TRF2056

LOW VOLTAGE 1.2 GHz FRACTIONAL N/INTEGER N SYNTHESIZER

SLWS111 NOVEMBER 2000

1

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

D

1.2-GHz Operation

D

Two Operating Modes:

Philips SA7025 Emulation Mode

Terminal-for-Terminal and Programming

Compatible

Extended Performance Mode (EPM)

D

Dual RF-IF Phase-Locked Loops

D

Fractional-N or Integer-N Operation

D

Programmable EPM Fractional

Modulus of 116

D

Normal, Speed-Up, and Fractional

Compensation Charge Pumps

D

Low-Power Consumption

description

The TRF2056 device is a low-voltage, low-power consumption 1.2-GHz fractional-N/integer-N frequency

synthesizer component for wireless applications. Fractional-N division and an integral speed-up charge pump

achieve rapid channel switching. Two operating modes are available: 1) SA7025 emulation mode in which the

device emulates the Philips SA7025 fractional-N synthesizer and 2) extended performance mode (EPM), which

provides additional features, including fractional accumulator modulos from 1 to 16 (compared to only 5 or 8

for the SA7025 synthesizer).

The TRF2056 device provides external loop filters and all functions necessary for voltage-controlled oscillator

(VCO) control in a dual phase-locked loop (PLL) frequency synthesizer system. A main channel is provided for

radio frequency (RF) channels and an auxiliary channel for intermediate frequency (IF) channels. The

current-output charge pumps directly drive passive resistance-capacitance (RC) filter networks to generate

VCO control voltages. Rapid main-channel frequency switching is achieved with a charge pump arrangement

that increases the current drive and alters the loop-filter frequency response during the speed-up mode portion

of the switching interval.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

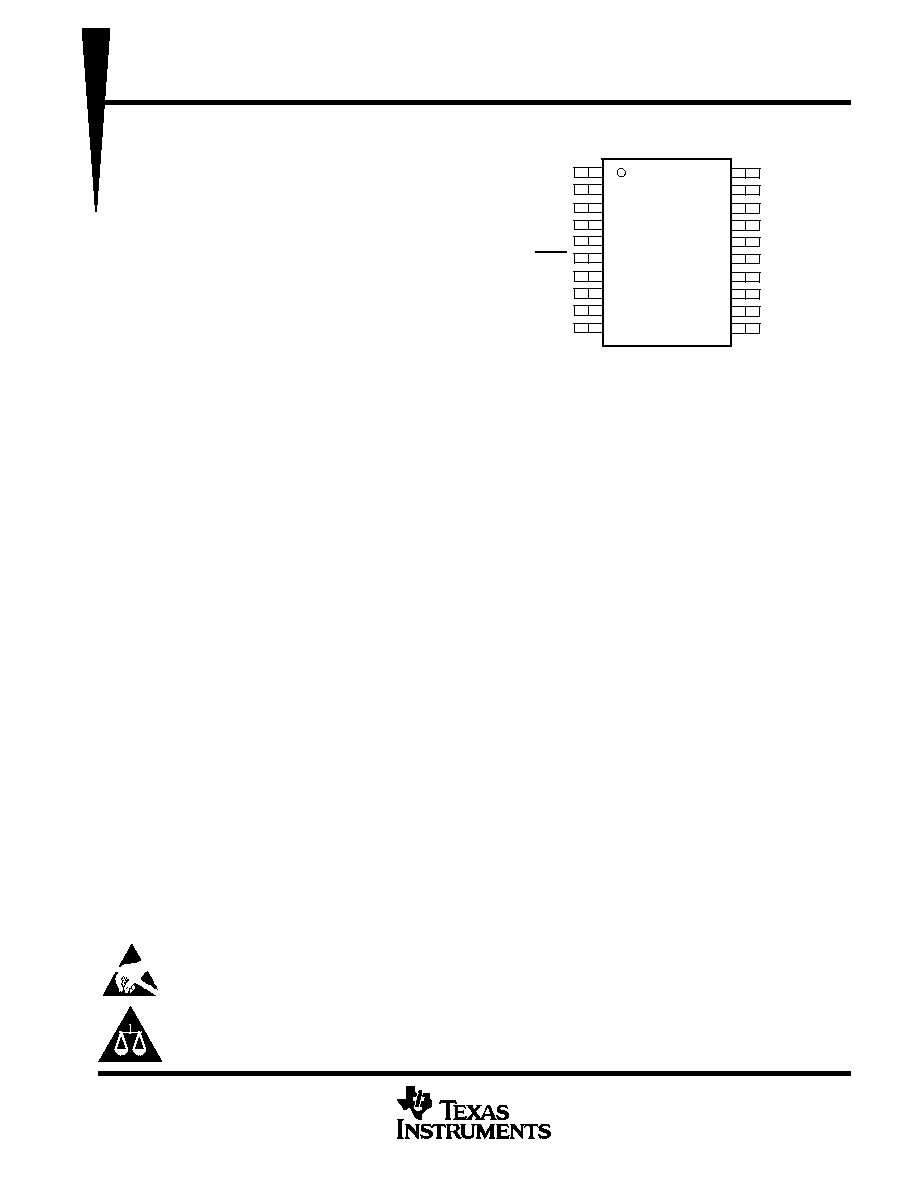

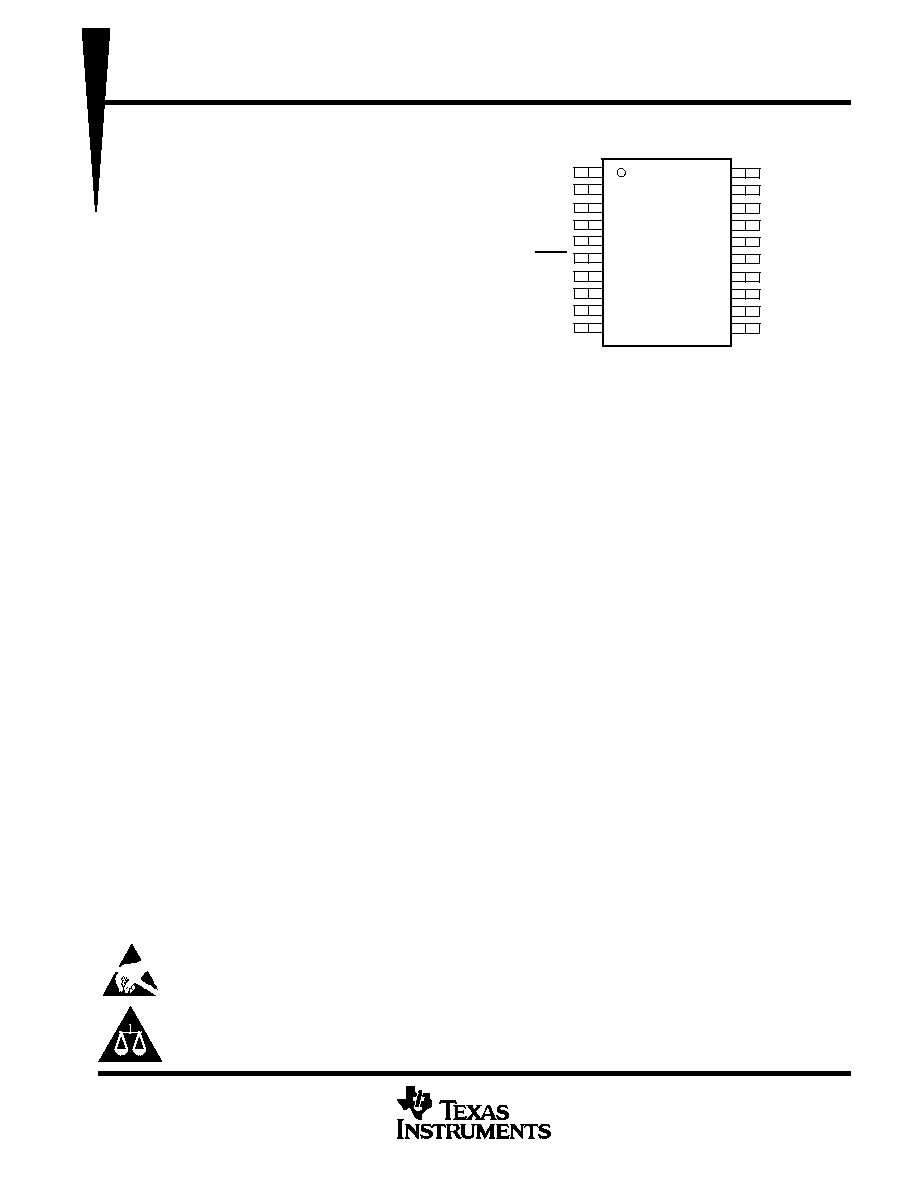

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

CLOCK

DATA

STROBE

V

SS

RFIN

RFIN

V

CCP

REFIN

RA

AUXIN

V

DD

TSETUP

LOCK/TEST

RF

RN

V

DDA

PHP

PHI

V

SSA

PHA

PW PACKAGE

(TOP VIEW)

Copyright

©

2000, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

TRF2056

LOW VOLTAGE 1.2 GHz FRACTIONAL N/INTEGER N SYNTHESIZER

SLWS111 NOVEMBER 2000

2

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

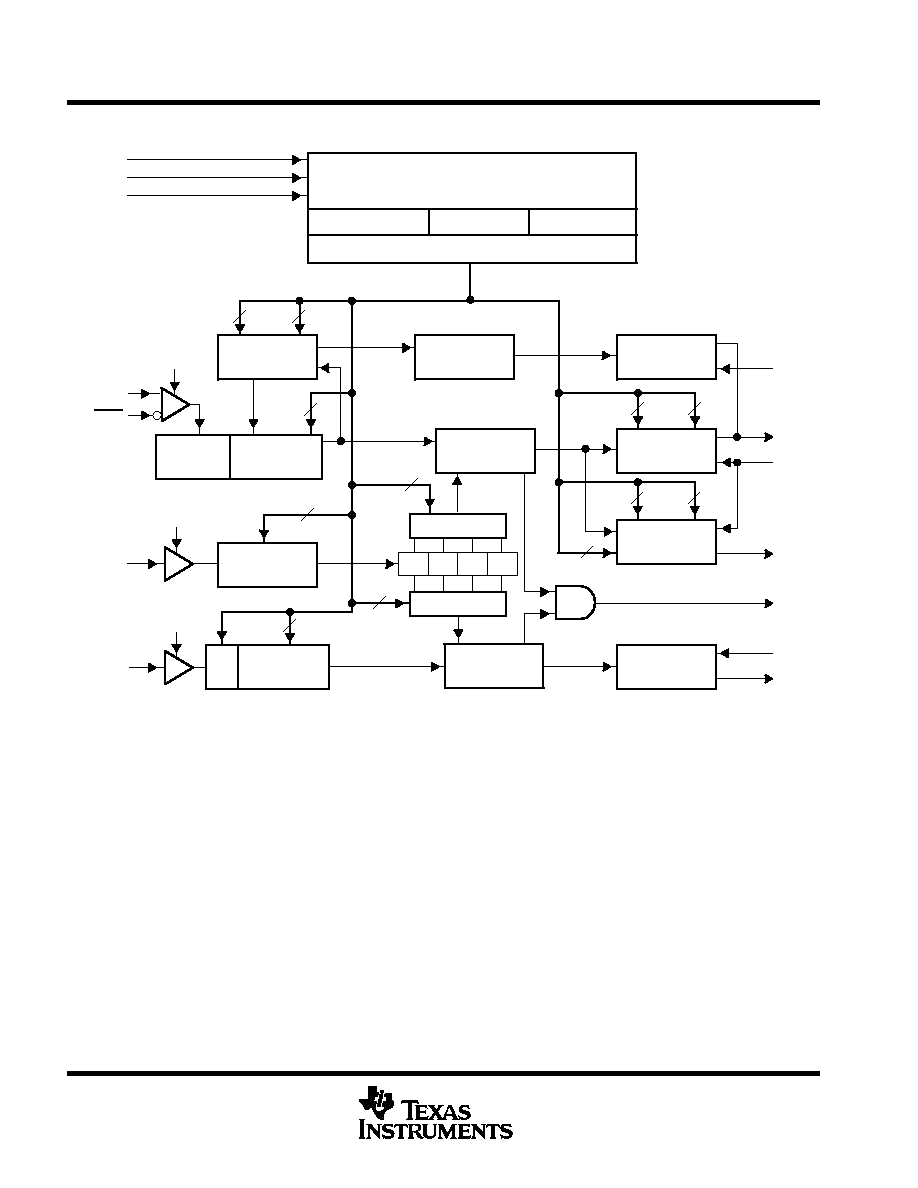

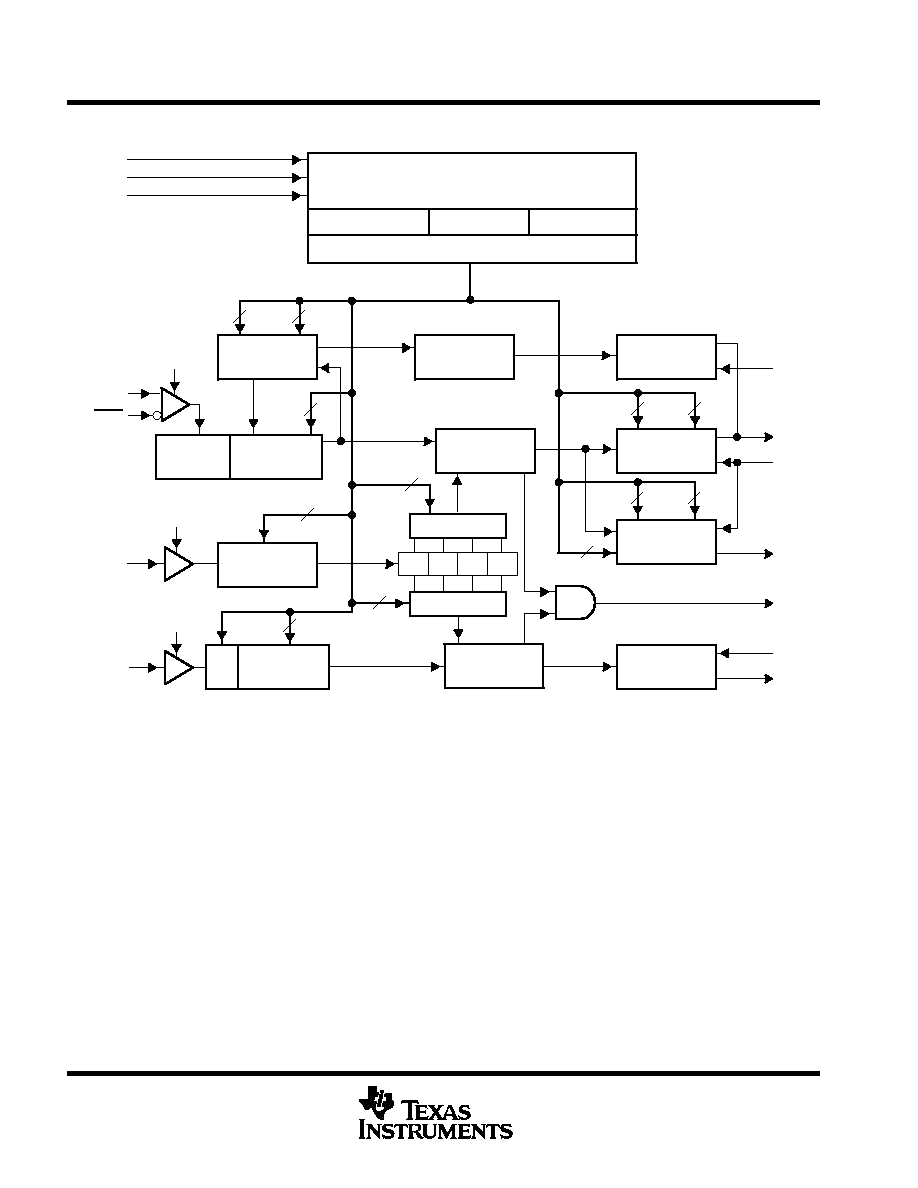

functional block diagram

Serial Control Shift Registers

Common Registers

EPM Registers SA7025 Registers

Conversion and Selection

CLOCK

STROBE

Fractional

Accumulator

FMOD

5

NF

4

Fractional

Compensation

Control Lines

Compensation

Charge Pump

Phase

Detector

Proportional

Charge Pump

Reference

Divider

Integral

Charge Pump

4

CK

18

N

12

NR

Phase

Detector

Auxiliary

Charge Pump

Auxiliary

Divider

4/1

12

NA

PA

REFIN

AUXIN

RF

RN

PHI

LOCK/

TEST

RA

PHA

Main Divider

(N/N+1)

RFIN

RFIN

32/33

Prescaler

CL

2

CN

8

PHP

CL

2

CN

8

1

2

4

8

Select

Select

2

SM

2

SA

3

1

5

6

8

10

17

14

16

13

18

9

11

DATA

2

Terminals 4, 7, 12, 15, and 20 are for supply voltage. Terminal 19 is for testing. These terminals are not shown.

Conversion and selection block provides emulation of SA7025 64/65/72 triple-modulus prescaler operation using the TRF2056 32/33

dual-modulus prescaler.

EM+EA

EM

EA

TRF2056

LOW VOLTAGE 1.2 GHz FRACTIONAL N/INTEGER N SYNTHESIZER

SLWS111 NOVEMBER 2000

3

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

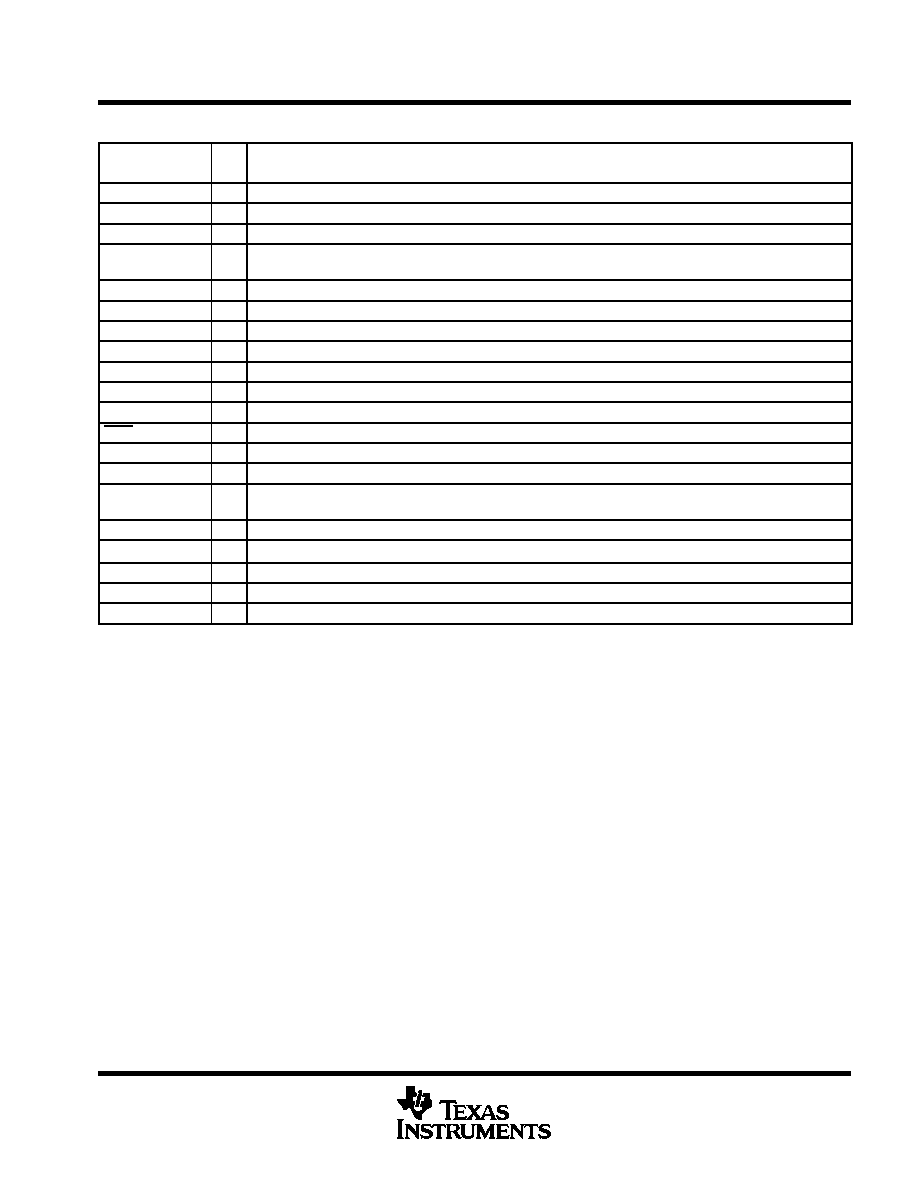

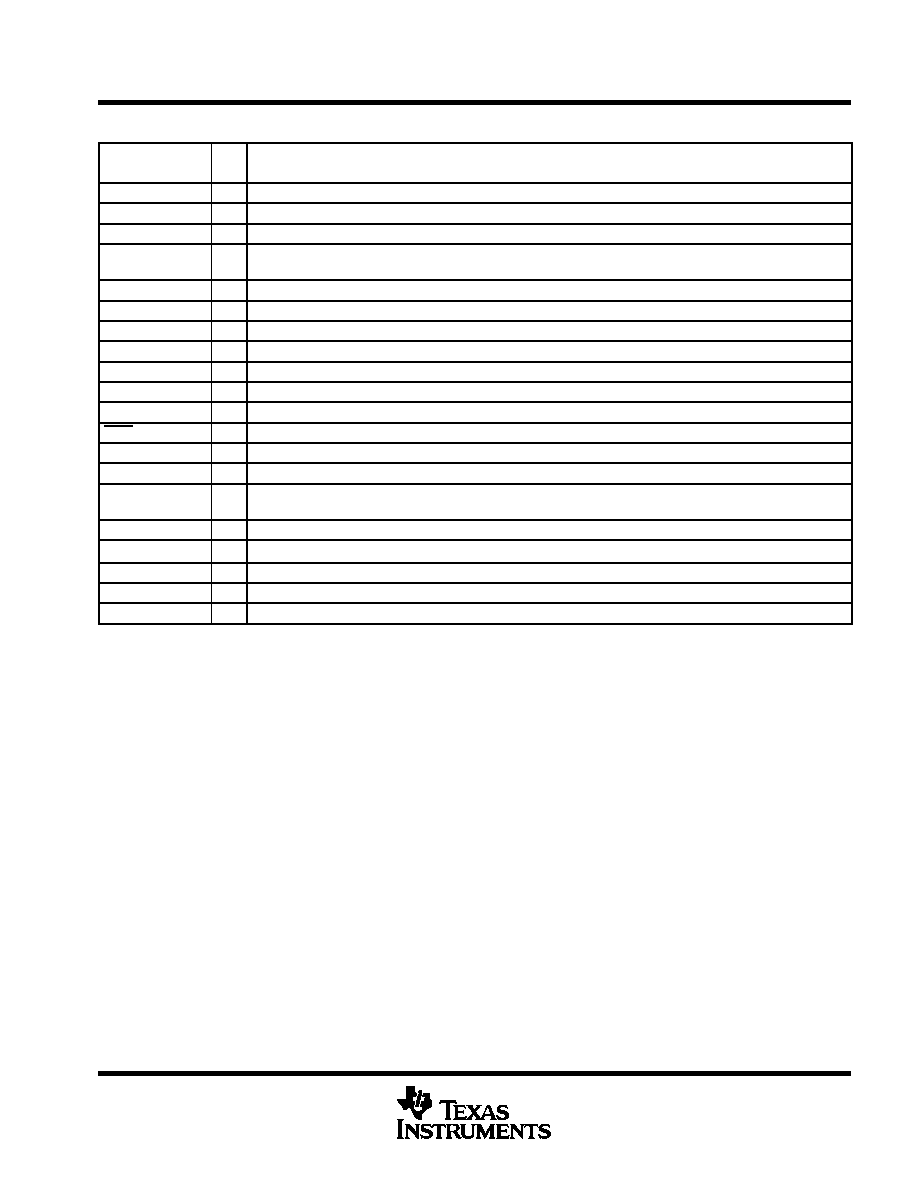

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

ĮĮĮĮ

ĮĮĮĮ

AUXIN

ĮĮĮ

ĮĮĮ

10

ĮĮ

ĮĮ

I

Auxiliary channel RF input

ĮĮĮĮ

ĮĮĮĮ

CLOCK

ĮĮĮ

ĮĮĮ

1

ĮĮ

ĮĮ

I

Serial interface clock signal

ĮĮĮĮ

ĮĮĮĮ

DATA

ĮĮĮ

ĮĮĮ

2

ĮĮ

ĮĮ

I

Serial interface data signal

ĮĮĮĮ

Į

ĮĮ

Į

ĮĮĮĮ

LOCK/

TEST

ĮĮĮ

ĮĮ

Į

ĮĮĮ

18

ĮĮ

ĮĮ

ĮĮ

O

Lock detector/test mode output

ĮĮĮĮ

ĮĮĮĮ

PHA

ĮĮĮ

ĮĮĮ

11

ĮĮ

ĮĮ

O

Auxiliary charge pump output

ĮĮĮĮ

PHI

ĮĮĮ

13

ĮĮ

O

Integral charge pump output

ĮĮĮĮ

ĮĮĮĮ

PHP

ĮĮĮ

ĮĮĮ

14

ĮĮ

ĮĮ

O

Proportional charge pump output

ĮĮĮĮ

ĮĮĮĮ

RA

ĮĮĮ

ĮĮĮ

9

ĮĮ

ĮĮ

I

Resistor to VSSA sets auxiliary charge pump reference current

ĮĮĮĮ

ĮĮĮĮ

REFIN

ĮĮĮ

ĮĮĮ

8

ĮĮ

ĮĮ

I

Reference frequency input signal

ĮĮĮĮ

ĮĮĮĮ

RF

ĮĮĮ

ĮĮĮ

17

ĮĮ

ĮĮ

I

Resistor to VSSA sets compensation charge pump reference current

ĮĮĮĮ

ĮĮĮĮ

RFIN

ĮĮĮ

ĮĮĮ

5

ĮĮ

ĮĮ

I

Prescaler positive RF input

ĮĮĮĮ

ĮĮĮĮ

RFIN

ĮĮĮ

ĮĮĮ

6

ĮĮ

ĮĮ

I

Prescaler negative RF input

ĮĮĮĮ

ĮĮĮĮ

RN

ĮĮĮ

ĮĮĮ

16

ĮĮ

ĮĮ

I

Resistor to VSSA sets proportional and integral charge pump reference current

ĮĮĮĮ

STROBE

ĮĮĮ

3

ĮĮ

I

Serial interface strobe signal

ĮĮĮĮ

Į

ĮĮ

Į

ĮĮĮĮ

TSETUP

ĮĮĮ

ĮĮ

Į

ĮĮĮ

19

ĮĮ

ĮĮ

ĮĮ

I

Test setup for terminal 18. For lock detect output, terminal 19 connects to VCC through a pullup resistor; for test mode

output, terminal 19 terminates to ground.

ĮĮĮĮ

ĮĮĮĮ

VCCP

ĮĮĮ

ĮĮĮ

7

ĮĮ

ĮĮ

Prescaler positive supply voltage

ĮĮĮĮ

ĮĮĮĮ

VDD

ĮĮĮ

ĮĮĮ

20

ĮĮ

ĮĮ

Digital supply voltage

ĮĮĮĮ

ĮĮĮĮ

VDDA

ĮĮĮ

ĮĮĮ

15

ĮĮ

ĮĮ

Analog supply voltage

ĮĮĮĮ

ĮĮĮĮ

VSS

ĮĮĮ

ĮĮĮ

4

ĮĮ

ĮĮ

Digital ground

ĮĮĮĮ

ĮĮĮĮ

VSSA

ĮĮĮ

ĮĮĮ

12

ĮĮ

ĮĮ

Analog ground

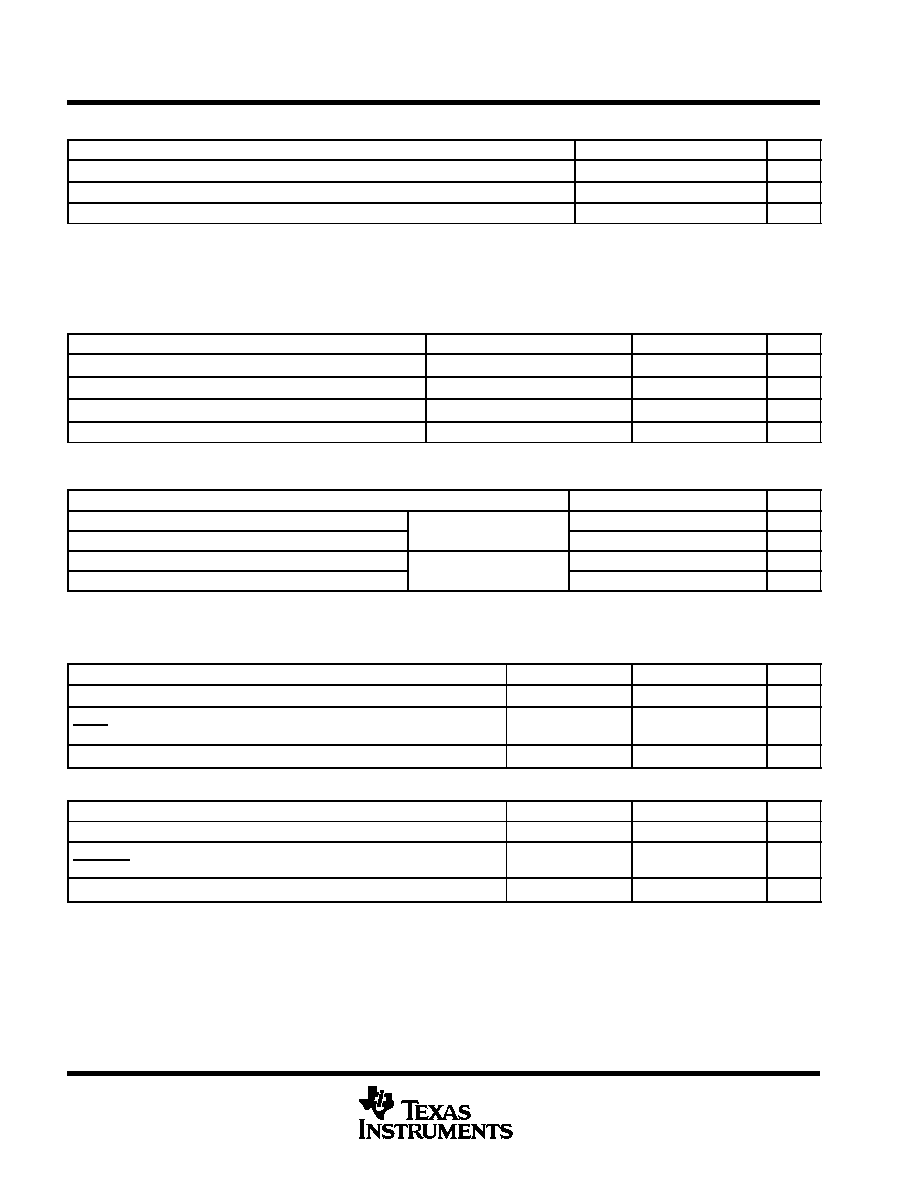

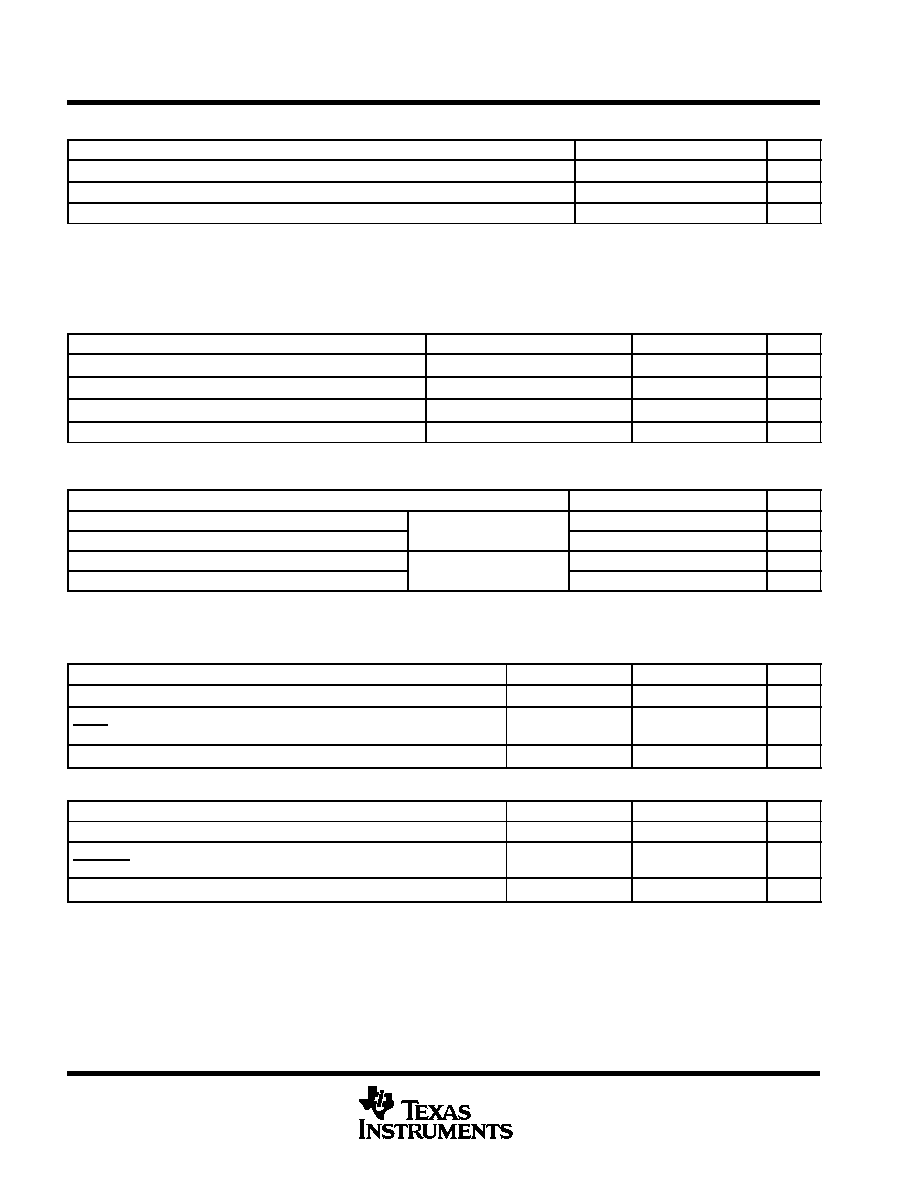

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

CCP,

V

DD

, V

DDA

(see Note 1)

0.6 V to 5.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, logic signals

0.6 V to 5.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating ambient temperature range, T

A

55

°

C to 85

°

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

65

°

C to 150

°

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under

recommended operating conditions is not implied.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage values are with respect to VSSA.

TRF2056

LOW VOLTAGE 1.2 GHz FRACTIONAL N/INTEGER N SYNTHESIZER

SLWS111 NOVEMBER 2000

4

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

recommended operating conditions

MIN

NOM

MAX

UNIT

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Supply voltage, VDDA

ĮĮĮĮ

ĮĮĮĮ

3.3

ĮĮĮ

ĮĮĮ

ĮĮĮĮĮ

ĮĮĮĮĮ

3.9

ĮĮĮ

ĮĮĮ

V

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Supply voltage, VCCP

,

VDD

ĮĮĮĮ

ĮĮĮĮ

2.9

ĮĮĮ

ĮĮĮ

3.3

ĮĮĮĮĮ

ĮĮĮĮĮ

3.9

ĮĮĮ

ĮĮĮ

V

Operating free-air temperature, TA

40

25

85

°

C

dc electrical characteristics V

DD

= V

DDA

= V

CCP

=

3.3 V, T

A

=25

_

C

internal registers: CN = 128, CL = 1, CK = 3, PA = 1

external components: RN = 18 k

, RF = 20 k

, RA = 100 k

(unless otherwise noted)

supply current: I = I

DD

+ I

CCP

+ I

DDA

PARAMETER

TEST CONDITIONS

ĮĮĮ

ĮĮĮ

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮĮ

ĮĮĮĮĮ

ISTANDBY

Total standby supply currents

EM = EA = 0 (see Note 2)

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

200

ĮĮĮ

ĮĮĮ

µ

A

ĮĮĮĮĮ

ĮĮĮĮĮ

IMAIN

Operational supply currents

EM = 1, EA = 0

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

7.0

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

mA

ĮĮĮĮĮ

ĮĮĮĮĮ

IAUX

Operational supply currents

EM = 0, EA = 1

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

1.5

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

mA

ĮĮĮĮĮ

ĮĮĮĮĮ

ITOTAL

Operational supply currents

ĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮ

EM = EA = 1

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

7.5

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

mA

NOTE 2: VRN = VRA = VRF = VDDA

digital interface

PARAMETER

MIN

TYP

MAX

UNIT

VIH

High-level input voltage

DATA CLOCK STROBE

0.7 VDD

VDD + 0.3

V

VIL

Low-level input voltage

DATA, CLOCK, STROBE

0.3

0.3 VDD

V

IIH

High-level input current

DATA CLOCK STROBE

10

µ

A

IIL

Low-level input current

DATA, CLOCK, STROBE

10

µ

A

charge pump currents (see Figure 1)

auxiliary charge pump

PARAMETER

ĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮ

TEST CONDITIONS

ĮĮĮ

ĮĮĮ

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮĮ

ĮĮĮĮĮ

|IPHA|

Output current PHA

ĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮ

VPHA = 0.5 VDDA

ĮĮĮ

ĮĮĮ

200

ĮĮĮ

ĮĮĮ

250

ĮĮĮ

ĮĮĮ

300

ĮĮĮ

ĮĮĮ

µ

A

ĮĮĮĮĮ

Į

ĮĮĮ

Į

ĮĮĮĮĮ

IPHA

|IPHA|

Relative output current variation PHA (see Figure 1)

ĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮ

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮ

Į

Į

Į

ĮĮĮ

2%

ĮĮĮ

Į

Į

Į

ĮĮĮ

10%

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮĮĮ

ĮĮĮĮĮ

IPHA

Output current matching PHA (see Figure 1)

ĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮ

VPHA = 0.5 VDDA

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

±

50

ĮĮĮ

ĮĮĮ

µ

A

proportional charge pump

,

normal mode, V

RF

= V

DDA

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

PARAMETER

ĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮ

TEST CONDITIONS

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮĮ

ĮĮĮĮĮ

|IPHP-NM|

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Output current PHP

ĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮ

VPHP = 0.5 VDDA

400

ĮĮĮ

ĮĮĮ

500

ĮĮĮ

ĮĮĮ

600

ĮĮĮ

ĮĮĮ

µ

A

ĮĮĮĮĮ

Į

ĮĮĮ

Į

ĮĮĮĮĮ

IPHP-NM

|IPHP-NM|

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Relative output current variation PHP (see Figure 1)

ĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮ

ĮĮĮ

Į

Į

Į

ĮĮĮ

2%

ĮĮĮ

Į

Į

Į

ĮĮĮ

10%

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮĮĮ

ĮĮĮĮĮ

IPHP-NM

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Output current matching PHP (see Figure 1)

ĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮ

VPHP = 0.5 VDDA

ĮĮĮ

ĮĮĮ

±

50

ĮĮĮ

ĮĮĮ

µ

A

TRF2056

LOW VOLTAGE 1.2 GHz FRACTIONAL N/INTEGER N SYNTHESIZER

SLWS111 NOVEMBER 2000

5

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

charge pump currents (see Figure 1) (continued)

proportional charge pump

,

speed-up mode, V

RF

= V

DDA

(see

speed-up mode operation)

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

PARAMETER

TEST CONDITIONS

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮĮ

|IPHP-SM|

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Output current PHP

VPHP = 0.5 VDDA

2

ĮĮĮ

2.5

ĮĮĮ

3

ĮĮĮ

mA

ĮĮĮĮĮ

Į

ĮĮĮ

Į

ĮĮĮĮĮ

IPHP-SM

|IPHP-SM|

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Relative output current variation PHP (see Figure 1)

ĮĮĮ

Į

Į

Į

ĮĮĮ

2%

ĮĮĮ

Į

Į

Į

ĮĮĮ

10%

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮĮĮ

ĮĮĮĮĮ

IPHP-SM

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Output current matching PHP (see Figure 1)

VPHP = 0.5 VDDA

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

±

300

ĮĮĮ

ĮĮĮ

µ

A

integral charge pump, speed-up mode, V

RF

= V

DDA

(see

speed-up mode operation)

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

PARAMETER

TEST CONDITIONS

ĮĮĮ

ĮĮĮ

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮĮ

ĮĮĮĮĮ

|IPHI-SM|

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Output current PHI

VPHI = 0.5 VDDA

ĮĮĮ

ĮĮĮ

4.8

ĮĮĮ

ĮĮĮ

6

ĮĮĮ

ĮĮĮ

7.2

ĮĮĮ

ĮĮĮ

mA

ĮĮĮĮĮ

Į

ĮĮĮ

Į

ĮĮĮĮĮ

IPHI-SM

|IPHI-SM|

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Į

ĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮĮ

Relative output current variation PHI (see Figure 1)

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮ

Į

Į

Į

ĮĮĮ

2%

ĮĮĮ

Į

Į

Į

ĮĮĮ

8%

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮĮĮ

ĮĮĮĮĮ

IPHI-SM

Output current matching PHI (see Figure 1)

VPHI = 0.5 VDDA

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

±

600

ĮĮĮ

ĮĮĮ

µ

A

fractional compensation proportional charge pump, normal mode, V

RN

= V

DDA

PARAMETER

TEST CONDITIONS

ĮĮĮ

ĮĮĮ

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮĮ

Į

ĮĮĮ

Į

ĮĮĮĮĮ

|IPHP-F-NM|

Output current PHP vs fractional numerator

(see Note 3)

VPHP = 0.5 VDDA, FNUM = 1

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮ

Į

Į

Į

ĮĮĮ

1.25

ĮĮĮ

Į

Į

Į

ĮĮĮ

ĮĮĮ

Į

Į

Į

ĮĮĮ

µ

A

NOTE: 3. Fractional compensation current is proportional to the numerator content of the fractional accumulator (FNUM).

charge pump leakage currents,

V

RN

= V

RA

= V

RF

= V

DDA

PARAMETER

ĮĮĮĮĮĮ

ĮĮĮĮĮĮ

TEST CONDITIONS

ĮĮĮ

ĮĮĮ

MIN

ĮĮĮ

ĮĮĮ

TYP

ĮĮĮ

ĮĮĮ

MAX

ĮĮĮ

ĮĮĮ

UNIT

ĮĮĮĮ

ĮĮĮĮ

IPHP

Output current PHP

ĮĮĮĮĮĮ

ĮĮĮĮĮĮ

VPHP = 0.5 VDDA

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

±

10

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮĮ

IPHI

Output current PHI

ĮĮĮĮĮĮ

VPHI = 0.5 VDDA

ĮĮĮ

ĮĮĮ

±

10

ĮĮĮ

ĮĮĮ

nA

ĮĮĮĮ

ĮĮĮĮ

IPHA

Output current PHA

ĮĮĮĮĮĮ

ĮĮĮĮĮĮ

VPHA = 0.5 VDDA

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

±

10

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ac electrical characteristics, V

DD

= V

CCP

= 2.9 V, V

DDA

= 3.9 V, T

A

= 25

°

C (unless otherwise noted)

main divider

PARAMETER

TEST CONDITIONS

ĮĮĮ

MIN

ĮĮĮ

TYP

ĮĮĮ

MAX

ĮĮĮ

UNIT

ĮĮĮĮ

ĮĮĮĮ

fRFIN

RF input frequency

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

1.2

ĮĮĮ

ĮĮĮ

GHz

ĮĮĮĮ

ĮĮĮĮ

VID_RFIN

Differential RF input power

50-

W

single-ended characteristic impedance; ac-coupled

ĮĮĮ

ĮĮĮ

20

ĮĮĮ

ĮĮĮ

ĮĮĮ

ĮĮĮ

0

ĮĮĮ

ĮĮĮ

dBm