TMS320C80

DIGITAL SIGNAL PROCESSOR

SPRS023B JULY 1994 REVISED OCTOBER 1997

1

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

D

Single-Chip Parallel Multiple

Instruction / Multiple Data (MIMD) DSP

D

More Than Two Billion RISC-Equivalent

Operations per Second

D

Master Processor (MP)

32-Bit Reduced Instruction Set

Computing (RISC) Processor

IEEE-754 Floating-Point Capability

4K-Byte Instruction Cache

4K-Byte Data Cache

D

Four Parallel Processors (PP)

32-Bit Advanced DSPs

64-Bit Opcode Provides Many Parallel

Operations per Cycle

2K-Byte Instruction Cache and 8K-Byte

Data RAM per PP

D

Transfer Controller ( TC)

64-Bit Data Transfers

Up to 480M-Byte / s Transfer Rate

32-Bit Addressing

Direct DRAM / VRAM Interface With

Dynamic Bus Sizing

Intelligent Queuing and Cycle

Prioritization

D

Video Controller ( VC)

Provides Video Timing and VRAM

Control

Dual-Frame Timers for Two Simultaneous

Image-Capture and / or Display Systems

D

Big- or Little-Endian Operation

D

50K-Byte On-Chip RAM

D

4G-Byte Address Space

D

16.6-ns Cycle Time

D

3.3-V Operation

D

IEEE Standard 1149.1

Test Access Port

(JTAG)

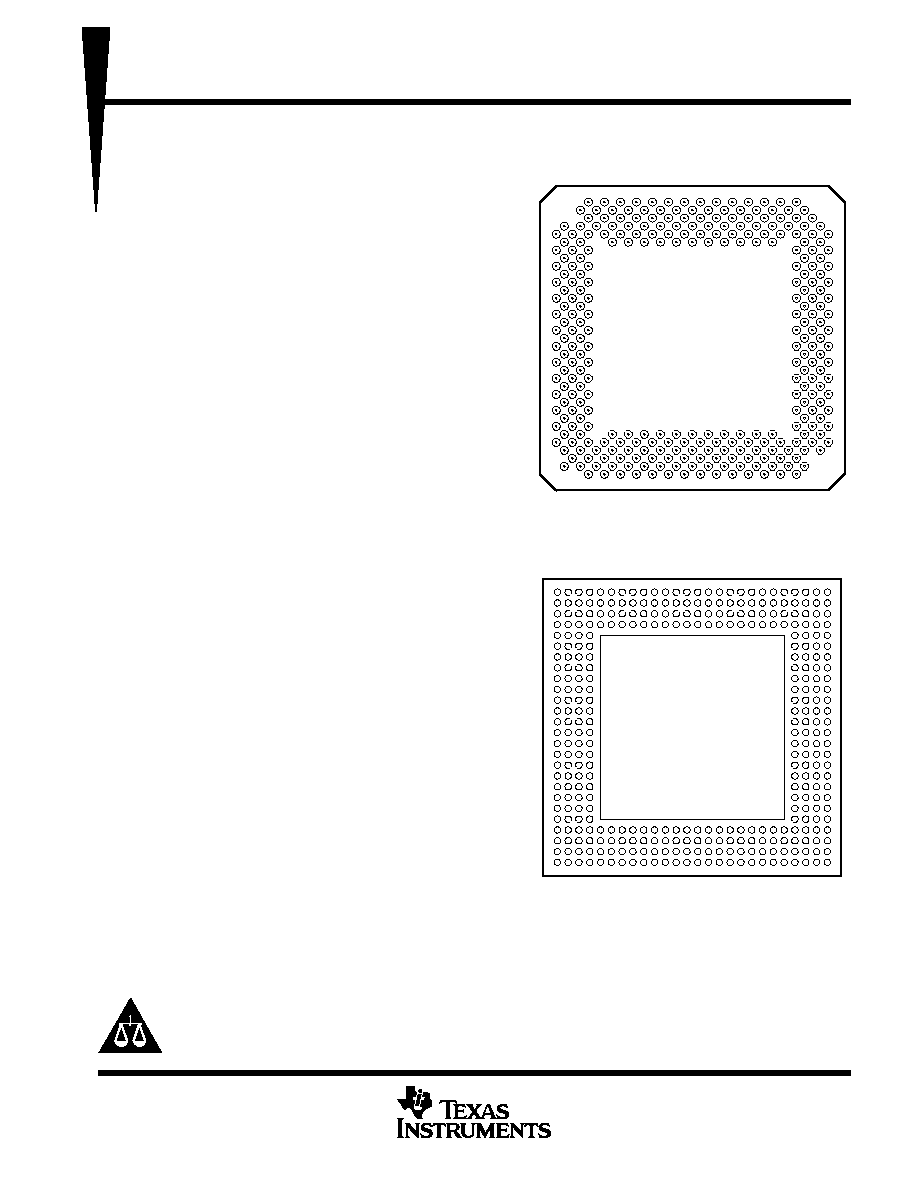

2

9

8

7

6

5

4

3

1

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

AR

AP

AN

AM

AL

AK

AJ

AH

AG

AF

AE

AD

AC

AB

AA

GF PACKAGE

( BOTTOM VIEW )

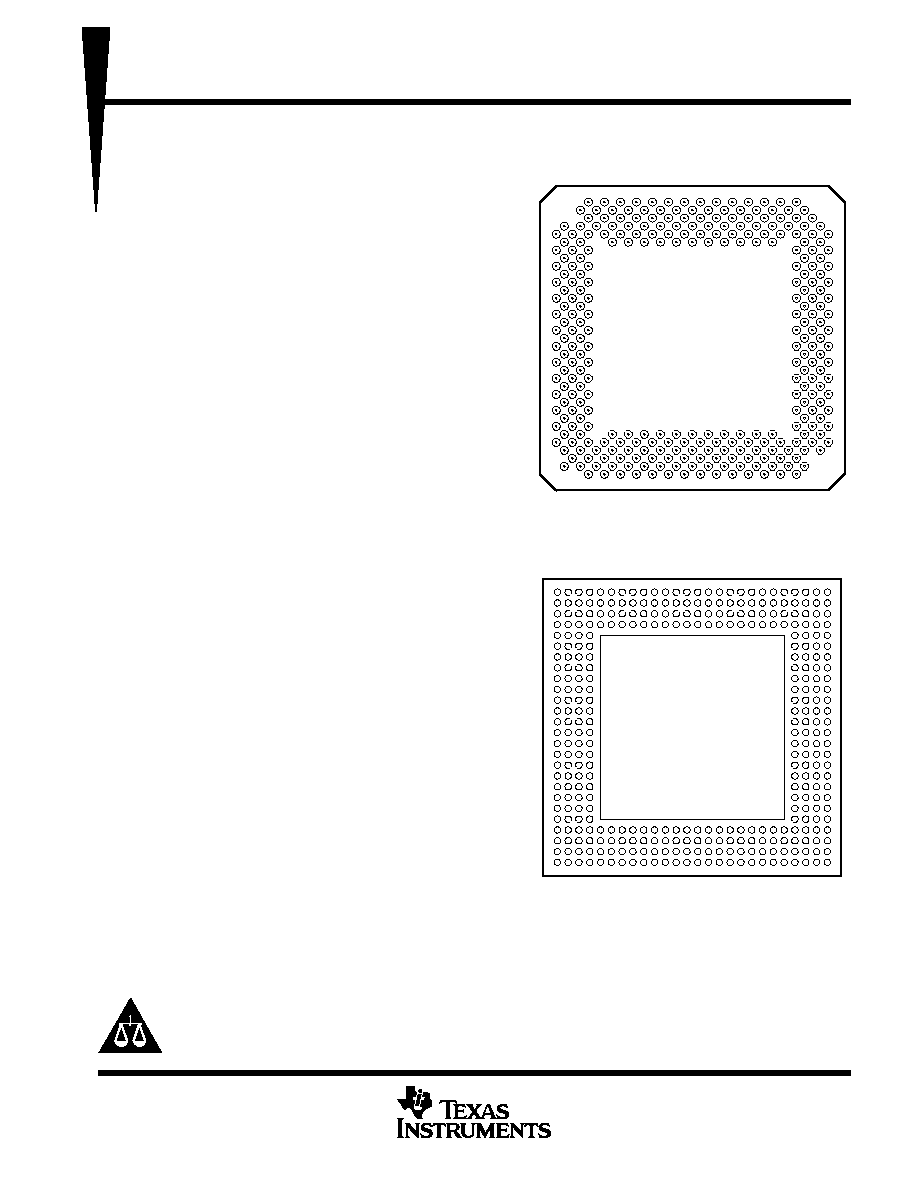

A

1

3

2

F

E

D

C

K

J

H

G

B

P

N

M

W

V

U

T

R

AC

AB

AA

Y

AF

AE

AD

L

5

6

4

9

8

7

11

13

12

15

16

14

10

19

18

21

23

22

20

25

26

24

17

GGP PACKAGE

( BOTTOM VIEW )

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright

©

1997, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IEEE Standard 1149.11990, IEEE Standard Test Access Port and Boundary-Scan Architecture

TMS320C80

DIGITAL SIGNAL PROCESSOR

SPRS023B JULY 1994 REVISED OCTOBER 1997

2

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

description

The TMS320C80 is a single chip, MIMD parallel processor capable of performing over two billion operations

per second. It consists of a 32-bit RISC master processor with a 120-MFLOP IEEE floating-point unit, four 32-bit

parallel processing digital signal processors (DSPs), a transfer controller with up to 480M-byte/s off-chip

transfer rate, and a video controller. All the processors are coupled tightly through an on-chip crossbar that

provides shared access to on-chip RAM. This performance and programmability make the 'C80 ideally suited

for video, imaging, and high-speed telecommunications applications.