TM893CBK32, TM893CBK32S

8388608 BY 32-BIT

DYNAMIC RAM MODULE

SMMS652A FEBRUARY 1995 REVISED JUNE 1995

1

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

D

Organization

TM893CBK32 . . . 8 388 608

×

32 Bit

D

Single 5-V Power Supply (

±

10% Tolerance)

D

72-Pin, Leadless Single In-Line Memory

Module ( SIMM ) for Use With Sockets

D

TM893CBK32 Utilizes Sixteen 16-Megabit

Dynamic RAMs in Plastic Small-Outline

J-Lead ( SOJ ) Packages

D

Long Refresh Period

32 ms (2048 Cycles)

D

All Inputs, Outputs, Clocks Fully TTL

Compatible

D

3-State Output

D

Common CAS Control for Eight Common

Data-In and Data-Out Lines in Four Blocks

D

Enhanced Page-Mode Operation With

CAS-Before-RAS ( CBR ), RAS-Only, and

Hidden Refresh

D

Presence Detect

D

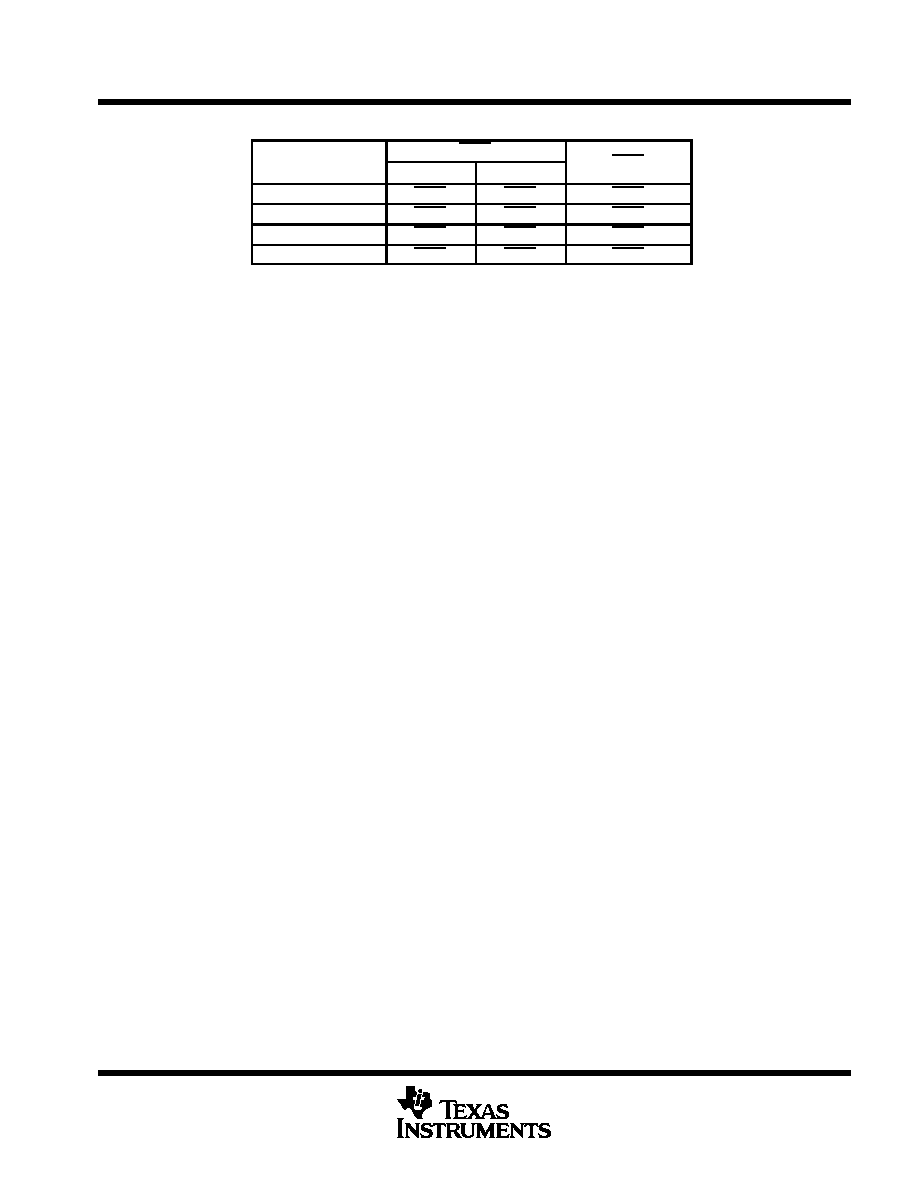

Performance Ranges:

ACCESS

ACCESS ACCESS READ

TIME

TIME

TIME

OR

tRAC

tAA

tCAC

WRITE

CYCLE

(MAX) (MAX)

(MAX)

(MIN)

'893CBK32-60

60 ns

30 ns

15 ns

110 ns

'893CBK32-70

70 ns

35 ns

18 ns

130 ns

'893CBK32-80

80 ns

40 ns

20 ns

150 ns

D

Low Power Dissipation

D

Operating Free-Air-Temperature Range

0

°

C to 70

°

C

D

Gold-Tabbed Versions Available:

TM893CBK32

D

Tin-Lead (Solder) Tabbed Versions

Available:

TM893CBK32S

description

The TM893CBK32 is a 32-megabyte, dynamic random-access memory organized as four times 8 388 608

×

8

bits in a 72-pin, leadless single in-line memory module ( SIMM ). The SIMM is composed of 16 TMS417400DJ,

4 194 304

×

4-bit dynamic RAMs, each in 24 / 26-lead plastic small-outline J-lead ( SOJ ) packages mounted on

a substrate with decoupling capacitors. The TMS417400DJ is described in the TMS417400 data sheet. The

TM893CBK32 SIMM is available in the double-sided BK leadless module for use with sockets.

operation

The TM893CBK32 operates as sixteen TMS417400DJs connected as shown in the functional block diagram

and Table 1. The common I / O feature dictates the use of early-write cycles to prevent contention on D and Q.

refresh

The refresh period is extended to 32 ms, and during this period each of the 2048 rows must be strobed with RAS

to retain data. To conserve power, CAS can remain high during the refresh sequence.

power up

To achieve proper operation, an initial pause of 200

µ

s followed by a minimum of eight initialization cycles is

required after full V

CC

level is achieved. These eight initialization cycles must include at least one refresh

( RAS-only or CBR ) cycle.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright

©

1995, Texas Instruments Incorporated

Part numbers in this data sheet are for the gold-tabbed version; the information applies to both gold-tabbed and solder-tabbed versions.

TM893CBK32, TM893CBK32S

8388608 BY 32-BIT

DYNAMIC RAM MODULE

SMMS652A FEBRUARY 1995 REVISED JUNE 1995

2

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

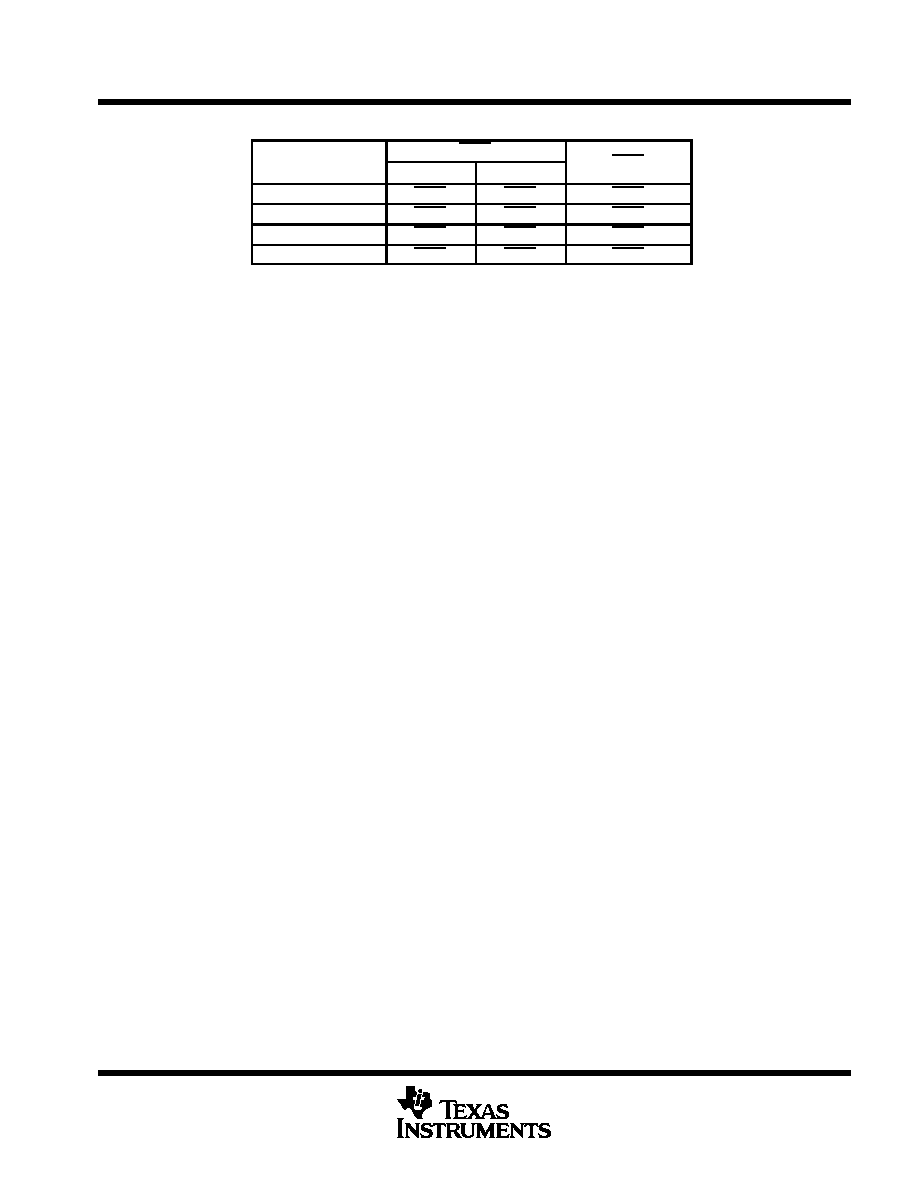

PRESENCE DETECT

SIGNAL (PIN)

PD1

(67)

PD2

(68)

PD3

(69)

PD4

(70)

80 ns

NC

VSS

NC

VSS

TM893CBK32

70 ns

NC

VSS

VSS

NC

60 ns

NC

VSS

NC

NC

TM893CBK32

( SIDE VIEW )

NC

NC

CAS0

CAS2

CAS3

CAS1

RAS0

RAS1

NC

W

NC

DQ8

DQ24

DQ9

DQ25

DQ10

DQ26

DQ11

DQ27

DQ12

DQ28

VCC

DQ29

DQ13

DQ30

DQ14

DQ31

DQ15

NC

PD1

PD2

PD3

PD4

NC

VSS

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

VSS

DQ0

DQ16

DQ1

DQ17

DQ2

DQ18

DQ3

DQ19

VCC

NC

A0

A1

A2

A3

A4

A5

A6

A10

DQ4

DQ20

DQ5

DQ21

DQ6

DQ22

DQ7

DQ23

A7

NC

VCC

A8

A9

RAS3

RAS2

NC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

BK SINGLE-IN-LINE PACKAGE

( TOP VIEW )

PIN NOMENCLATURE

A0 A10

Address Inputs

CAS0 CAS3

Column-Address Strobe

DQ0 DQ31

Data In/Data Out

NC

No Connection

PD1 PD4

Presence Detects

RAS0 RAS3

Row-Address Strobe

VCC

5-V Supply

VSS

Ground

W

Write Enable

VSS

TM893CBK32, TM893CBK32S

8388608 BY 32-BIT

DYNAMIC RAM MODULE

SMMS652A FEBRUARY 1995 REVISED JUNE 1995

3

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

Table 1. Connection Table

DATA BLOCK

RASx

CASx

DATA BLOCK

SIDE 1

SIDE 2

CASx

DQ0 DQ7

RAS0

RAS1

CAS0

DQ8 DQ15

RAS0

RAS1

CAS1

DQ16 DQ23

RAS2

RAS3

CAS2

DQ24 DQ31

RAS2

RAS3

CAS3

single in-line memory module and components

PC substrate: 1,27

±

0,1 mm (0.05 inch) nominal thickness; 0.005 inch/inch maximum warpage

Bypass capacitors: Multilayer ceramic

Contact area for TM893CBK32: Nickel plate and gold plate over copper

Contact area for TM893CBK32S: Nickel plate and tin-lead over copper

TM893CBK32, TM893CBK32S

8

388

608 BY

32-BIT

DYNAMIC RAM MODULE

SMMS652A

FEBRUAR

Y

1995 REVISED JUNE 1995

T

emp

l

ate

R

e

l

ease

D

ate:

7

11

94

4

POST

OFFICE BOX 1443 HOUST

ON,

TEXAS

772511443

·

functional block diagram (side 1 )

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

A0 A10

DQ0

DQ3

11

11

11

11

11

11

11

11

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

11

DQ8

DQ11

DQ16

DQ19

DQ24

DQ27

DQ4

DQ7

DQ12

DQ15

DQ20

DQ23

DQ28

DQ31

W

RAS0

CAS0

CAS1

CAS2

CAS3

RAS2

functional block diagram (side 2)

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

A0 A10

DQ0

DQ3

11

11

11

11

11

11

11

11

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

4 M

×

4

A0 A10

RAS

W

CAS

OE

DQ1

DQ4

11

DQ8

DQ11

DQ16

DQ19

DQ24

DQ27

DQ4

DQ7

DQ12

DQ15

DQ20

DQ23

DQ28

DQ31

W

RAS1

CAS0

CAS1

CAS2

CAS3

RAS3

TM893CBK32, TM893CBK32S

8388608 BY 32-BIT

DYNAMIC RAM MODULE

SMMS652A FEBRUARY 1995 REVISED JUNE 1995

5

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Voltage range on V

CC

(see Note 1)

1 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range on any pin (see Note 1)

1 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Short-circuit output current

50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power dissipation (TM893CBK32)

16 W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

0

°

C to 70

°

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

55

°

C to 125

°

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS.

recommended operating conditions

MIN

NOM

MAX

UNIT

VCC

Supply voltage

4.5

5

5.5

V

VIH

High-level input voltage

2.4

6.5

V

VIL

Low-level input voltage (see Note 2)

1

0.8

V

TA

Operating free-air temperature

0

70

°

C

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used for logic-voltage levels only.

electrical characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted)

PARAMETER

TEST CONDITIONS

'893BBK32-60

'893BBK32-70

'893BBK32-80

UNIT

PARAMETER

TEST CONDITIONS

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

VOH High-level output voltage

IOH = 5 mA

2.4

2.4

2.4

V

VOL

Low-level output voltage

IOL = 4.2 mA

0.4

0.4

0.4

V

II

Input current (leakage)

VCC = 5.5 V,

VI = 0 V to 6.5 V,

All others = 0 V to VCC

±

20

±

20

±

20

µ

A

IO

Output current (leakage)

VCC = 5.5 V,

VO = 0 V to VCC,

CAS high

±

20

±

20

±

20

µ

A

ICC1

Read or write cycle current

(see Note 3)

VCC = 5.5 V,

Minimum cycle

896

816

736

mA

ICC2 Standby current

VIH = 2.4 V (TTL),

After 1 memory cycle,

RAS and CAS high

32

32

32

mA

ICC2 Standby current

VIH = VCC 0.2 V (CMOS),

After 1 memory cycle,

RAS and CAS high

16

16

16

mA

ICC3

Average refresh current

(RAS only or CBR)

(see Note 3)

VCC = 5.5 V,

Minimum cycle,

RAS cycling,

CAS high (RAS only);

RAS low after CAS low (CBR)

1760

1600

1440

mA

ICC4

Average page current

(see Note 4)

VCC = 5.5 V,

tPC = Minimum,

RAS low,

CAS cycling

576

496

416

mA

NOTES:

3. Measured with a maximum of one address change while RAS = VIL

4. Measured with a maximum of one address change while CAS = VIH