TM2SN64EPN 2097152 BY 64-BIT

TM4SN64EPN 4194304 BY 64-BIT

SYNCHRONOUS DYNAMIC RAM MODULES

SMMS696 AUGUST 1997

1

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

D

Organization:

TM2SN64EPN . . . 2 097 152 x 64 Bits

TM4SN64EPN . . . 4 194 304 x 64 Bits

D

Single 3.3-V Power Supply

(

±

10% Tolerance)

D

Designed for 66-MHz 4-Clock Systems

D

JEDEC 168-Pin Dual-In-Line Memory

Module (DIMM) Without Buffer for Use With

Socket

D

TM2SN64EPN -- Uses Eight 16M-Bit

Synchronous Dynamic RAMs (SDRAMs)

(2M

×

8-Bit) in Plastic Thin Small-Outline

Packages (TSOPs)

D

TM4SN64EPN -- Uses Sixteen 16M-Bit

SDRAMs (2M

×

8-Bit) in Plastic TSOPs

D

Byte-Read/Write Capability

D

Performance Ranges:

D

High-Speed, Low-Noise Low-Voltage TTL

(LVTTL) Interface

D

Read Latencies 2 and 3 Supported

D

Support Burst-Interleave and

Burst-Interrupt Operations

D

Burst Length Programmable to 1, 2, 4,

and 8

D

Two Banks for On-Chip Interleaving

(Gapless Access)

D

Ambient Temperature Range

0

°

C to 70

°

C

D

Gold-Plated Contacts

D

Pipeline Architecture

D

Serial Presence-Detect (SPD) Using

EEPROM

SYNCHRONOUS

CLOCK CYCLE

TIME

ACCESS TIME

CLOCK TO

OUTPUT

REFRESH

INTERVAL

tCK3

(CL = 3)

tCK2

(CL = 2)

tCK3

(CL = 3)

tCK2

(CL = 2)

'xSN64EPN-10

10 ns

15 ns

7.5 ns

8 ns

64 ms

'xSN64EPN-12

12 ns

15 ns

8 ns

9 ns

64 ms

CL = CAS latency

description

The TM2SN64EPN is a 16M-byte, 168-pin dual-in-line memory module (DIMM). The DIMM is composed of

eight TMS626812ADGE, 2 097 152 x 8-bit SDRAMs, each in a 400-mil, 44-pin plastic thin small-outline package

(TSOP) mounted on a substrate with decoupling capacitors. See the TMS626812A data sheet (literature

number SMOS691).

The TM4SN64EPN is a 32M-byte, 168-pin DIMM. The DIMM is composed of sixteen TMS626812ADGE,

2 097 152 x 8-bit SDRAMs, each in a 400-mil, 44-pin plastic TSOP mounted on a substrate with decoupling

capacitors. See the TMS626812A data sheet (literature number SMOS691).

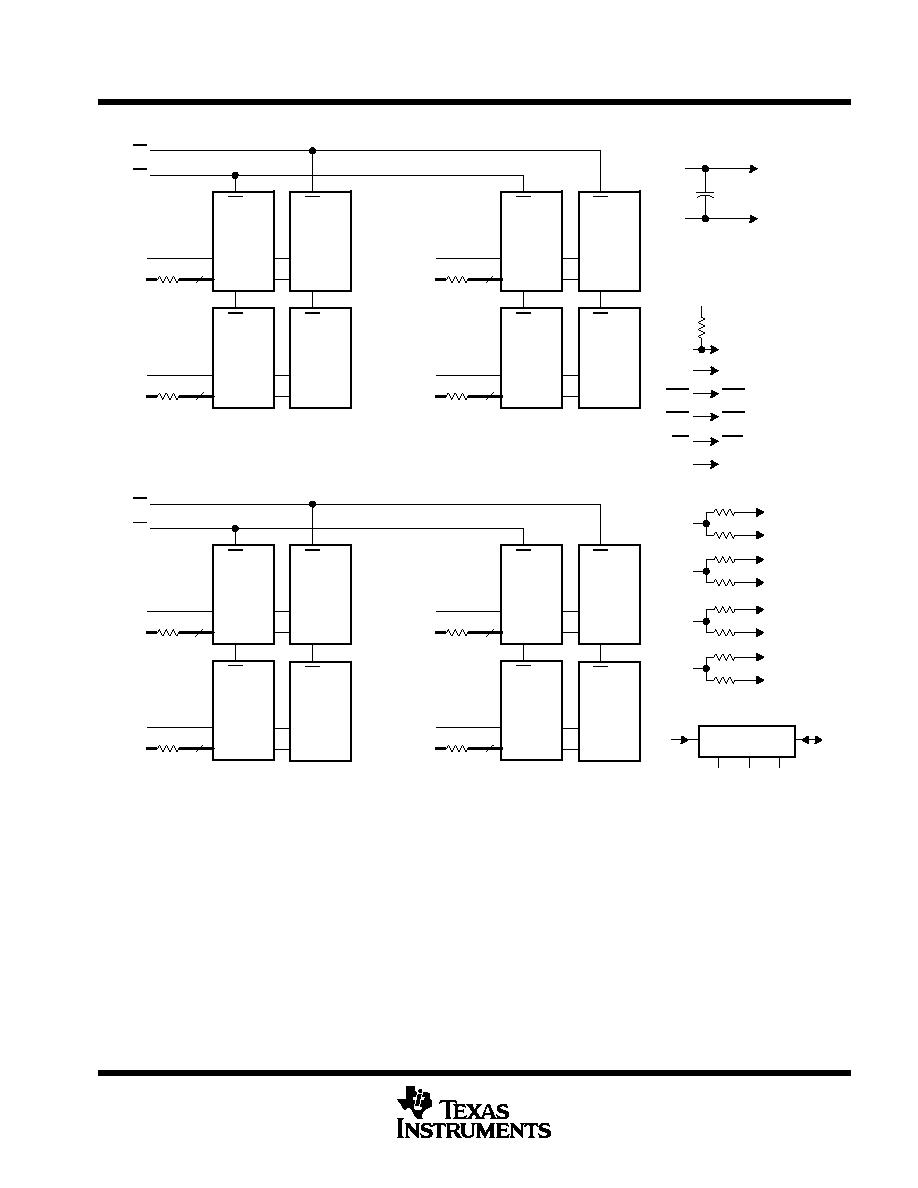

operation

The TM2SN64EPN operates as eight TMS626812ADGE devices that are connected as shown in the

TM2SN64EPN functional block diagram. The TM4SN64EPN operates as sixteen TMS626812ADGE devices

connected as shown in the TM4SN64EPN functional block diagram.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW

Copyright

©

1997, Texas Instruments Incorporated

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

TM2SN64EPN 2097152 BY 64-BIT

TM4SN64EPN 4194304 BY 64-BIT

SYNCHRONOUS DYNAMIC RAM MODULES

SMMS696 AUGUST 1997

2

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

DUAL-IN-LINE MEMORY MODULE

( TOP VIEW )

TM4SN64EPN

( SIDE VIEW )

1

10

11

40

84

41

PIN NOMENCLATURE

A[0:10]

Row Address Inputs

A[0:8]

Column Address Inputs

A11/BA0

Bank-Select Zero

CAS

Column-Address Strobe

CKE[0:1]

Clock Enable

CK[0:3]

System Clock

DQ[0:63]

Data-In / Data-Out

DQMB[0:7]

Data-In/Data-Out

Mask Enable

NC

No Connect

RAS

Row-Address Strobe

S[0:3]

Chip-Select

SA[0:2]

Serial Presence-Detect (SPD)

Device Address Input

SCL

SPD Clock

SDA

SPD Address / Data

VDD

3.3-V Supply

VSS

Ground

WE

Write Enable

TM2SN64EPN

( SIDE VIEW )

PRODUCT PREVIEW

TM2SN64EPN 2097152 BY 64-BIT

TM4SN64EPN 4194304 BY 64-BIT

SYNCHRONOUS DYNAMIC RAM MODULES

SMMS696 AUGUST 1997

4

POST OFFICE BOX 1443

·

HOUSTON, TEXAS 772511443

dual-in-line memory module and components

The dual-in-line memory module and components include:

D

PC substrate: 1,27

±

0,1 mm (0.05 inch) nominal thickness; 0.005 inch/inch maximum warpage

D

Bypass capacitors: Multilayer ceramic

D

Contact area: Nickel plate and gold plate over copper

functional block diagram for the TM2SN64EPN

8

DQ[0:7]

8

CS

U0

CS

U4

R

R

S0

DQMB0

DQ[0:7]

DQMB4

DQ[32:39]

DQM

DQ[0:7]

DQM

RAS

RAS: SDRAM U[0:7]

CK0

CK: U1, U5

CK2

C

SPD EEPROM

SA0

SA1

SA2

A0

A1

A2

SCL

SDA

8

DQ[0:7]

8

CS

U1

CS

U5

R

R

DQMB1

DQ[8:15]

DQMB5

DQ[40:47]

DQM

DQ[0:7]

DQM

R = 10

RC = 10

C = 10 pF

8

DQ[0:7]

8

CS

U2

CS

U6

R

R

S2

DQMB2

DQ[16:23]

DQMB6

DQ[48:55]

DQM

DQ[0:7]

DQM

8

DQ[0:7]

8

CS

U3

CS

U7

R

R

DQMB3

DQ[24:31]

DQMB7

DQ[56:63]

DQM

DQ[0:7]

DQM

CAS

CAS: SDRAM U[0:7]

WE

WE: SDRAM U[0:7]

CKE0

CKE: SDRAM U[0:7]

A[0:11]

A[0:11]: SDRAM U[0:7]

RC

RC

RC

VDD

VSS

Two 0.1

µ

F

(minimum) per

SDRAM

U[0:7]

U[0:7]

CK1

CK: U2, U6

CK: U3, U7

CK3

C

RC

RC

RC

CK: U0, U4

LEGEND: CS

=

Chip select

SPD =

Serial Presence Detect

PRODUCT PREVIEW