TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C DECEMBER 1996 REVISED JANUARY 1999

1

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

D

Conversion Time

10

µ

s

D

10-Bit-Resolution ADC

D

Programmable Power-Down

Mode . . . 1

µ

A

D

Wide Range Single-Supply Operation of

2.7 V dc to 5.5 V dc

D

Analog Input Range of 0 V to V

CC

D

Built-in Analog Multiplexer with 8 Analog

Input Channels

D

TMS320 DSP and Microprocessor SPI and

QSPI Compatible Serial Interfaces

D

End-of-Conversion (EOC) Flag

D

Inherent Sample-and-Hold Function

D

Built-In Self-Test Modes

D

Programmable Power and Conversion Rate

D

Asynchronous Start of Conversion for

Extended Sampling

D

Hardware I/O Clock Phase Adjust Input

description

The TLV1544 and TLV1548 are CMOS 10-bit

switched-capacitor successive-approximation (SAR)

analog-to-digital (A/D) converters. Each device

has a chip select (CS), input-output clock (I/O

CLK), data input (DATA IN) and serial data output

(DATA OUT) that provide a direct 4-wire

synchronous serial peripheral interface (SPI

TM

,

QSPI

TM

) port of a host microprocessor. When

interfacing with a TMS320 DSP, an additional

frame sync signal (FS) indicates the start of a

serial data frame. The devices allow high-speed

data transfers from the host. The INV CLK input

provides further timing flexibility for the serial

interface.

In addition to a high-speed converter and versatile

control capability, the device has an on-chip

11-channel multiplexer that can select any one of

eight analog inputs or any one of three internal self-test voltages. The sample-and-hold function is automatic

except for the extended sampling cycle, where the sampling cycle is started by the falling edge of asynchronous

CSTART. At the end of the A/D conversion, the end-of-conversion (EOC) output goes high to indicate that the

conversion is complete. The TLV1544 and TLV1548 are designed to operate with a wide range of supply

voltages with very low power consumption. The power saving feature is further enhanced with a

software-programmed power-down mode and conversion rate. The converter incorporated in the device

features differential high-impedance reference inputs that facilitate ratiometric conversion, scaling, and

isolation of analog circuitry from logic and supply noise. A switched-capacitor design allows low-error

conversion over the full operating temperature range.

SPI and QSPI are registered trademarks of Motorola, Inc.

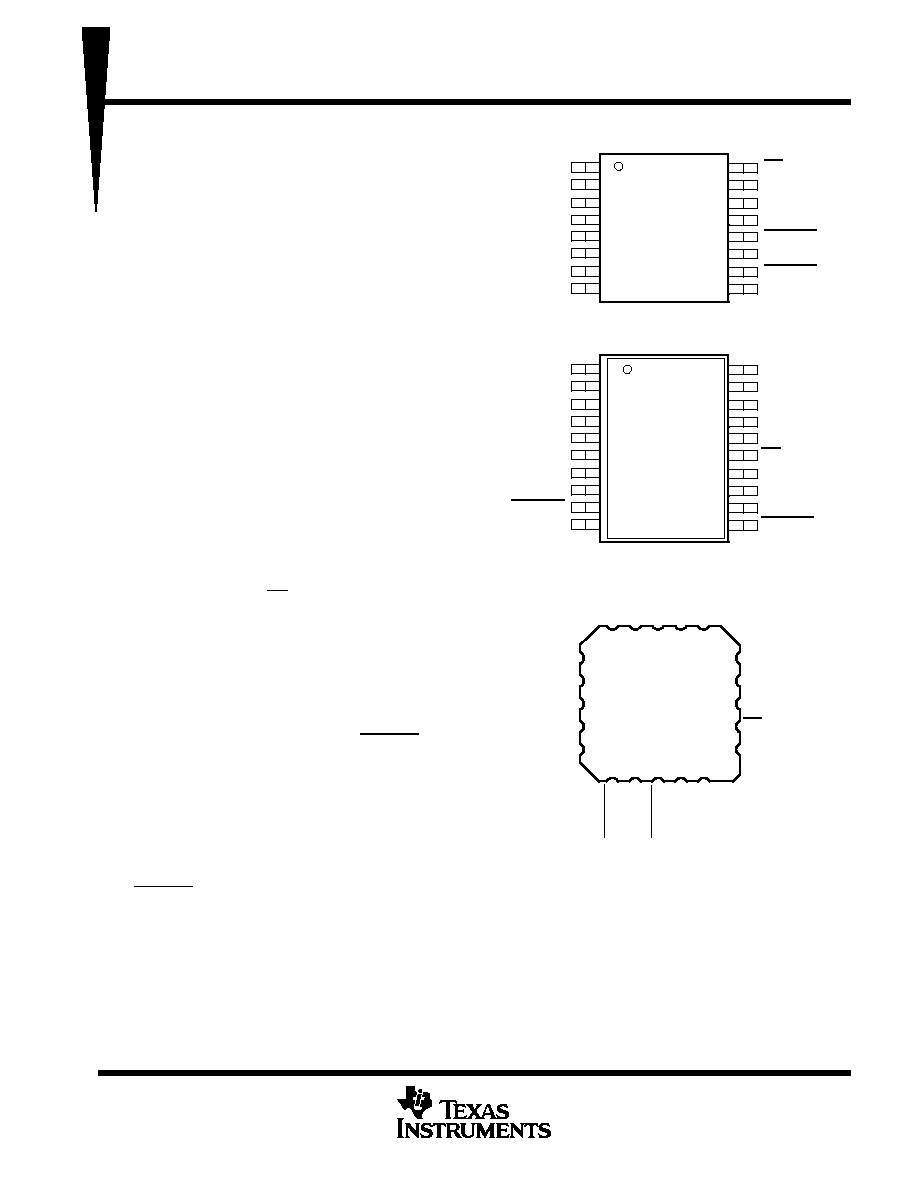

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

A0

A1

A2

A3

A4

A5

A6

A7

CSTART

GND

V

CC

EOC

I/O CLK

DATA IN

DATA OUT

CS

REF+

REF

FS

INV CLK

DB OR J PACKAGE

(TOP VIEW)

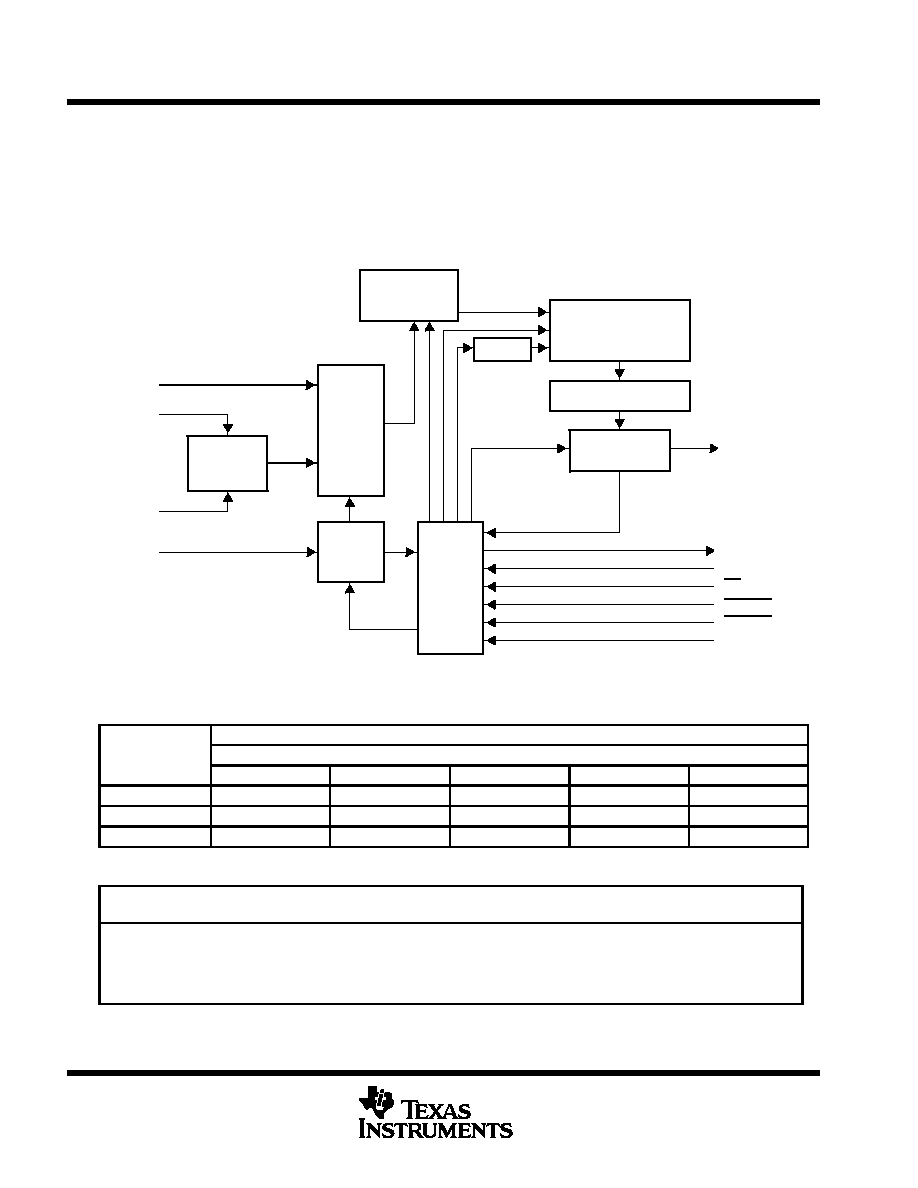

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

DATA OUT

DATA IN

I/O CLK

EOC

V

CC

A0

A1

A2

CS

REF+

REF

FS

INV CLK

GND

CSTART

A3

D OR PW PACKAGE

(TOP VIEW)

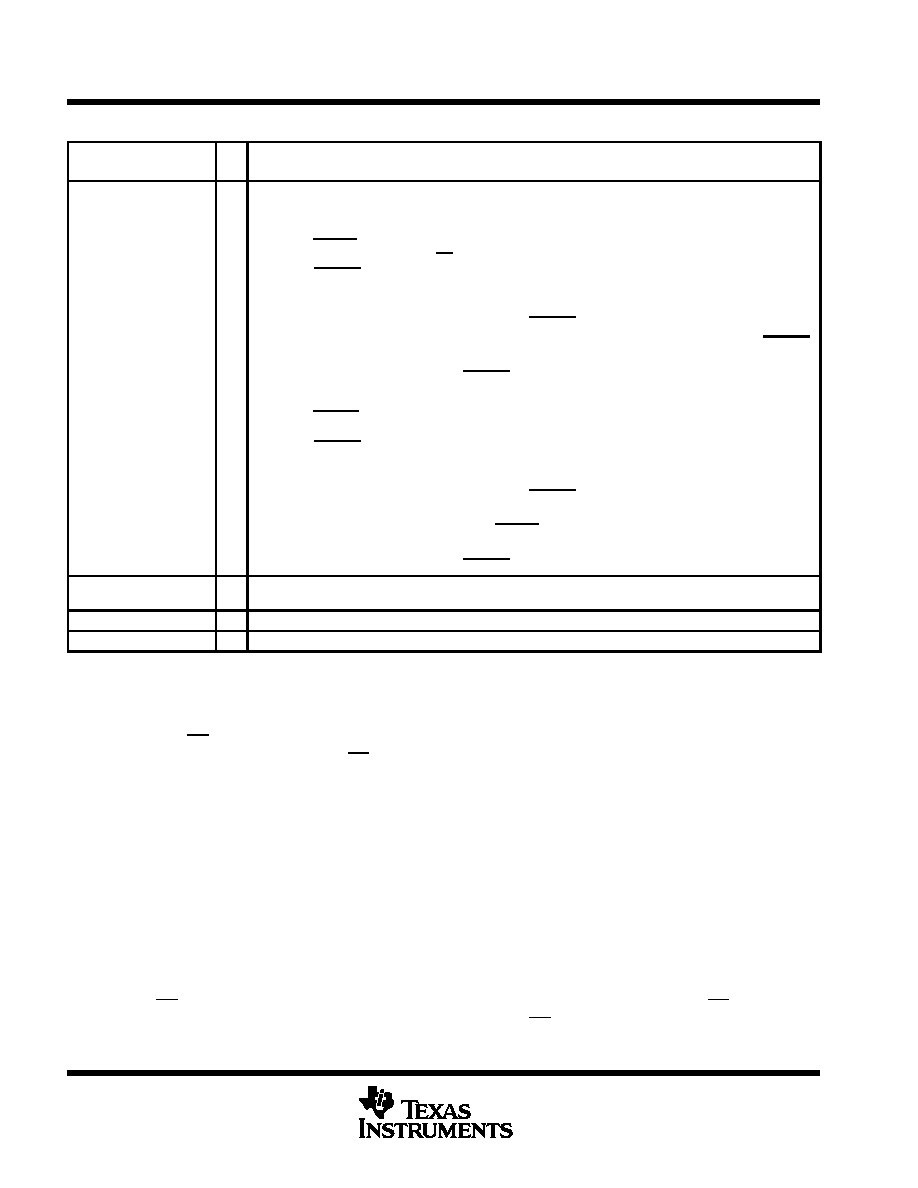

19

20

1

3

2

17

18

16

15

14

13

12

11

9

10

5

4

6

7

8

I/O CLK

DATA IN

DATA OUT

CS

REF+

A3

A4

A5

A6

A7

A2

A1

A0

V

EOC

GND

INV CLK

FS

REF

CST

AR

T

FK PACKAGE

(TOP VIEW)

CC

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright

©

1999, Texas Instruments Incorporated

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C DECEMBER 1996 REVISED JANUARY 1999

2

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

description (continued)

The TLV1544 has four analog input channels while the TLV1548 has eight analog input channels. The

TLV1544C and TLV1548C are characterized for operation from 0

°

C to 70

°

C. The TLV1544I and TLV1548I are

characterized for operation over the full industrial temperature range of 40

°

C to 85

°

C. The TLV1548M is

characterized for operation over the full military temperature range of 55

°

C to 125

°

C.

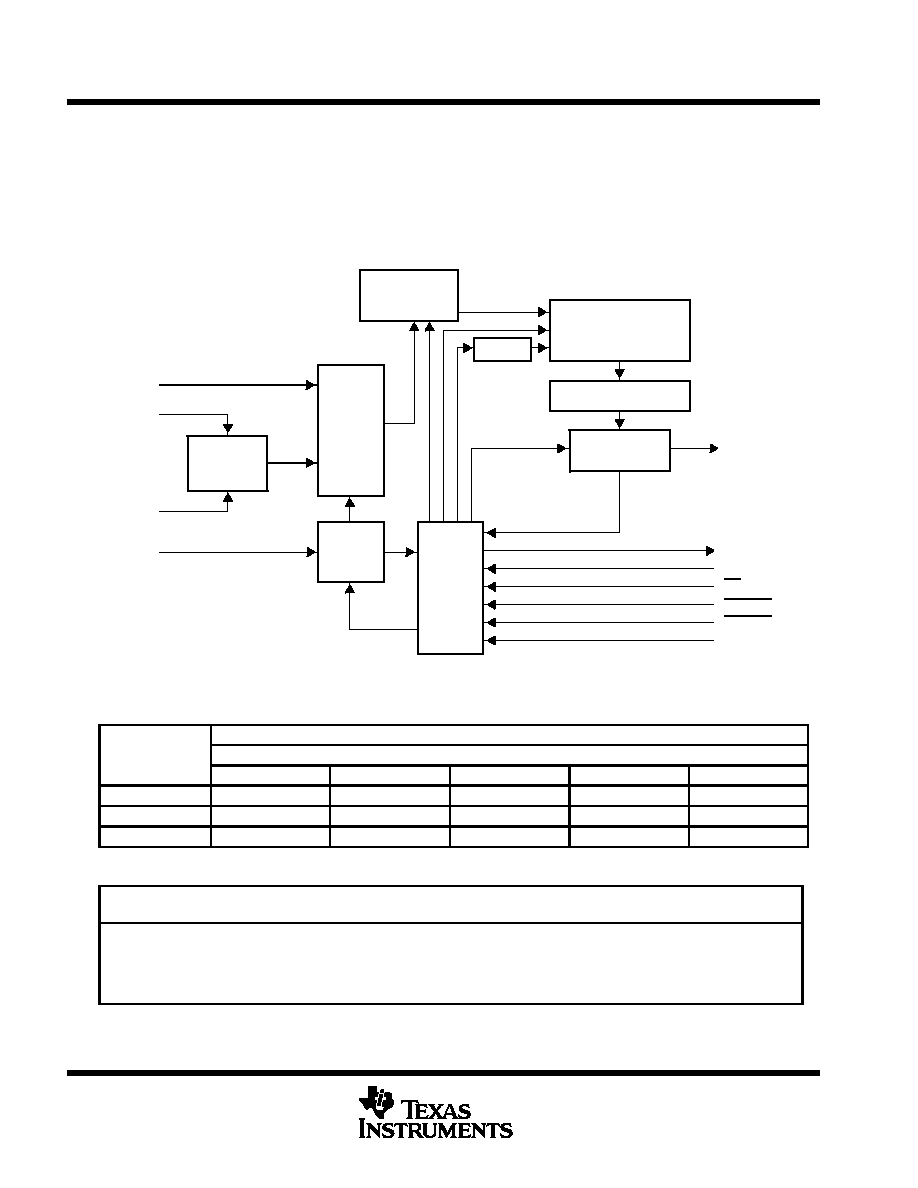

functional block diagram

Analog

MUX

Self-Test

Reference

Input

Data

Register

Control

Logic

and

I/O

Counters

10-Bit ADC

(Switch Capacitors)

Output Data Register

10-to-1

Data Selector

Sample

and

Hold Function

CLOCK

A0A7

REF+

REF

DATA IN

DATA OUT

EOC

FS

CS

CSTART

INV CLK

I/O CLK

Terminals shown are for the DB package.

18

14

13

17

16

19

12

15

9

11

18

AVAILABLE OPTIONS

PACKAGE

TA

SMALL OUTLINE

(DB)

(D)

(PW)

(J)

(FK)

0

°

C to 70

°

C

TLV1548CDB

TLV1544CD

TLV1544CPW

40

°

C to 85

°

C

TLV1548IDB

TLV1544ID

TLV1544IPW

55

°

C to 125

°

C

TLV1548MJ

TLV1548MFK

DISSIPATION RATING TABLE

PACKAGE

TA

25

°

C

DERATING FACTOR

TA = 70

°

C

TA = 85

°

C

TA = 125

°

C

PACKAGE

A

POWER RATING

ABOVE TA = 25

°

C

A

POWER RATING

A

POWER RATING

A

POWER RATING

DB

D

785 mW

799 mW

8.7 mW/

°

C

8 9 mW/

°

C

393 mW

399 mW

261 mW

266 mW

--

--

D

PW

J

799 mW

604 mW

1894 mW

8.9 mW/

°

C

6.7 mW/

°

C

15 1 mW/

°

C

399 mW

302 mW

1212 mW

266 mW

201 mW

985 mW

--

--

379 mW

J

FK

1894 mW

1375 mW

15.1 mW/

°

C

11.0 mW/

°

C

1212 mW

880 mW

985 mW

715 mW

379 mW

275 mW

This is the inverse of the traditional junction-to-ambient thermal resistance (R

JA). R

JA values are derived from Texas Instruments

characterization data. Thermal resistance is not production tested and values are given for informational purposes only.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C DECEMBER 1996 REVISED JANUARY 1999

3

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

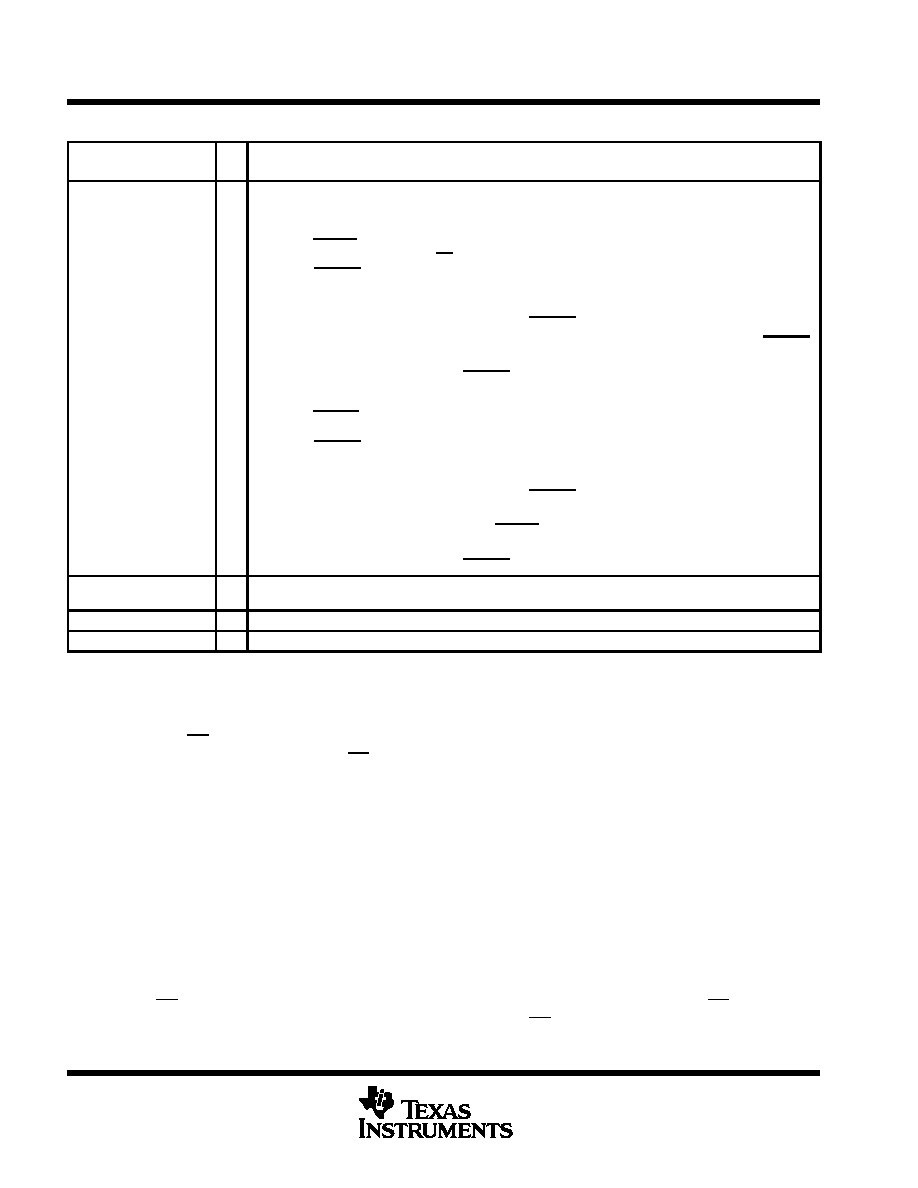

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

NO.

I/O

DESCRIPTION

A0A3

A4A7

69

14

58

I

Analog inputs. The analog inputs are internally multiplexed. (For a source impedance greater than

1 k

, the asynchronous start should be used to increase the sampling time.)

CS

16

15

I

Chip select. A high-to-low transition on CS resets the internal counters and controls and enables DATA IN,

DATA OUT, and I/O CLK within the maximum setup time. A low-to-high transition disables DATA IN, DATA

OUT, and I/O CLK within the setup time.

CSTART

10

9

I

Sampling/conversion start control. CSTART controls the start of the sampling of an analog input from a

selected multiplex channel. A high-to-low transition starts the sampling of the analog input signal. A

low-to-high transition puts the sample-and-hold function in hold mode and starts the conversion. CSTART

is independent from I/O CLK and works when CS is high. The low CSTART duration controls the duration

of the sampling cycle for the switched capacitor array. CSTART is tied to VCC if not used.

DATA IN

2

17

I

Serial data input. The 4-bit serial data selects the desired analog input and test voltage to be converted next

in a normal cycle. These bits can also set the conversion rate and enable the power-down mode.

When operating in the microprocessor mode, the input data is presented MSB first and is shifted in on the

first four rising (INV CLK = VCC) or falling (INV CLK = GND) edges of I/O CLK (after CS

).

g (

CC)

g (

)

g

(

)

When operating in the DSP mode, the input data is presented MSB first and is shifted in on the first four

falling (INV CLK = VCC) or rising (INV CLK = GND) edges of I/O CLK (after FS

).

After the four input data bits have been read into the input data register, DATA IN is ignored for the remainder

of the current conversion period.

DATA OUT

1

16

O

Three-state serial output of the A/D conversion result. DATA OUT is in the high-impedance state when CS

is high and active when CS is low or after FS

(in DSP mode). With a valid CS signal, DATA OUT is removed

from the high-impedance state and is driven to the logic level corresponding to the MSB or LSB value of

the previous conversion result. DATA OUT changes on the falling (microprocessor mode) or rising (DSP

mode) edge of I/O CLK.

EOC

4

19

O

End of conversion. EOC goes from a high to a low logic level on the tenth rising (microprocessor mode)

or tenth falling (DSP mode) edge of I/O CLK and remains low until the conversion is complete and data is

ready for transfer. EOC can also indicate that the converter is busy.

FS

13

12

I

DSP frame synchronization input. FS indicates the start of a serial data frame into or out of the device. FS

is tied to VCC when interfacing the device with a microprocessor.

GND

11

10

Ground return for internal circuitry. All voltage measurements are with respect to GND, unless otherwise

noted.

INV CLK

12

11

I

Inverted clock input. INV CLK is tied to GND when an inverted I/O CLK is used as the source of the input

clock. This affects both microprocessor and DSP interfaces. INV CLK is tied to VCC if I/O CLK is not

inverted. INV CLK can also invoke a built-in test mode.

Terminal numbers are for the D package.

Terminal numbers are for the DB, J, and FK packages.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C DECEMBER 1996 REVISED JANUARY 1999

4

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

Terminal Functions (Continued)

TERMINAL

I/O

DESCRIPTION

NAME

NO.

NO.

I/O

DESCRIPTION

I/O CLK

3

18

I

Input/output clock. I/O CLK receives the serial I/O clock input in the two modes and performs the following

four functions in each mode:

Microprocessor mode

·

When INVCLK = VCC, I/O CLK clocks the four input data bits into the input data register on the first four

rising edges of I/O CLK after CS

with the multiplexer address available after the fourth rising edge.

When INV CLK = GND, input data bits are clocked in on the first four falling edges instead.

·

On the fourth falling edge of I/O CLK, the analog input voltage on the selected multiplex input begins

charging the capacitor array and continues to do so until the tenth rising edge of I/O CLK except in the

extended sampling cycle where the duration of CSTART determines when to end the sampling cycle.

·

Output data bits change on the first ten falling I/O clock edges regardless of the condition of INV CLK.

·

I/O CLK transfers control of the conversion to the internal state machine on the tenth rising edge of I/O

CLK regardless of the condition of INV CLK.

Digital signal processor (DSP) mode

·

When INV CLK = VCC, I/O CLK clocks the four input data bits into the input data register on the first four

falling edges of I/O CLK after FS

with the multiplexer address available after the fourth falling edges.

When INV CLK = GND, input data bits are clocked in on the first four rising edges instead.

·

On the fourth rising edge of I/O CLK, the analog input voltage on the selected multiplex input begins

charging the capacitor array and continues to do so until the tenth falling edge of I/O CLK except in the

extended sampling cycle where the duration of CSTART determines when to end the sampling cycle.

·

Output data MSB shows after FS

and the rest of the output data bits change on the first ten rising I/O

CLK edges regarless of the condition of INV CLK.

·

I/O CLK transfers control of the conversion to the internal state machine on the tenth falling edge of I/O

CLK regardless of the condition of INV CLK.

REF+

15

14

I

Upper reference voltage (nominally VCC ). The maximum input voltage range is determined by the difference

between the voltages applied to REF+ and REF.

REF

14

13

I

Lower reference voltage (nominally ground)

VCC

5

20

I

Positive supply voltage

Terminal numbers are for the D package.

Terminal numbers are for the DB, J, and FK packages.

detailed description

Initially, with CS high (inactive), DATA IN and I/O CLK are disabled and DATA OUT is in the high-impedance

state. When the serial interface takes CS low (active), the conversion sequence begins with the enabling of I/O

CLK and DATA IN and the removal of DATA OUT from the high-impedance state. The host then provides the

4-bit channel address to DATA IN and the I/O clock sequence to I/O CLK. During this transfer, the host serial

interface also receives the previous conversion result from DATA OUT. I/O CLK receives an input sequence from

the host that is from 10 to 16 clocks long. The first four valid I/O CLK cycles load the input data register with the

4-bit input data on DATA IN that selects the desired analog channel. The next six clock cycles provide the control

timing for sampling the analog input. Sampling of the analog input is held after the first valid I/O CLK sequence

of ten clocks. The tenth clock edge also takes EOC low and begins the conversion. The exact locations of the

I/O clock edges depend on the mode of operation.

serial interface

The TLV1548 is compatible with generic microprocessor serial interfaces such as SPI and QSPI, and a TMS320

DSP serial interface. The internal latched flag If_mode is generated by sampling the state of FS at the falling

edge of CS. If_mode is set to one (for microprocessor) when FS is high at the falling edge of CS, and If_mode

is cleared to zero (for DSP) when FS is low at the falling edge of CS. This flag controls the multiplexing of I/O

CLK and the state machine reset function. FS is pulled high when interfacing with a microprocessor.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C DECEMBER 1996 REVISED JANUARY 1999

5

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

I/O CLK

The I/O CLK can go up to 10 MHz for most of the voltage range when fast I/O is possible. The maximum I/O

CLK is limited to 2.8 MHz for a supply voltage range from 2.7 V. Table 1 lists the maximum I/O CLK frequencies

for all different supply voltage ranges. This also depends on input source impedance. For example, I/O CLK

speed faster than 2.39 MHz is achievable if the input source impedance is less than 1 k

.

Table 1. Maximum I/O CLK Frequency

VCC

MAXIMUM INPUT

RESISTANCE (Max)

SOURCE IMPEDANCE

I/O CLK

2 7 V

5 K

1 k

2.39 MHz

2.7 V

5 K

100

2.81 MHz

4 5 V

1 K

1 k

7.18 MHz

4.5 V

1 K

100

10 MHz

microprocessor serial interface

Input data bits from DATA IN are clocked in on the first four rising edges of the I/O CLK sequence if INV CLK

is held high when the device is in microprocessor interface mode. Input data bits are clocked in on the first four

falling edges of the I/O CLK sequence if INV CLK is held low. The MSB of the previous conversion appears on

DATA OUT on the falling edge of CS. The remaining nine bits are shifted out on the next nine edges (depending

on the state of INV CLK) of I/O CLK. Ten bits of data are transmitted to the host through DATA OUT.

A minimum of 9.5 clock pulses is required for the conversion to begin. On the tenth clock rising edge, the EOC

output goes low and returns to the high logic level when the conversion is complete; then the result can be read

by the host. On the tenth clock falling edge, the internal logic takes DATA OUT low to ensure that the remaining

bit values are zero if the I/O CLK transfer is more than ten clocks long.

CS is inactive (high) between serial I/O CLK transfers. Each transfer takes at least ten I/O CLK cycles. The falling

edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The rising edge of

CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time. Also,

the rising edge of CS disables I/O CLK and DATA IN within a setup time. A conversion does not begin until the

tenth I/O CLK rising edge.

A high-to-low transition on CS within the specified time during an ongoing cycle aborts the cycle, and the device

returns to the initial state (the output data register holds the previous conversion result). CS should not be taken

low close to completion of conversion because the output data can be corrupted.