1

Data sheet acquired from Harris Semiconductor

SCHS176D

Features

À Adds Two Binary Numbers

À Full Internal Lookahead

À Fast Ripple Carry for Economical Expansion

À Operates with Both Positive and Negative Logic

À Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

À Wide Operating Temperature Range . . . -55

o

C to 125

o

C

À Balanced Propagation Delay and Transition Times

À Significant Power Reduction Compared to LSTTL

Logic ICs

À HC Types

- 2V to 6V Operation

- High Noise Immunity: N

IL

= 30%, N

IH

= 30% of V

CC

at V

CC

= 5V

À HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

IL

= 0.8V (Max), V

IH

= 2V (Min)

- CMOS Input Compatibility, I

l

1

Á

A at V

OL

, V

OH

Description

The 'HC283 and 'HCT283 binary full adders add two 4-bit

binary numbers and generate a carry-out bit if the sum

exceeds 15.

Because of the symmetry of the add function, this device

can be used with either all active-high operands (positive

logic) or with all active-low operands (negative logic). When

using positive logic the carry-in input must be tied low if there

is no carry-in.

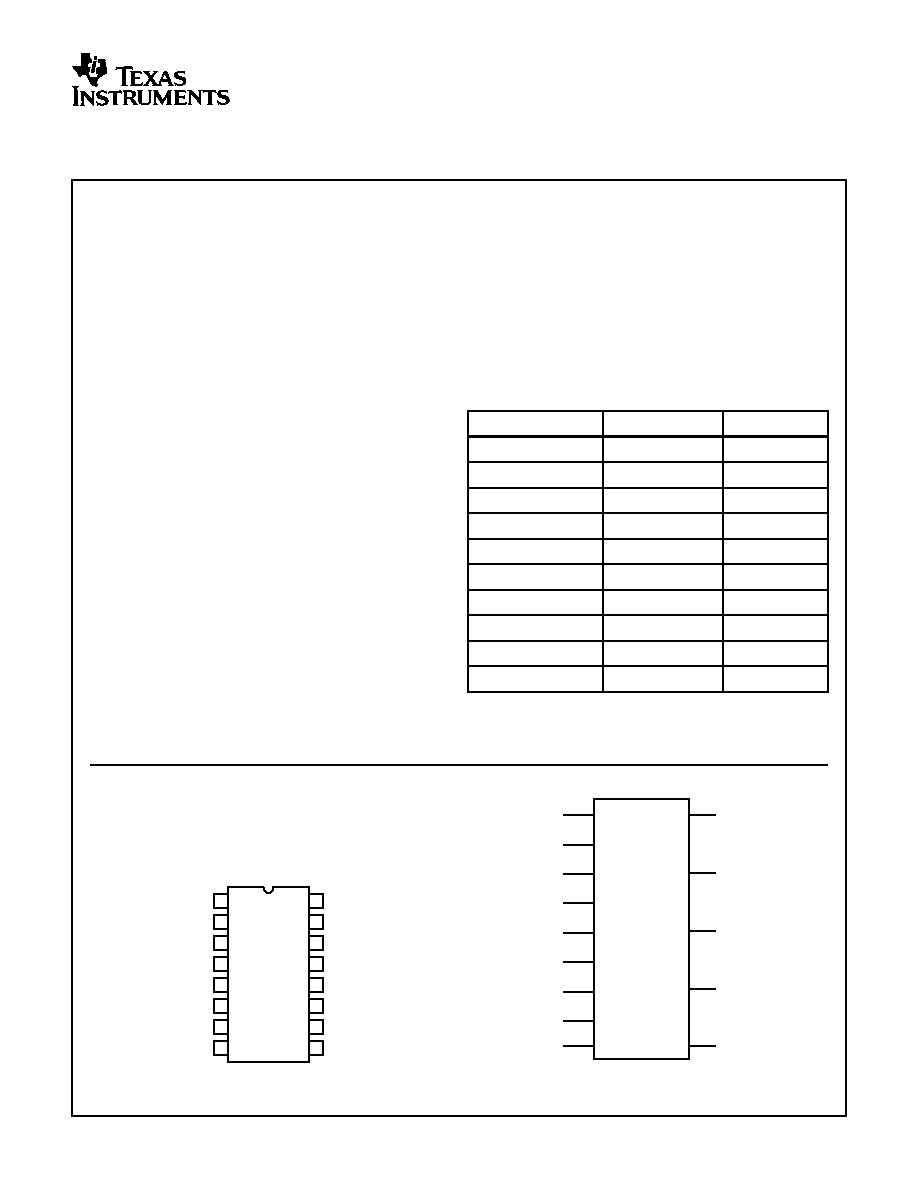

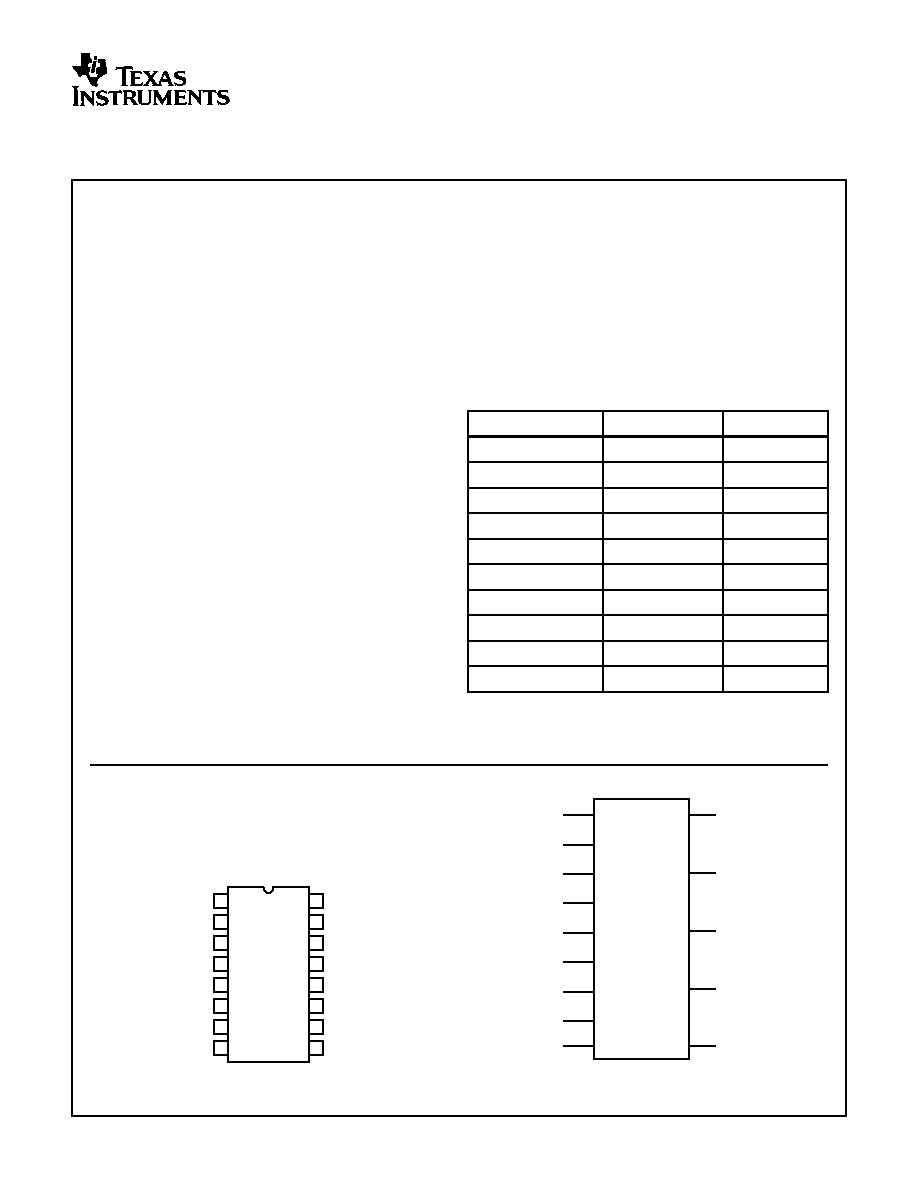

Ordering Information

PART NUMBER

TEMP. RANGE (

o

C)

PACKAGE

CD54HC283F3A

-55 to 125

16 Ld CERDIP

CD54HCT283F3A

-55 to 125

16 Ld CERDIP

CD74HC283E

-55 to 125

16 Ld PDIP

CD74HC283M

-55 to 125

16 Ld SOIC

CD74HC283MT

-55 to 125

16 Ld SOIC

CD74HC283M96

-55 to 125

16 Ld SOIC

CD74HCT283E

-55 to 125

16 Ld PDIP

CD74HCT283M

-55 to 125

16 Ld SOIC

CD74HCT283MT

-55 to 125

16 Ld SOIC

CD74HCT283M96

-55 to 125

16 Ld SOIC

NOTE: When ordering, use the entire part number. The suffix 96

denotes tape and reel. The suffix T denotes a small-quantity reel of

250.

Pinout

CD54HC283, CD54HCT283

(CERDIP)

CD74HC283, CD74HCT283

(PDIP, SOIC)

TOP VIEW

Functional Diagram

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

S1

B1

A1

S0

A0

B0

GND

C

IN

V

CC

A2

S2

A3

B3

S3

C

OUT

B2

5

6

3

2

15

11

12

14

4

9

S2

S1

A0

B0

A1

B1

B2

A3

B3

A2

7

C

IN

GND = 8

V

CC

= 16

10

13

1

S0

S3

C

OUT

November 1997 - Revised October 2003

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

®

2003, Texas Instruments Incorporated

CD54HC283, CD74HC283,

CD54HCT283, CD74HCT283

High-Speed CMOS Logic

4-Bit Binary Full Adder with Fast Carry

[ /Title

(CD74

HC283

,

CD74

HCT28

3)

/Sub-

ject

(High

Speed

CMOS

Logic

4-Bit

Binary

Full

Adder

2

Absolute Maximum Ratings

Thermal Information

DC Supply Voltage, V

CC

. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V

DC Input Diode Current, I

IK

For V

I

< -0.5V or V

I

> V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . . . .▒

20mA

DC Output Diode Current, I

OK

For V

O

< -0.5V or V

O

> V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . .▒

20mA

DC Drain Current, per Output, I

O

For -0.5V < V

O

< V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . . . . . . . .▒

25mA

DC Output Source or Sink Current per Output Pin, I

O

For V

O

> -0.5V or V

O

< V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . .▒

25mA

DC V

CC

or Ground Current, I

CC

. . . . . . . . . . . . . . . . . . . . . . . . .▒

50mA

Operating Conditions

Temperature Range, T

A

. . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

Supply Voltage Range, V

CC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V

DC Input or Output Voltage, V

I

, V

O

. . . . . . . . . . . . . . . . . 0V to V

CC

Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max)

4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

E (PDIP) Package . . . . . . . . . . . . . . . . . . . . . . . . . .

67

M (SOIC) Package. . . . . . . . . . . . . . . . . . . . . . . . . .

73

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

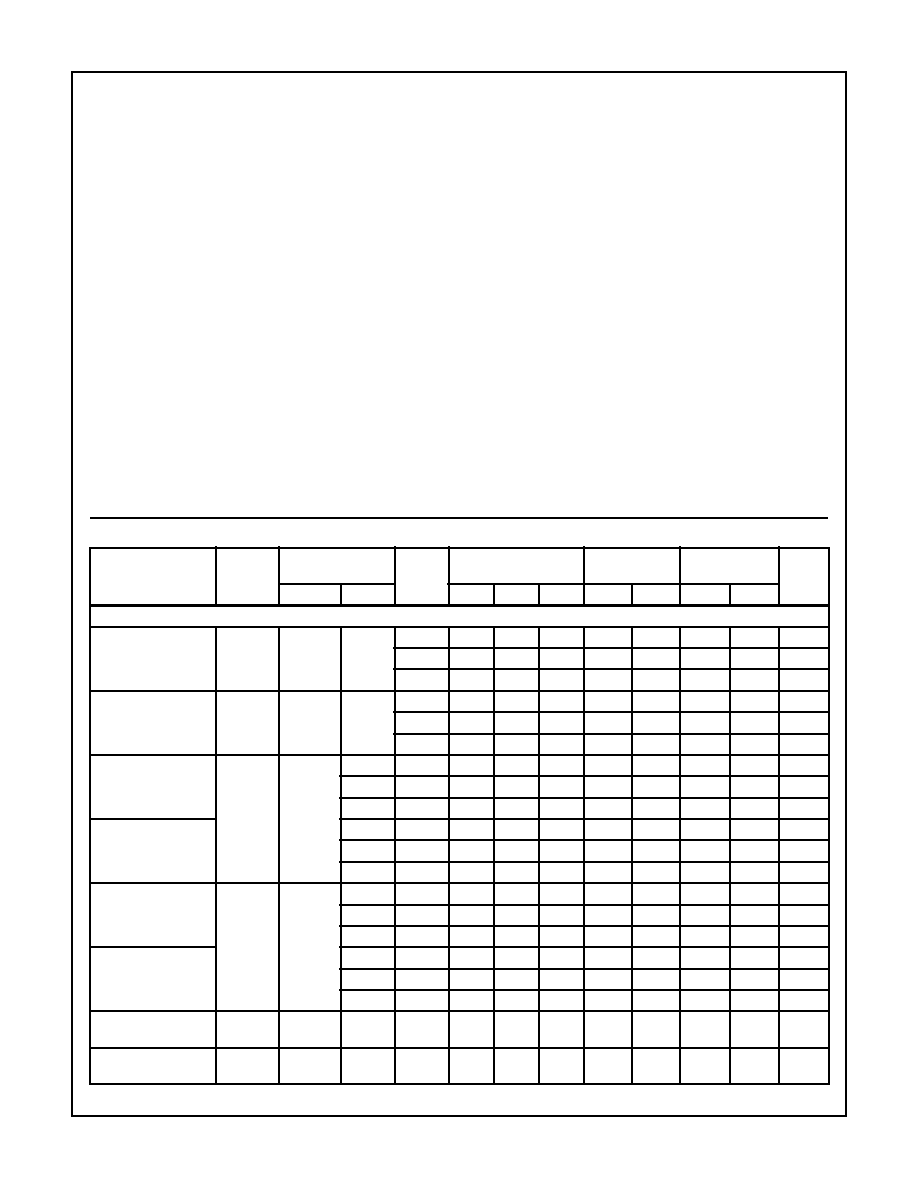

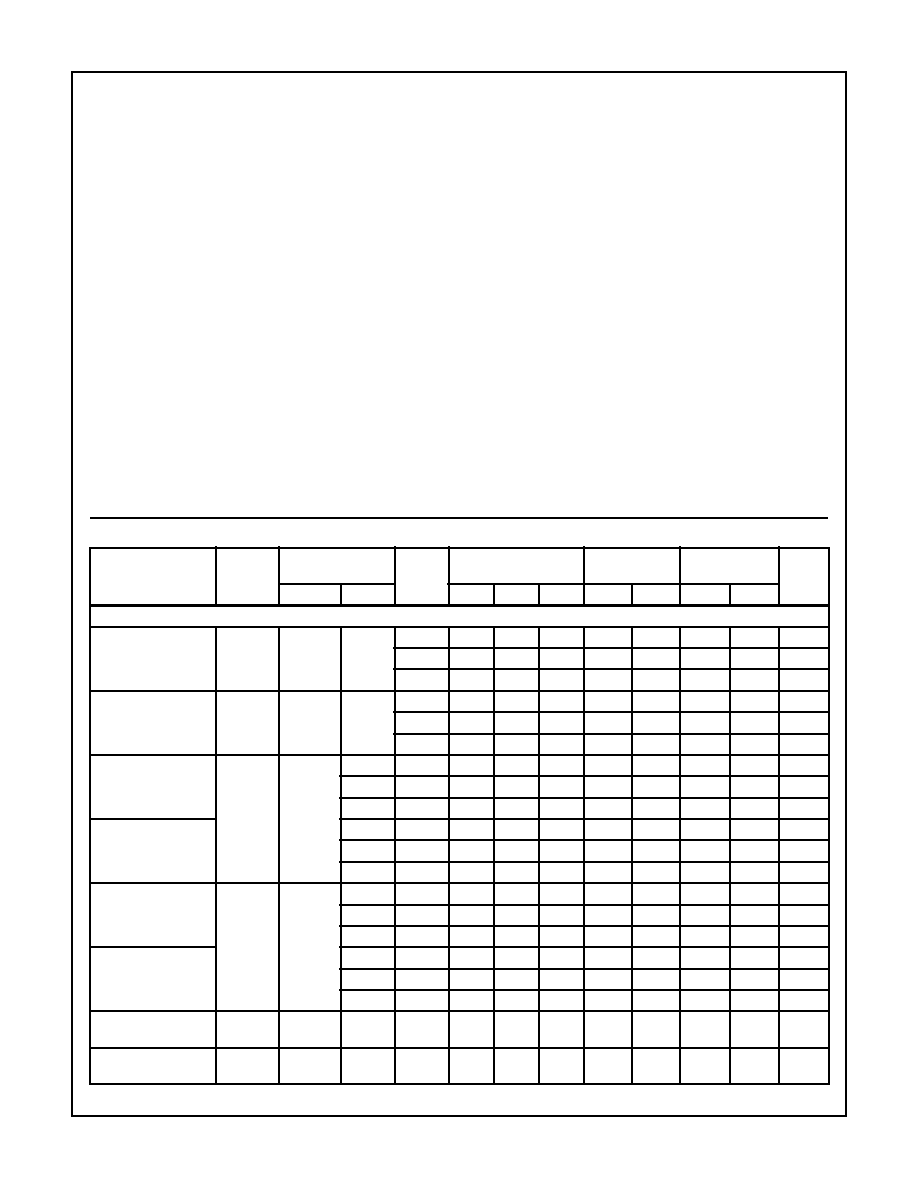

DC Electrical Specifications

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITS

V

I

(V)

I

O

(mA)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HC TYPES

High Level Input

Voltage

V

IH

-

-

2

1.5

-

-

1.5

-

1.5

-

V

4.5

3.15

-

-

3.15

-

3.15

-

V

6

4.2

-

-

4.2

-

4.2

-

V

Low Level Input

Voltage

V

IL

-

-

2

-

-

0.5

-

0.5

-

0.5

V

4.5

-

-

1.35

-

1.35

-

1.35

V

6

-

-

1.8

-

1.8

-

1.8

V

High Level Output

Voltage

CMOS Loads

V

OH

V

IH

or V

IL

-0.02

2

1.9

-

-

1.9

-

1.9

-

V

-0.02

4.5

4.4

-

-

4.4

-

4.4

-

V

-0.02

6

5.9

-

-

5.9

-

5.9

-

V

High Level Output

Voltage

TTL Loads

-

-

-

-

-

-

-

-

-

V

-4

4.5

3.98

-

-

3.84

-

3.7

-

V

-5.2

6

5.48

-

-

5.34

-

5.2

-

V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or V

IL

0.02

2

-

-

0.1

-

0.1

-

0.1

V

0.02

4.5

-

-

0.1

-

0.1

-

0.1

V

0.02

6

-

-

0.1

-

0.1

-

0.1

V

Low Level Output

Voltage

TTL Loads

-

-

-

-

-

-

-

-

-

V

4

4.5

-

-

0.26

-

0.33

-

0.4

V

5.2

6

-

-

0.26

-

0.33

-

0.4

V

Input Leakage

Current

I

I

V

CC

or

GND

-

6

-

-

▒

0.1

-

▒

1

-

▒

1

Á

A

Quiescent Device

Current

I

CC

V

CC

or

GND

0

6

-

-

8

-

80

-

160

Á

A

CD54HC283, CD74HC283, CD54HCT283, CD74HCT283

3

HCT Types

High Level Input

Voltage

V

IH

-

-

4.5 to

5.5

2

-

-

2

-

2

-

V

Low Level Input

Voltage

V

IL

-

-

4.5 to

5.5

-

-

0.8

-

0.8

-

0.8

V

High Level Output

Voltage

CMOS Loads

V

OH

V

IL

or V

IH

-0.02

4.5

4.4

-

-

4.4

-

4.4

-

V

High Level Output

Voltage

TTL Loads

V

OH

V

IL

or V

IH

-4

4.5

3.98

-

-

3.84

-

3.7

-

V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or V

IL

0.02

4.5

-

-

0.1

-

0.1

-

0.1

V

Low Level Output

Voltage

TTL Loads

V

OL

V

IH

or V

IL

4

4.5

-

-

0.26

-

0.33

-

0.4

V

Input Leakage

Current

I

I

V

CC

to

GND

-

5.5

-

-

▒

0.1

-

▒

1

-

▒

1

Á

A

Quiescent Device

Current

ICC

V

CC

or

GND

-

5.5

-

-

8

-

80

-

160

Á

A

Additional Quiescent

Device Current Per

Input Pin: 1 Unit Load

I

CC

(Note 2)

V

CC

- 2.1

-

4.5 to

5.5

-

100

360

-

450

-

490

Á

A

NOTE:

2. For dual-supply systems theoretical worst case (V

I

= 2.4V, V

CC

= 5.5V) specification is 1.8mA.

DC Electrical Specifications

(Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITS

V

I

(V)

I

O

(mA)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HCT Input Loading Table

INPUT

UNIT LOADS

C

IN

1.5

B1, A1, A0

1

B0

0.4

B3, A3, A2, B2

0.5

NOTE: Unit Load is

I

CC

limit specified in DC Electrical

Specifications table, e.g., 360

Á

A max at 25

o

C.

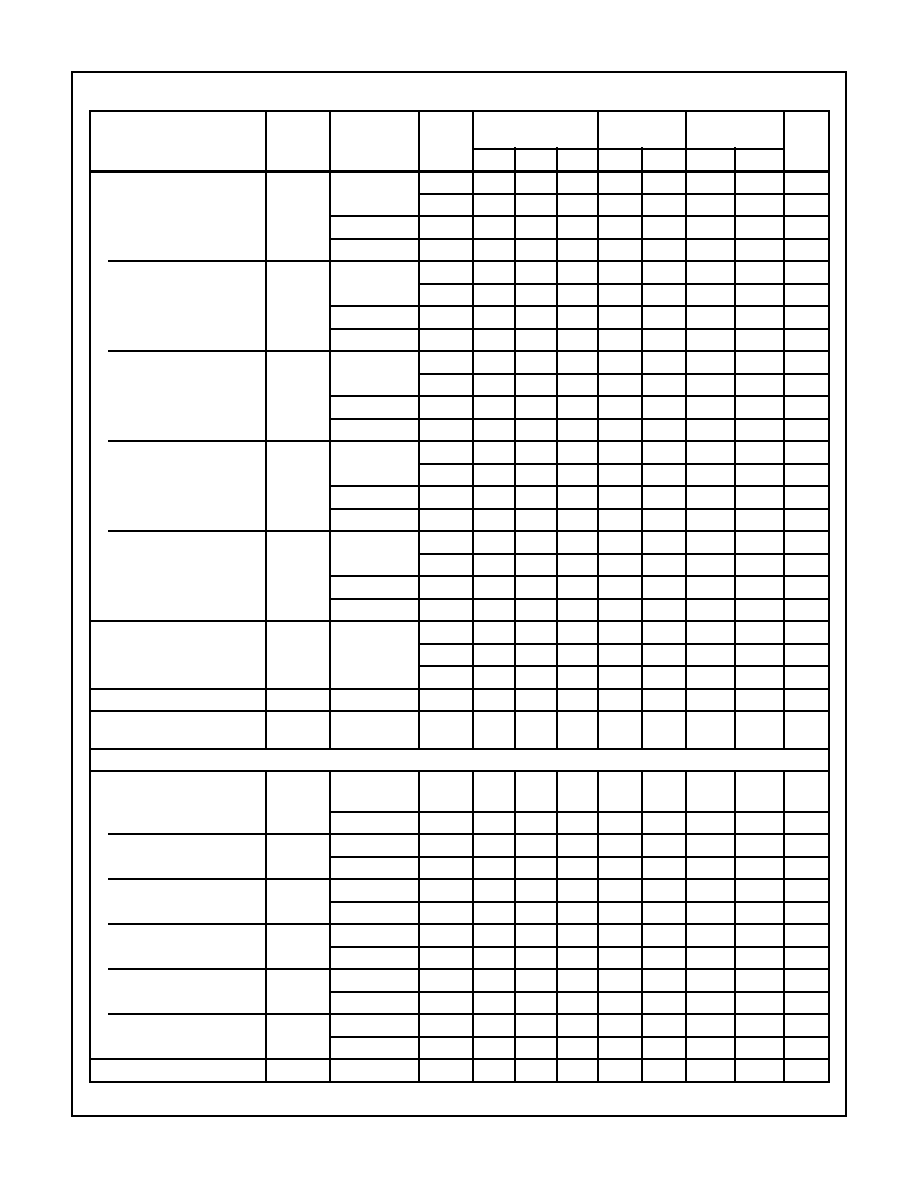

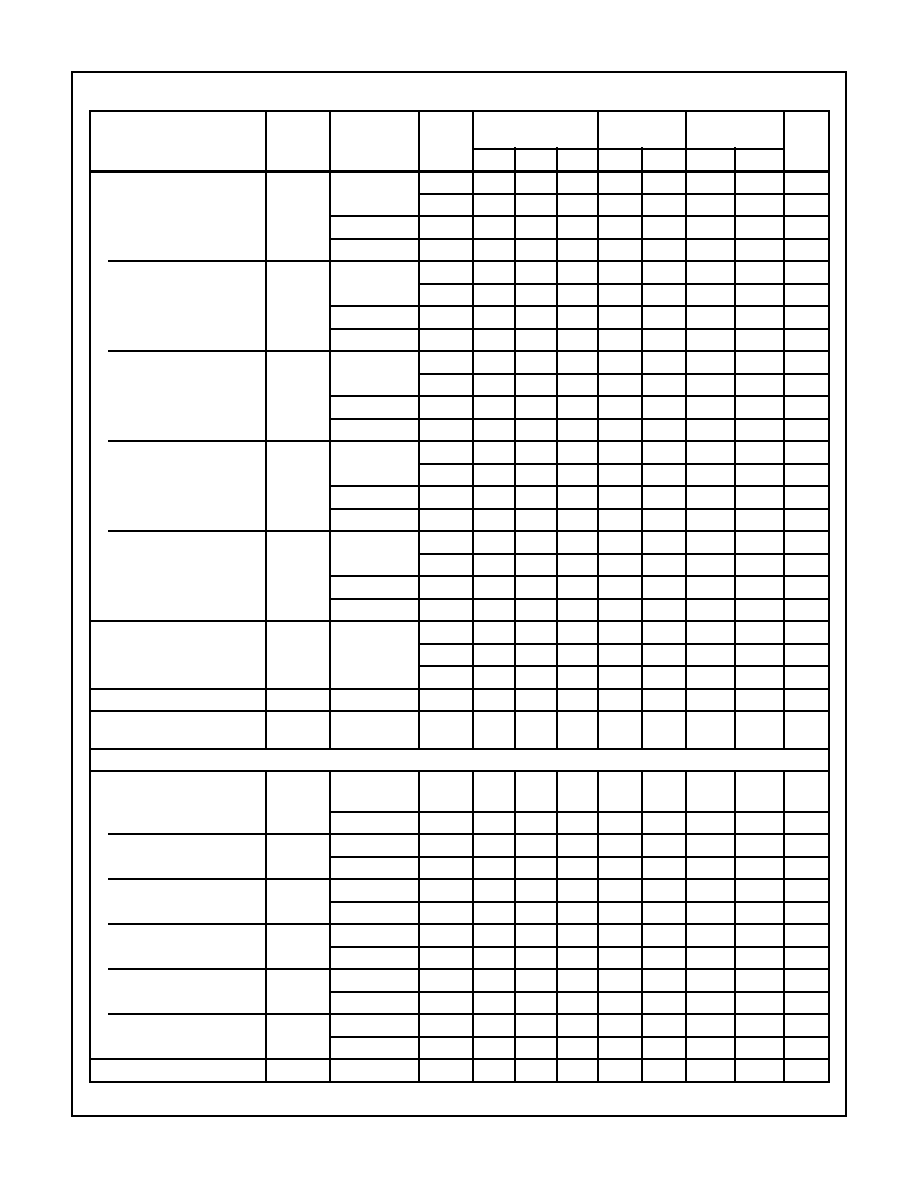

Switching Specifications

Input t

r

, t

f

= 6ns

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO

85

o

C

-55

o

C TO

125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HC TYPES

Propagation Delay

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

160

-

200

-

240

ns

C

IN

to S0

4.5

-

-

32

-

40

-

48

ns

C

L

= 15pF

5

-

13

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

27

-

34

-

41

ns

CD54HC283, CD74HC283, CD54HCT283, CD74HCT283

4

C

IN

to S1

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

180

-

225

-

270

ns

4.5

-

-

36

-

45

-

54

ns

C

L

= 15pF

5

-

15

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

31

-

38

-

46

ns

C

IN

to S2, C

IN

to C

OUT

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

195

-

245

-

295

ns

4.5

-

-

39

-

49

-

59

ns

C

L

= 15pF

5

-

16

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

33

-

42

-

50

ns

C

IN

to S3

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

230

-

290

-

345

ns

4.5

-

-

46

-

58

-

69

ns

C

L

= 15pF

5

-

19

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

39

-

49

-

59

ns

An, Bn to C

OUT

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

195

-

245

-

295

ns

4.5

-

-

39

-

49

-

59

ns

C

L

= 15pF

5

-

16

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

33

-

42

-

50

ns

An, Bn to Sn

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

210

-

265

-

315

ns

4.5

-

-

42

-

53

-

63

ns

C

L

= 15pF

5

-

18

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

36

-

45

-

54

ns

Output Transition Time

t

TLH

, t

THL

C

L

= 50pF

2

-

-

75

-

95

-

110

ns

4.5

-

-

15

-

19

-

22

ns

6

-

-

13

-

16

-

19

ns

Input Capacitance

C

IN

C

L

= 50pF

-

-

-

10

-

10

-

10

pF

Power Dissipation

Capacitance, (Notes 3, 4)

C

PD

-

5

-

70

-

-

-

-

-

pF

HCT TYPES

Propagation Delay

C

IN

to S0

t

PLH

, t

PHL

C

L

= 15pF

5

-

13

-

-

-

-

-

ns

C

L

= 50pF

4.5

-

-

31

-

39

-

47

ns

C

IN

to S1

t

PLH

, t

PHL

C

L

= 15pF

5

-

18

-

-

-

-

-

ns

C

L

= 50pF

4.5

-

43

-

54

-

65

ns

C

IN

to S2, C

IN

to C

OUT

t

PLH

, t

PHL

C

L

= 15pF

5

-

19

-

-

-

-

-

ns

C

L

= 50pF

4.5

-

46

-

58

-

69

ns

C

IN

to S3

t

PLH

, t

PHL

C

L

= 15pF

5

-

22

-

-

-

-

-

ns

C

L

= 50pF

4.5

-

53

-

66

-

80

ns

An, Bn to C

OUT

t

PLH

, t

PH

L

C

L

= 15pF

5

-

20

-

-

-

-

-

ns

C

L

= 50pF

4.5

-

48

-

60

-

72

ns

An, Bn to Sn

t

PLH

, t

PHL

C

L

= 15pF

5

-

21

-

-

-

-

-

ns

C

L

= 50pF

4.5

-

49

-

61

-

74

ns

Output Transition Time

t

TLH

, t

THL

C

L

= 50pF

4.5

-

15

-

19

-

22

ns

Switching Specifications

Input t

r

, t

f

= 6ns (Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO

85

o

C

-55

o

C TO

125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

CD54HC283, CD74HC283, CD54HCT283, CD74HCT283

5

Input Capacitance

C

IN

-

-

-

-

10

-

10

-

10

pF

Power Dissipation

Capacitance, (Notes 3, 4)

C

PD

-

5

-

82

-

-

-

-

-

pF

NOTES:

3. C

PD

is used to determine the dynamic power consumption, per package.

4. P

D

= V

CC

2

f

i

(C

PD

+ C

L

) where: f

i

= Input Frequency, C

L

= Output Load Capacitance, V

CC

= Supply Voltage.

Switching Specifications

Input t

r

, t

f

= 6ns (Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO

85

o

C

-55

o

C TO

125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

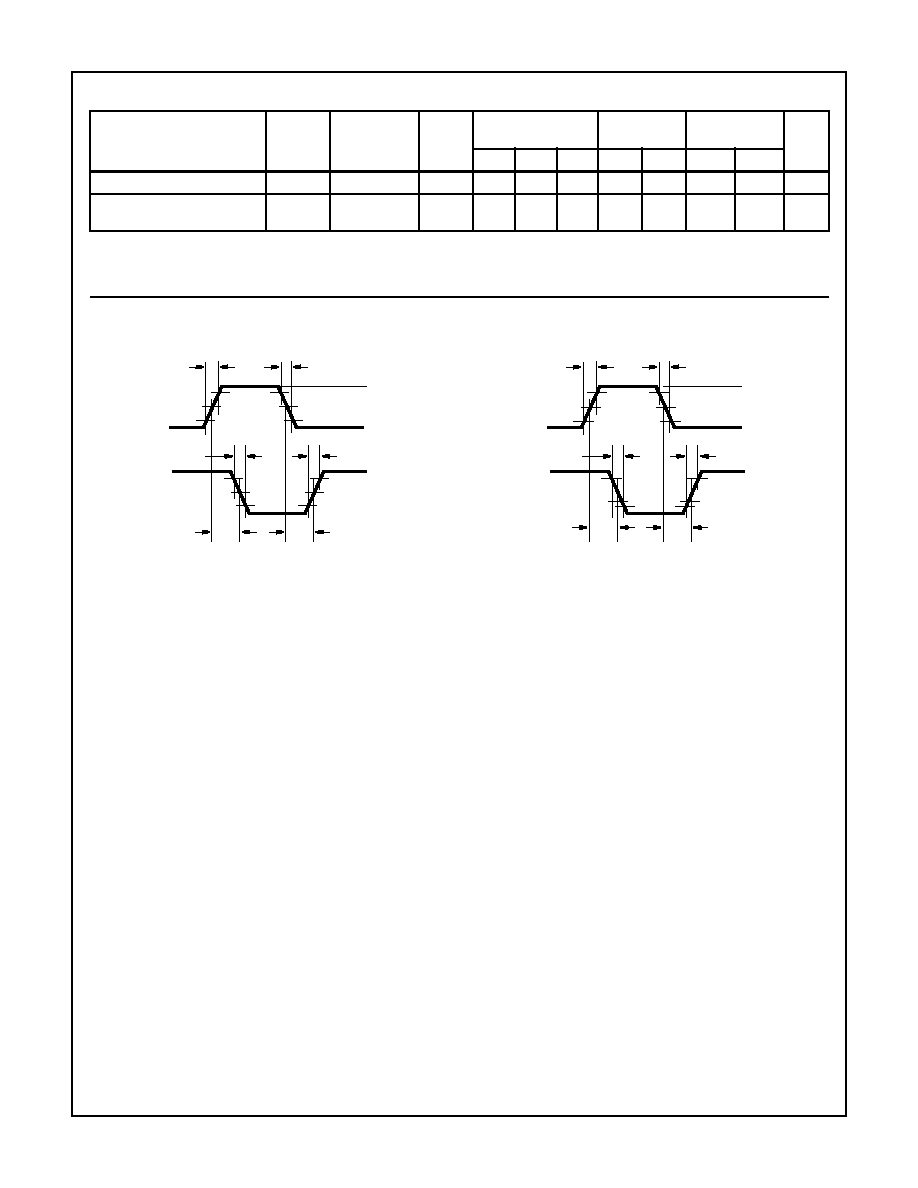

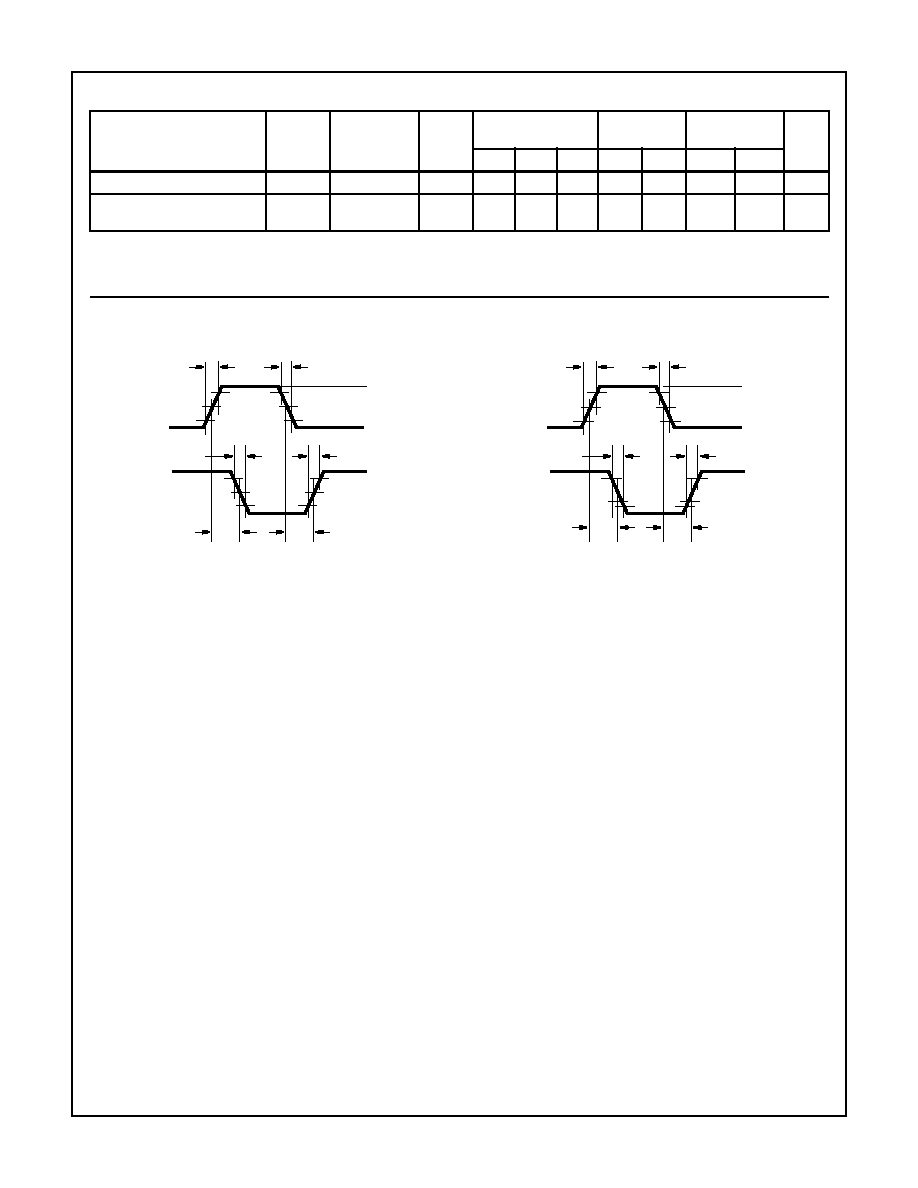

Test Circuits and Waveforms

FIGURE 1. HC AND HCU TRANSITION TIMES AND PROPAGA-

TION DELAY TIMES, COMBINATION LOGIC

FIGURE 2. HCT TRANSITION TIMES AND PROPAGATION

DELAY TIMES, COMBINATION LOGIC

t

PHL

t

PLH

t

THL

t

TLH

90%

50%

10%

50%

10%

INVERTING

OUTPUT

INPUT

GND

V

CC

t

r

= 6ns

t

f

= 6ns

90%

t

PHL

t

PLH

t

THL

t

TLH

2.7V

1.3V

0.3V

1.3V

10%

INVERTING

OUTPUT

INPUT

GND

3V

t

r

= 6ns

t

f

= 6ns

90%

CD54HC283, CD74HC283, CD54HCT283, CD74HCT283