1/10

PRODUCT PREVIEW

October 2005

This is a preliminary information on a new product now in development. Details are subjet to change without notice

STL100NH3LL

N-CHANNEL 30V - 0.0032

- 25A PowerFLATTM (6x5)

STripFETTM III MOSFET

Table 1: General Features

TYPICAL R

DS

(on) = 0.0032

@ 10V

IMPROVED DIE-TO-FOOTPRINT RATIO

VERY LOW PROFILE PACKAGE (1mm MAX)

VERY LOW THERMAL RESISTANCE

CONDUCTION LOSSES REDUCED

SWITCHING LOSSES REDUCED

DESCRIPTION

The STL100NH3LL utilizes the latest advanced

design rules of ST's proprietary STripFETTM Tech-

nology. This process complete to unique metalliza-

tion technique realised the most advanced low

voltage MOSFET in PowerFLAT(6x5). The Chip-

scaled PowerFLATTM package allows a significant

board space saving, still boosting the perfor-

mance.

APPLICATIONS

HIGH-EFFICIENCY DC-DC CONVERTERS

SYNCHRONOUS RECTIFICATION

Table 2: Order Codes

Figure 1: Package

Figure 2: Internal Schematic Diagram

TYPE

V

DSS

R

DS(on)

I

D

STL100NH3LL

30 V

< 0.0035

25 A (1)

PowerFLAT (6x5)

SALES TYPE

MARKING

PACKAGE

PACKAGING

STL100NH3LL

L100NH3LL

PowerFLATTM( 6x5 )

TAPE & REEL

Rev. 4

STL100NH3LL

2/10

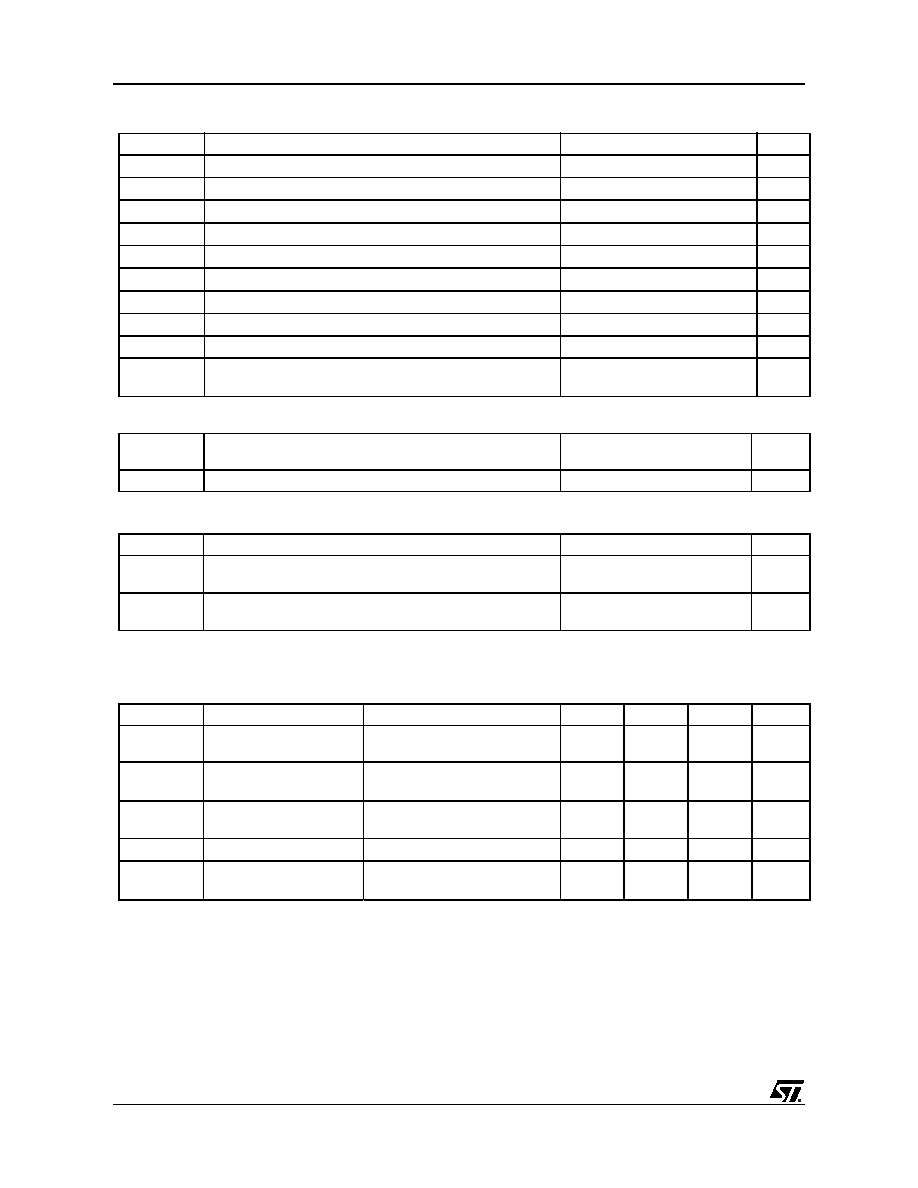

Table 3: Absolute Maximum ratings

Table 4: Thermal Data

Table 5: Avalanche Characteristics

ELECTRICAL CHARACTERISTICS (T

CASE

=25°C UNLESS OTHERWISE SPECIFIED)

Table 6: On/Off

Symbol

Parameter

Value

Unit

V

DS

Drain-source Voltage (V

GS

= 0)

30

V

V

GS

Gate- source Voltage

±16

V

I

D

(2)

Drain Current (continuous) at T

C

= 25°C

100

A

I

D

Drain Current (continuous) at T

C

= 100°C

15.6

A

I

DM

(3)

Drain Current (pulsed)

100

A

I

D

(1)

Drain Current (continuous) at T

C

= 25°C

25

A

P

TOT

(2)

Total Dissipation at T

C

= 25°C

80

W

P

TOT

(1)

Total Dissipation at T

C

= 25°C

4

W

Derating Factor

0.03

W/°C

T

stg

T

j

Storage Temperature

Operating Junction Temperature Range

-55 to 150

°C

Rthj-

C

Thermal Resistance Junction-case ( Drain)

(Steady State)

1.56

°C/W

Rthj-pcb (4)

Thermal Operating Junction-pcb

31.3

°C/W

Symbol

Parameter

Max Value

Unit

I

AV

Not-Repetitive Avalanche Current

(pulse width limited by T

j

max)

12.5

A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25 °C, I

D

= I

AV

, V

DD

= 24 V)

1.3

J

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250 µA, V

GS

= 0

30

V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating, T

C

= 125 °C

1

10

µA

µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ± 16V

±100

nA

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

, I

D

= 250 µA

1

V

R

DS(on)

Static Drain-source On

Resistance

V

GS

= 10V, I

D

= 12.5 A

V

GS

= 4.5V, I

D

=12.5 A

0.0032

0.004

0.0035

0.005

3/10

STL100NH3LL

ELECTRICAL CHARACTERISTICS (CONTINUED)

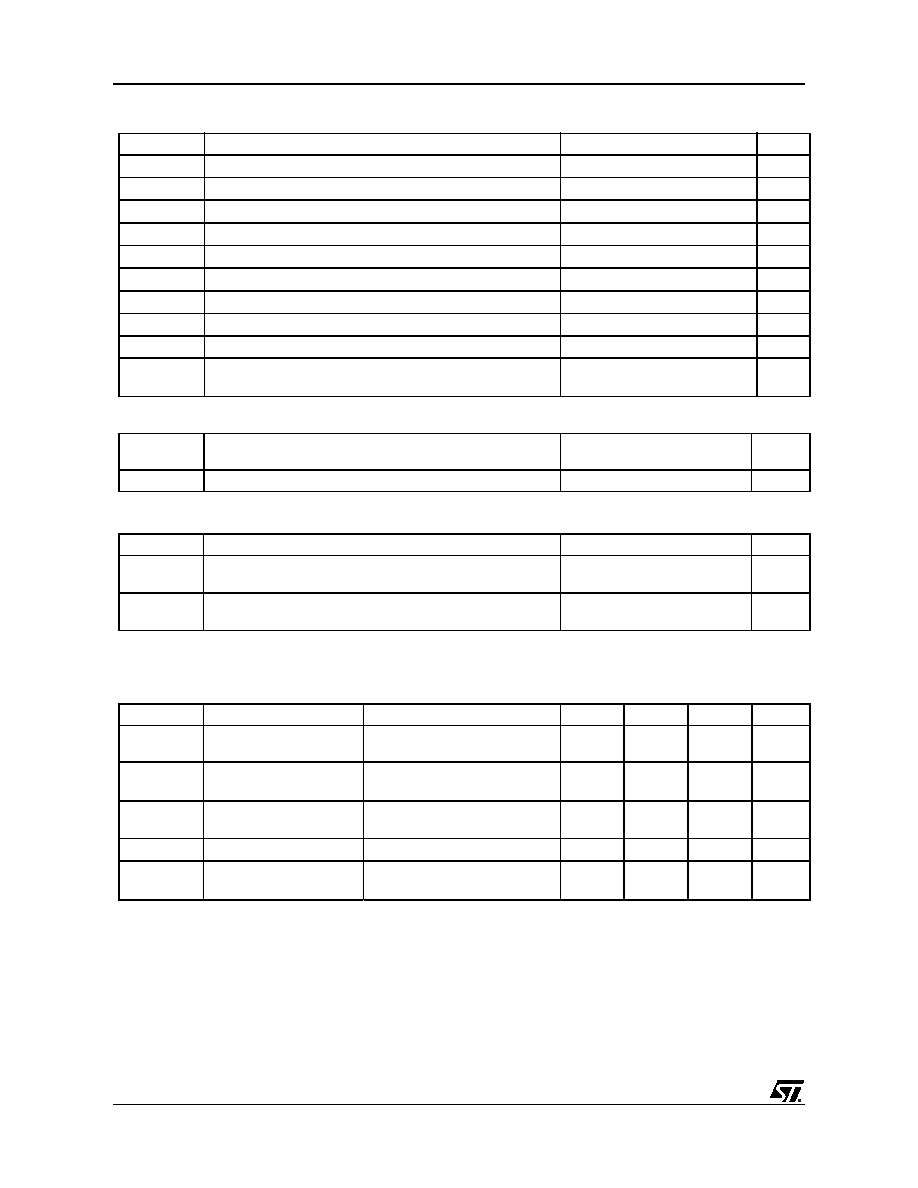

Table 7: Dynamic

Table 8: Source Drain Diode

Note:

(1)The value is according R

thj-pcb

(2)The value is according R

thj-c

(3) Pulse width limited by safe operating area.

(4) When mounted on FR-4 board of 1 in

2

, 2oz Cu, t < 10 sec

(5) Pulsed: Pulse duration = 300

µs, duty cycle 1.5%

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

g

fs

(5)

Forward Transconductance

V

DS

= 10 V

,

I

D

=12,5 A

30

S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

DS

= 25V, f = 1 MHz, V

GS

= 0

4450

655

50

pF

pF

pF

t

d(on)

t

r

t

d(off)

t

r

Turn-on Delay Time

Rise Time

Turn-off Delay Time

Fall Time

V

DD

= 15 V, I

D

= 12.5 A,

R

G

= 4.7

V

GS

= 10 V

(see Figure 15)

18

50

75

8

ns

ns

ns

ns

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

= 15V, I

D

= 25 A,

V

GS

= 4.5V

(see Figure 17)

30

12.5

10

40

nC

nC

nC

R

G

Gate Input Resistance

f=1 MHz Gate DC Bias = 0

Test Signal Level = 20mV

Open Drain

1

2

3

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

I

SD

I

SDM

(3)

Source-drain Current

Source-drain Current (pulsed)

25

100

A

A

V

SD

(4)

Forward On Voltage

I

SD

= 25 A, V

GS

= 0

1.3

V

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

SD

= 25 A, di/dt = 100A/µs

V

DD

= 25 V, T

j

= 150°C

(see test circuit, Figure 16)

32

34

2.1

ns

nC

A

STL100NH3LL

4/10

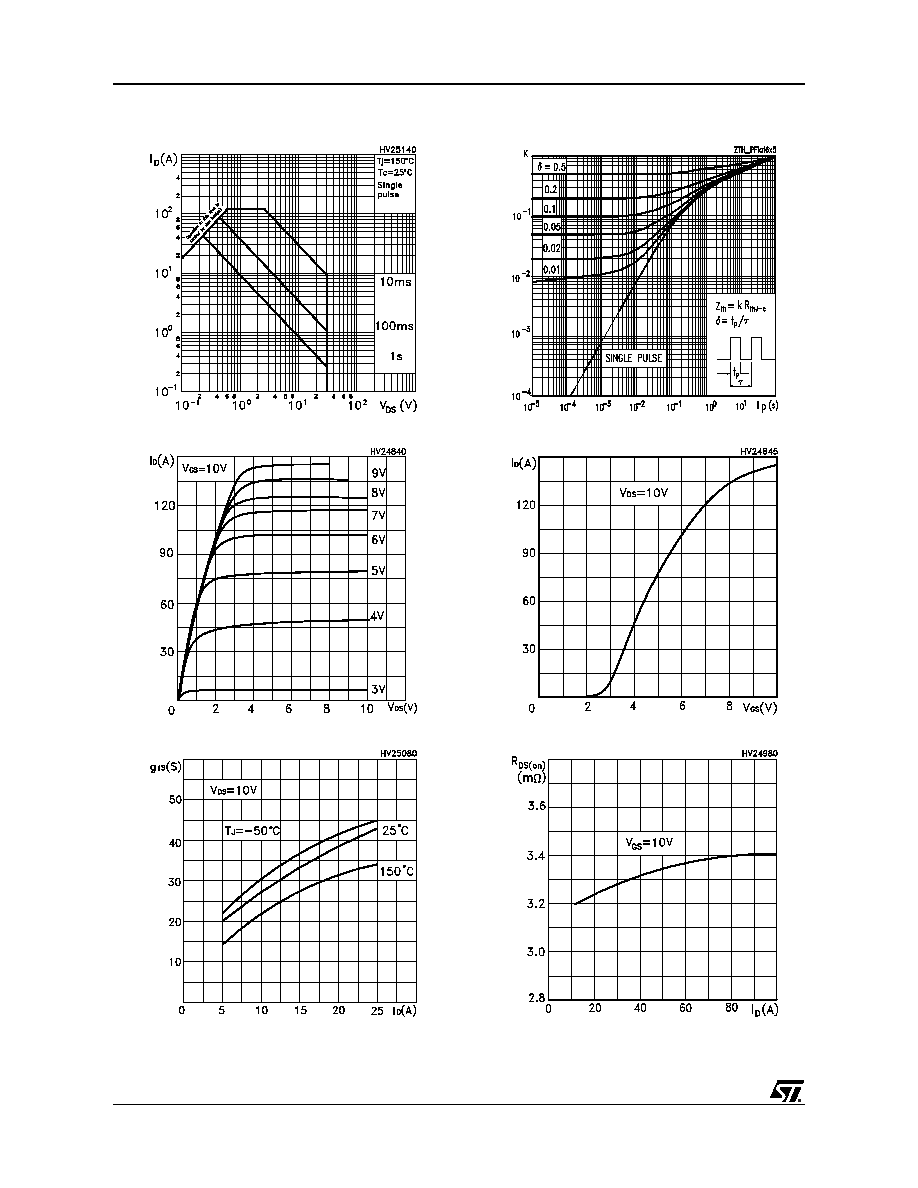

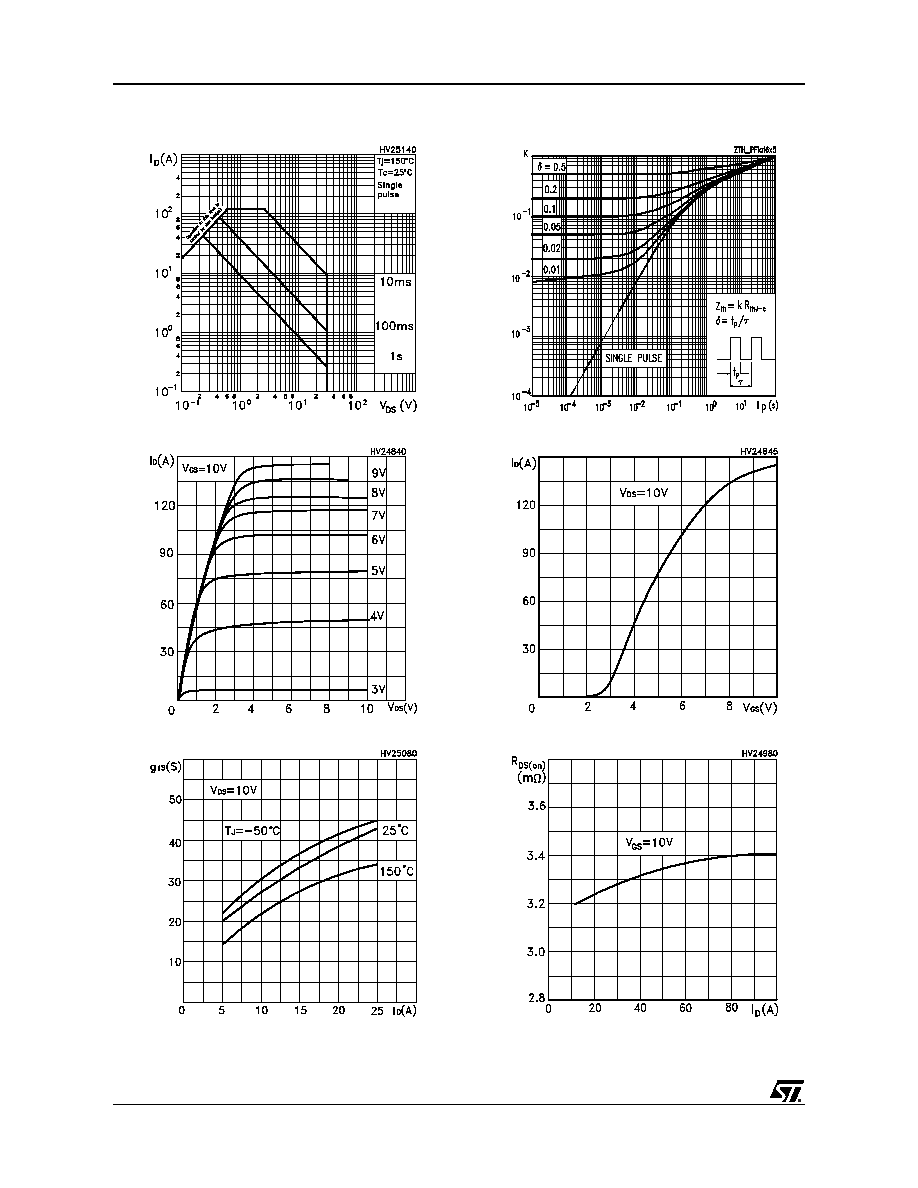

Figure 3: Safe Operating Area

Figure 4: Output Characteristics

Figure 5: Transconductance

Figure 6: Thermal Impedance

Figure 7: Transfer Characteristics

Figure 8: Static Drain-source On Resistance

5/10

STL100NH3LL

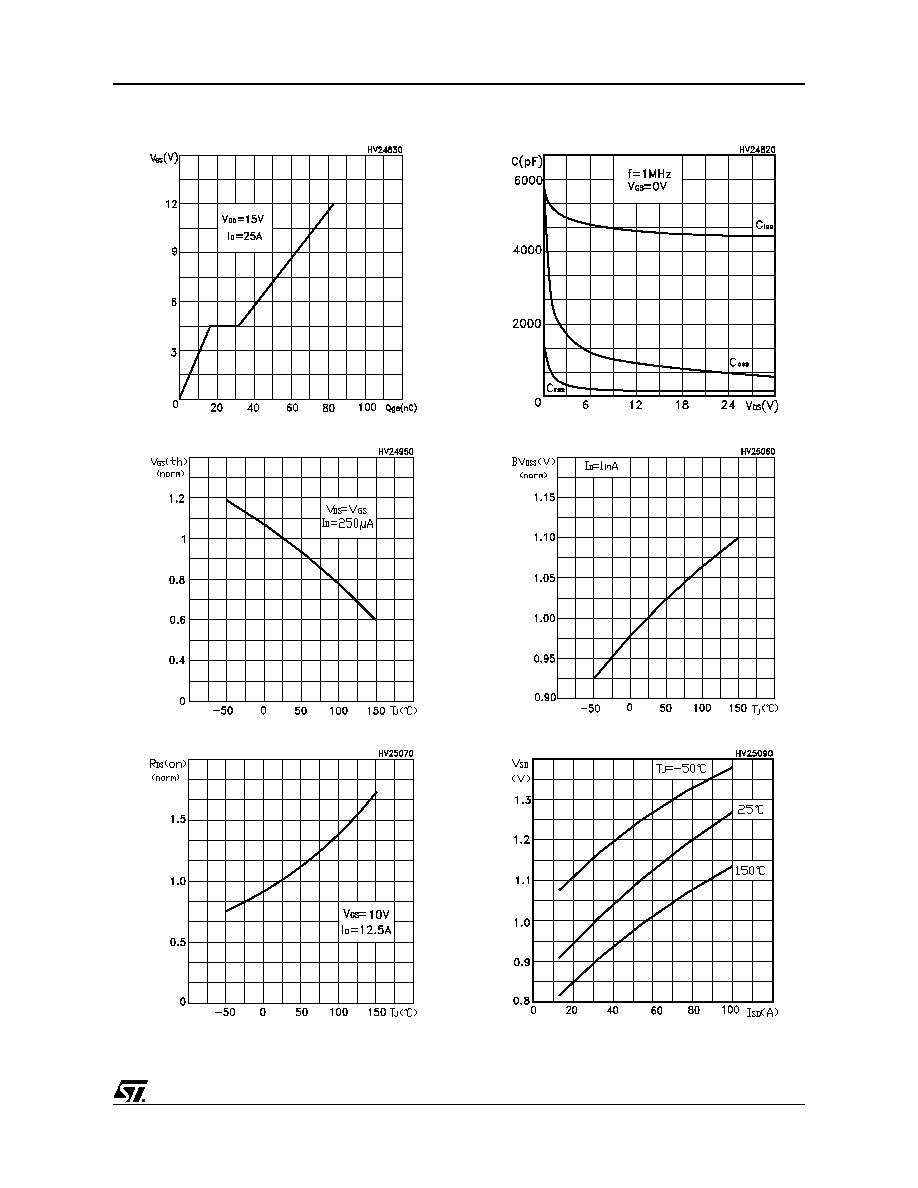

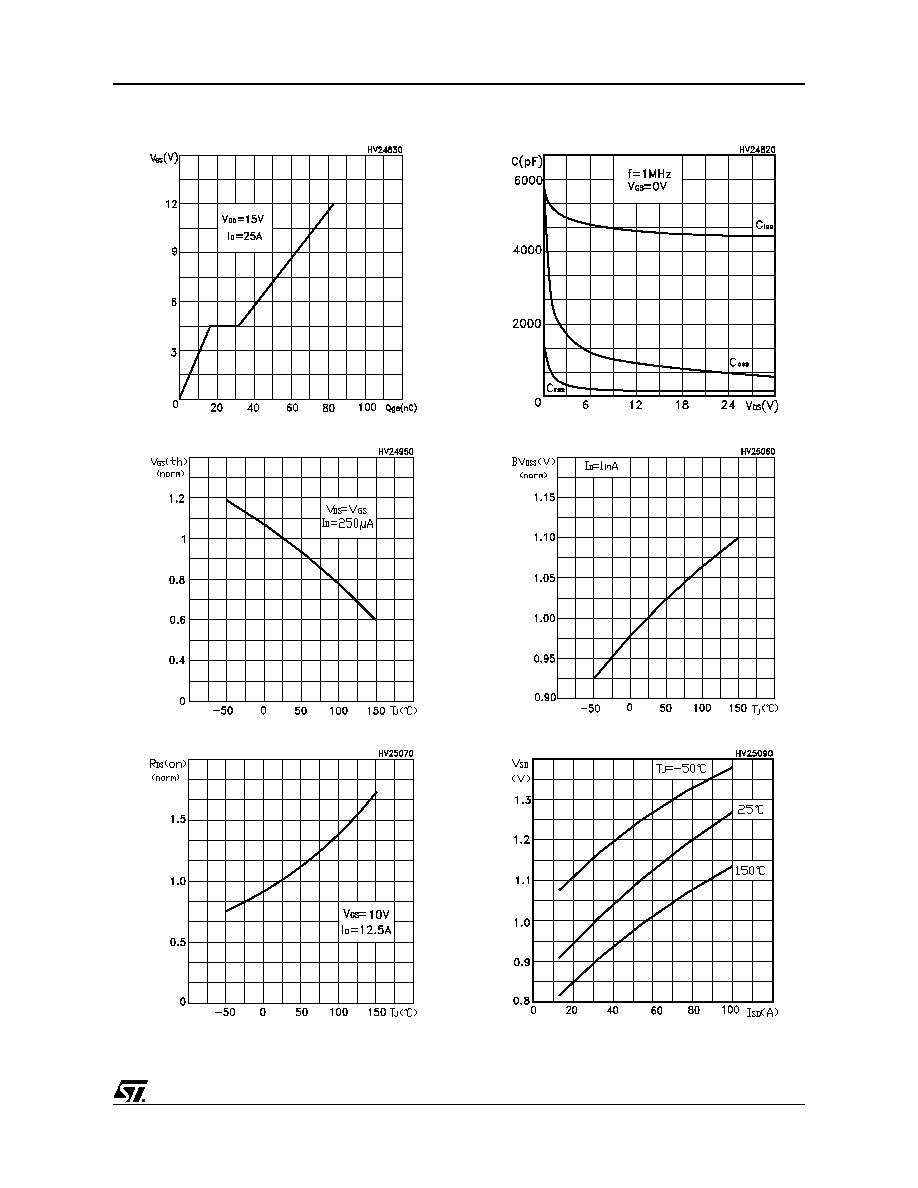

Figure 9: Gate Charge vs Gate-source Voltage

Figure 10: Normalized Gate Thereshold Volt-

age vs Temperature

Figure 11: Normalized On Resistance vs Tem-

perature

Figure 12: Capacitance Variations

Figure 13: Normalized BVDSS vs Temperature

Figure 14: Source-Drain Diode Forward Char-

acteristics