1/8

PRELIMINARY DATA

June 2003

STD7NS20

STD7NS20-1

N-CHANNEL 200V - 0.35

- 7A DPAK / IPAK

MESH OVERLAYTM MOSFET

s

TYPICAL R

DS

(on) = 0.35

s

EXTREMELY HIGH dv/dt CAPABILITY

s

100% AVALANCHE TESTED

s

VERY LOW INTRINSIC CAPACITANCES

s

ADD SUFFIX "T4" FOR ORDERING IN TAPE &

REEL

DESCRIPTION

Using the latest high voltage MESH OVERLAYTM

process, STMicroelectronics has designed an ad-

vanced family of power MOSFETs with outstanding

performance. The new patented STrip layout cou-

pled with the Company's proprietary edge termina-

tion structure, makes it suitable in coverters for

lighting applications.

APPLICATIONS

s

HIGH CURRENT, HIGH SPEED SWITCHING

s

SWITH MODE POWER SUPPLIES (SMPS)

s

DC-DC CONVERTERS FOR TELECOM,

INDUSTRIAL, AND LIGHTING EQUIPMENT

ABSOLUTE MAXIMUM RATINGS

(�)Pulse width limited by safe operating area

TYPE

V

DSS

R

DS(on)

I

D

STD7NS20

STD7NS20-1

200 V

200 V

< 0.40

< 0.40

7 A

7 A

Symbol

Parameter

Value

Unit

V

DS

Drain-source Voltage (V

GS

= 0)

200

V

V

DGR

Drain-gate Voltage (R

GS

= 20 k

)

200

V

V

GS

Gate- source Voltage

� 20

V

I

D

Drain Current (continuos) at T

C

= 25�C

7

A

I

D

Drain Current (continuos) at T

C

= 100�C

4.4

A

I

DM

( )

Drain Current (pulsed)

28

A

P

TOT

Total Dissipation at T

C

= 25�C

45

W

Derating Factor

0.37

W/�C

dv/dt (1)

Peak Diode Recovery voltage slope

5

V/ns

T

stg

Storage Temperature

�65 to 150

�C

T

j

Max. Operating Junction Temperature

150

�C

(1) I

SD

7A, di/dt

300 A/

�

s, V

DD

V

(BR)DSS

, Tj

T

jMAX

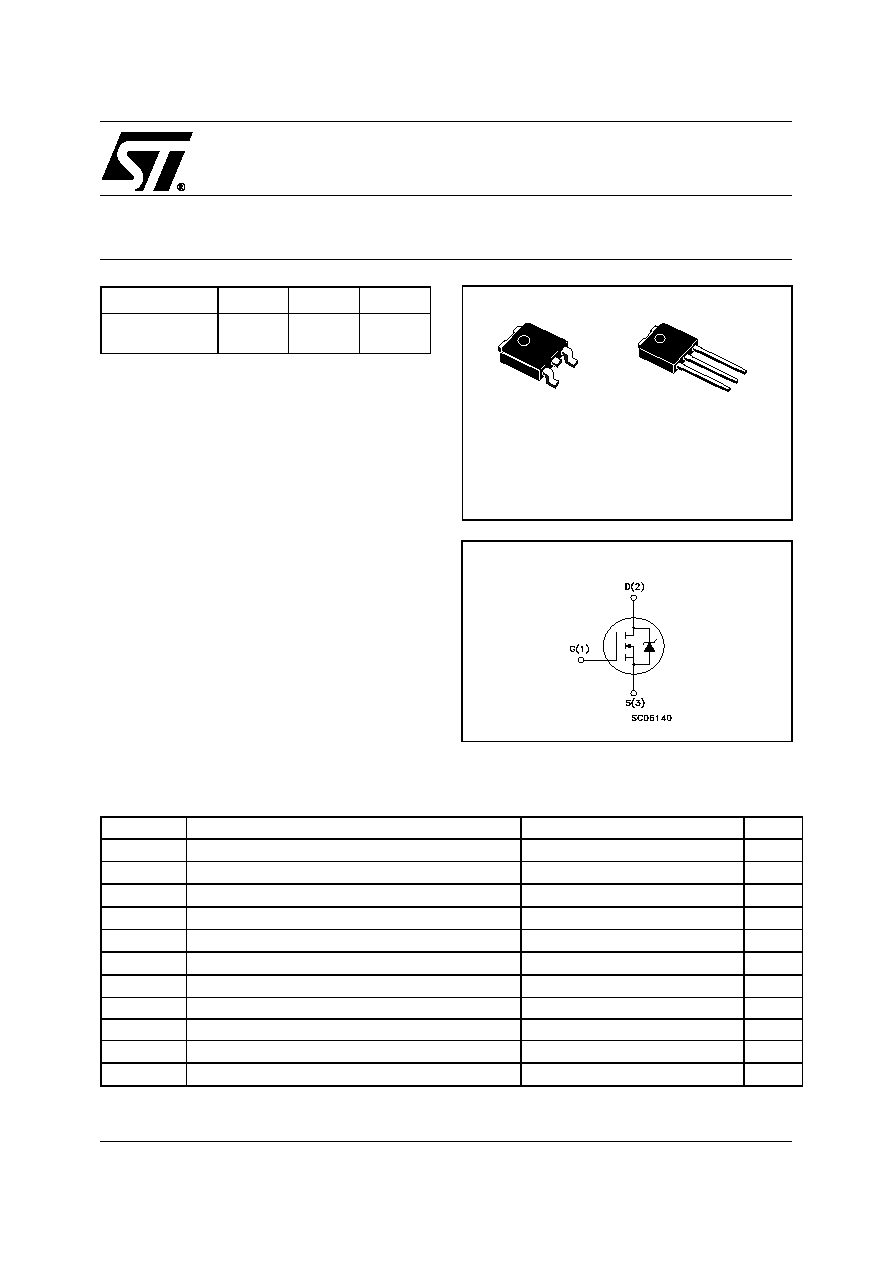

INTERNAL SCHEMATIC DIAGRAM

1

3

TO-252

DPAK

3

2

1

IPAK

TO-251

STD7NS20 / STD7NS20-1

2/8

THERMAL DATA

AVALANCHE CHARACTERISTICS

ELECTRICAL CHARACTERISTICS (TCASE = 25 �C UNLESS OTHERWISE SPECIFIED)

OFF

ON (1)

DYNAMIC

Rthj-case

Thermal Resistance Junction-case Max

2.7

�C/W

Rthj-amb

Thermal Resistance Junction-ambient Max

100

�C/W

T

l

Maximum Lead Temperature For Soldering Purpose

275

�C

Symbol

Parameter

Max Value

Unit

I

AR

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

j

max)

7

A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25 �C, I

D

= I

AR

, V

DD

= 50 V)

60

mJ

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250 �A, V

GS

= 0

200

V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

1

�A

V

DS

= Max Rating, T

C

= 125 �C

10

�A

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= �20V

�100

nA

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

, I

D

= 250�A

2

3

4

V

R

DS(on)

Static Drain-source On

Resistance

V

GS

= 10V, I

D

= 3.5 A

0.35

0.40

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

g

fs

(1)

Forward Transconductance

V

DS

> I

D(on)

x R

DS(on)max,

I

D

= 3.5 A

4

S

C

iss

Input Capacitance

V

DS

= 25V, f = 1 MHz, V

GS

= 0

540

pF

C

oss

Output Capacitance

90

pF

C

rss

Reverse Transfer

Capacitance

35

pF

3/8

STD7NS20 / STD7NS20-1

ELECTRICAL CHARACTERISTICS (CONTINUED)

SWITCHING ON

SWITCHING OFF

SOURCE DRAIN DIODE

Note: 1. Pulsed: Pulse duration = 300 �s, duty cycle 1.5 %.

2. Pulse width limited by safe operating area.

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

t

d(on)

Turn-on Delay Time

V

DD

= 100 V, I

D

= 3.5 A

R

G

= 4.7

V

GS

= 10 V

(see test circuit, Figure 3)

10

ns

t

r

Rise Time

15

ns

Q

g

Total Gate Charge

V

DD

= 160V, I

D

= 18 A,

V

GS

= 10V

31

45

nC

Q

gs

Gate-Source Charge

7.5

nC

Q

gd

Gate-Drain Charge

9

nC

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

t

r(Voff)

t

f

t

c

Off-voltage Rise Time

Fall Time

Cross-over Time

V

clamp

= 160 V, I

D

= 7 A,

R

G

= 4.7

,

V

GS

= 10V

(see test circuit, Figure 5)

12

12

25

ns

ns

ns

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

I

SD

Source-drain Current

7

A

I

SDM

(2)

Source-drain Current (pulsed)

28

A

V

SD

(1)

Forward On Voltage

I

SD

= 7 A, V

GS

= 0

1.5

V

t

rr

Reverse Recovery Time

I

SD

= 7 A, di/dt = 100A/�s

V

DD

= 50V, T

j

= 150�C

(see test circuit, Figure 5)

170

ns

Q

rr

Reverse Recovery Charge

0.95

�

C

I

RRM

Reverse Recovery Current

11

A

STD7NS20 / STD7NS20-1

4/8

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

Fig. 4: Gate Charge test Circuit

Fig. 2: Unclamped Inductive Waveform

Fig. 1: Unclamped Inductive Load Test Circuit

Fig. 3: Switching Times Test Circuit For

Resistive Load

5/8

STD7NS20 / STD7NS20-1

DIM.

mm

inch

MIN.

TYP.

MAX.

MIN.

TYP.

MAX.

A

2.20

2.40

0.087

0.094

A1

0.90

1.10

0.035

0.043

A2

0.03

0.23

0.001

0.009

B

0.64

0.90

0.025

0.035

B2

5.20

5.40

0.204

0.213

C

0.45

0.60

0.018

0.024

C2

0.48

0.60

0.019

0.024

D

6.00

6.20

0.236

0.244

E

6.40

6.60

0.252

0.260

G

4.40

4.60

0.173

0.181

H

9.35

10.10

0.368

0.398

L2

0.8

0.031

L4

0.60

1.00

0.024

0.039

V2

0

o

8

o

0

o

0

o

P032P_B

TO-252 (DPAK) MECHANICAL DATA