DATABRIEF

January 2006

1/11

Rev. 2

®

STD2000

Single-Chip Worldwide iDTV Processor

Dual-Channel High Definition Video

Processor

Up to 12-bit Video Processing

3D Digital Luma/Chroma Noise Reduction

3D Motion Adaptive Pixel-based Advanced

Deinterlacing with Diagonal Compensation

Contour Sensitive De-interlacing CSDiTM

Flexible H/V Scaling Engine with Multi Window

management capabilities

Image Quality Improvement Engine for crystal

clear and crisp pictures

Dual Digital Chroma Decoder

(PAL/SECAM/NTSC) with 3D/2D Comb Filter

and Dual VBI Data Slicer

Powerful 32-bit RISC ST40 CPU (266 MHz,

480 MIPS)

Dual Transport Stream Demux with DES, DVB

and Multi2 Descrambler

Dual DVB-CI/one CableCARDTM interface

MP@ML Dual Channel or MP@HL Single

Channel MPEG-2 Video decoder

24-bit audio DSP Core, MPEG-1 (Layers 1, 2 &

3), MPEG2, Dolby

®

Digital Decoder

Gamma 2D Graphics Engine for Middleware

graphics and On-Screen Display

Auxiliary Video/Graphics Sub-System for

Monitor output

Exhaustive set of peripherals for DTV

Chassis Control

DDR333 Unified Memory Interface (LMI)

Programmable External Memory Interface

(EMI)

CRT and Flat Panel Display Video Outputs

27 MHz Crystal Oscillator

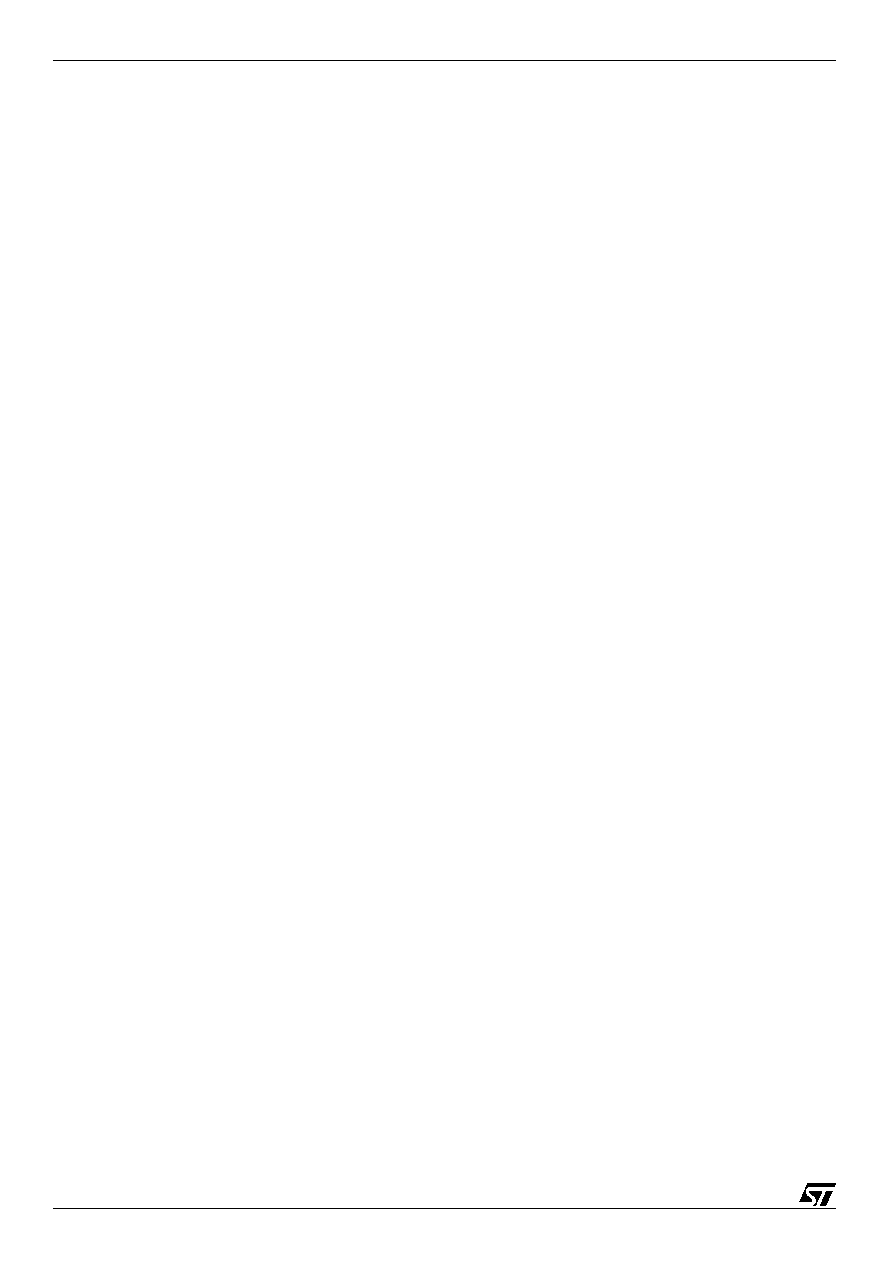

ID Video Display Pipeline (TNR, DEI, Scaling, IQI)

HD Video Display Pipeline (TNR, DEI, Scaling, IQI)

Compos

i

t

or

ST Bus On-Chip Interconnect

Dual

Transport

Demux

MPEG-2

MP@HL

MP@MLx2

Video

Dual C.I. / One CableCardTM

Chassis

Control

TimeBase

Clock

Generator

LMI

EM

I

266 MHz

480 MIPS

16K - I, 32K-D

ST40 CPU

Decoder

H/V SRC

NOR Flash

DDR SDRAM

SD/ID Analog

Video

MPEG-2

Audio & Video

SD/HD Digital

Video

Display

LCD

PDP

Peripherals

VCR

Dual DDEC

3D Comb

DLP

CRT

DVD

Dis

pla

y

Dr

iv

er

Digital

Encoder

Recorder

VBI DMA

Gamma

2D Graphics

Digital

Digital

MPEG 1&2

Dolby

Digital

Audio DSP

Decoder

MP3

Audio In

Audio Out

Graphics

STD2000

2/11

Dual Channel Video Input Processor

Analog Video Inputs

CVBS, Y/C, 1H/2H/2.14H YPrPb, 1H/2H RGB

analog inputs

Digital Video Inputs

D1/HD Digital video input (CCIR 601-656 /

SMPTE 274M, SMPTE 296M, SMPTE 260M)

YCL Digital video input (proprietary port;

YCrCb-4:2:2, 2H for off-chip Motion-

compensated Video Processing)

RGB to YCrCb 4:2:2 conversion

Analog Video Pre-Processing

Dual Digital Chroma Decoder

(PAL/NTSC/SECAM)

3D Comb Filter support on one channel,

adaptative 4H/2D comb filter on second

channel

Dual VBI data slicer for Teletext, CC, WSS

and other systems

3:2/2:2 Pulldown, Video/Movie and Scene

Change Detection

3D Digital Luma and Chroma Motion Adaptive

Noise Reduction

Automatic Letterbox Detection

Dual Channel High Definition Video

Processor

Image Processing

24, 25, 30, 50, 60 to 50, 60, 75, 100, 120 Hz

Field up-rate conversion

3D Motion-adaptive pixel-based advanced

deinterlacing with diagonal compensation

(CSDiTM: Contour Sensitive Desinterlacer)

Image Quality Improvements

LTI and CTI

Contrast Enhancer: Black-White Stretch

Blue Stretch

Green Boost, Auto-Flesh and Tint Control

Peaking: Adaptive Peaking and Coring

Video Scaling & Composition

Horizontal/Vertical Format Conversion

Support of 4:3 and 16:9 display aspect ratios

Zoom In or Zoom out (X and Y independent

linear factors from x0.25 to x4)

Panoramic mode

H or V crop and independent rescaling

Compositor supporting Monochrome and

Graphics planes

Video two-channel HD processing for:

PIP/POP, Picture And Picture (Perfect PAP),

Picture In Graphic (PIG)

Video Output Control

Color Space Translator

(conversion to YCrCb 4:4:4 or RGB coding)

Gamma Correction with programmable any-

curve correction

Perfect Color Engine (spatio-temporal

dithering down to 4-to-8 bits)

RGB 3x10-bit Digital output to flat panel or

DMD

RGB or YUV analog outputs

Color warping for color gammut correction

CPU Sub-System

32-bit RISC ST40 CPU (266 MHz, 480MIPs)

16 Kbytes I-Cache and 32 Kbytes D-Cache

RAM

Floating Point Unit (FPU)

Memory Management Unit (MMU)

On-Chip Memory

(64 Kbytes SRAM)

Services

Test Access Port and its link (JTAG based)

Diagnostic Controller Unit (for low intrusion,

real-time debugging)

Advanced User Debug support

System Bus Analyzer (SBAG)

Dual Transport Stream Processor

Dual Transport Stream Demux

DES, DVB and Multi2 descramblers

Dual Transport processing: DVB or ATSC

(ISO/IEC 13818-x and A53)

DVB-CI interface (Dual Slot support)

CableCARDTM interface (Single Slot support)

3/11

STD2000

MPEG2 Digital Video Decoder

MPEG2 Video (ISO/IEC 13818-2, ATSC-A54)

MP@ML Dual-channel Decode or MP@HL

Single-channel Decode

Data Extraction (closed caption,...)

Digital Audio Decoder

24-bit audio DSP Core (with embedded

Software & Patch RAM)

MPEG1 (layers 1, 2 & 3), MPEG2, Dolby®

Digital / ATSC-A52

Lt/Rt Downmix for standard Stereo digital

outputs

Triple I˛S channel outputs

One PCM/Stream or I˛S Input (S/PDIF

external receiver or HDMI)

S/PDIF Digital Output (IEC60958 and

IEC61937)

Gamma 2D Graphic Processor

Full Screen or windowed Bitmap area

ARGB-4444 Graphics plane in mixed mode

2D-Graphics hardware accelerator

GFx/Video programmable alpha-blending

Background Color Plane

Horizontal and/or Vertical Scrolling, controlled

by software

Auxiliary Video/Graphics Processor

On-chip PAL/NTSC/SECAM Encoder for

monitor output

Encoding of Teletext, WSS, VPS or Closed

Caption

Graphics plane for optional Subtitle support

Macrovision Copy Protection (Factory Disable

option)

DTV Chassis Control

Two UARTs

One Smartcard interface

Two I˛C (2 channels each)

Four-channel PWM with input capture and

compare

Real-time Clock and WatchDog timer

Infrared Receiver/Transmitter

10-bit, 8-channel low-speed A/D Converter

8 external interrupt channels with Interrupt

Level Controller

More than 56 General Purpose IOs

Low-power mode and wake-up controller

Interfaces

Local Memory Interface (LMI)

64-bit, dual-port DDR memory interface

16- and 32-bit DDR-SDRAM device support

Up to 166 MHz support

Support devices of up to 512 Mbits

Programmable External Memory Interface

(EMI)

16-bit/8-bit External Memory Interface for

supporting Flash and optional peripherals

Support NOR Flash devices of up to 256

Mbits

6 separately configurable banks

Support for external memory-mapped ICs or

sub-systems

FDP and CRT Video Outputs

RGB 3x10-bit digital output to flat panel or

DMD

RGB or YUV analog outputs for CRT

General Information

STD2000

4/11

1 General

Information

1.1 Introduction

The STD2000 is a highly-integrated, high performance system-on-chip iDTV processor that

combines Set-top Box decoding facility with a powerful TV processor.

A dual-channel PIP/PAP video processor supports High Definition formats. Its advanced integration

drastically reduces integrated Digital TV BOM costs by removing redundancy between Analog and

Digital source video processing.

Compliant with worldwide standards such as ATSC, DVB-T, ISDB-T and the Chinese Digital

Terrestrial Standard, the STD2000 also includes a built-in CableCARDTM interface for US

OpenCableTM specifications and a dual DVB-CI interface for European DVB-T specifications.

1.2 Typical

Applications

Typical applications for the STD2000 system-on-chip are illustrated in the following diagrams:

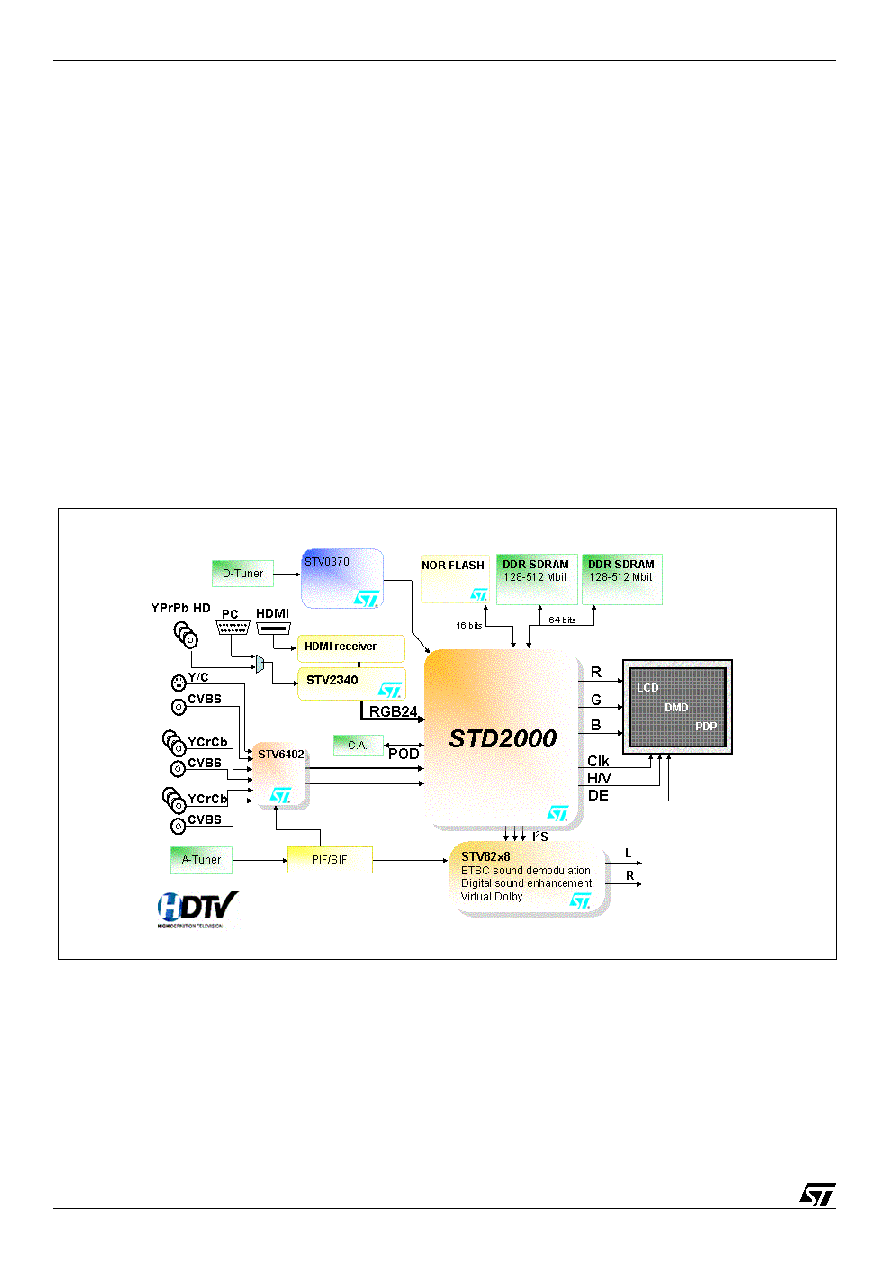

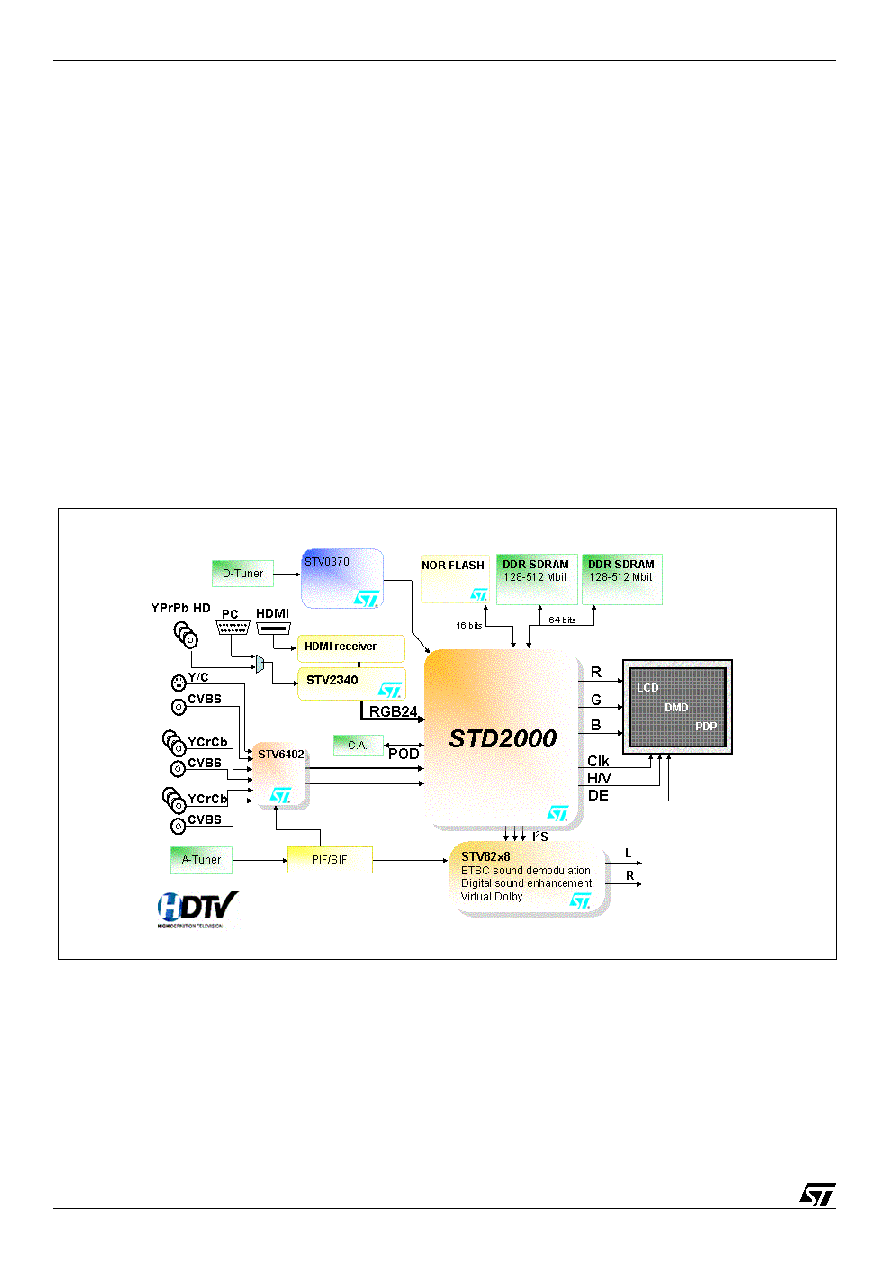

Figure 1: US LCD Digital Cable Ready HDTV

5/11

STD2000 General

Information

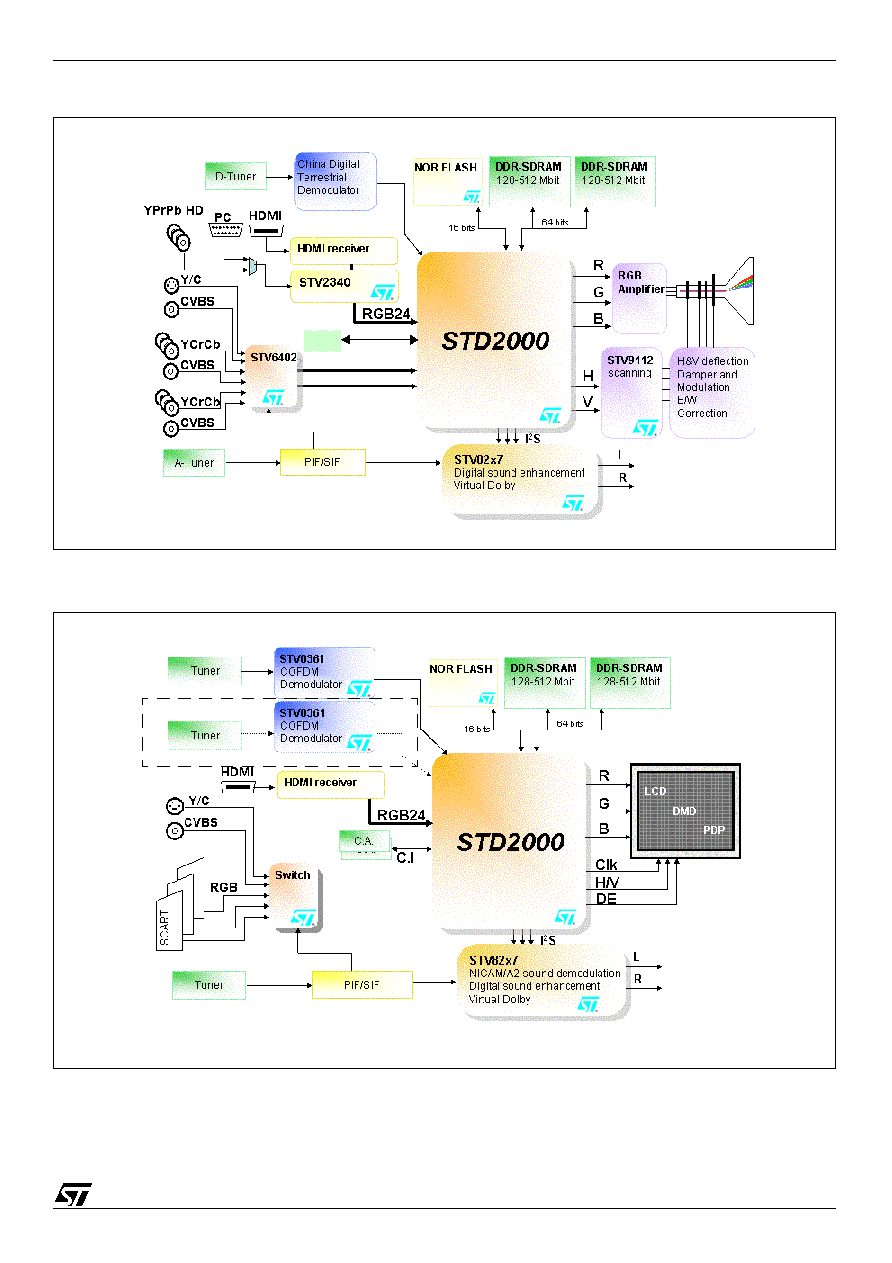

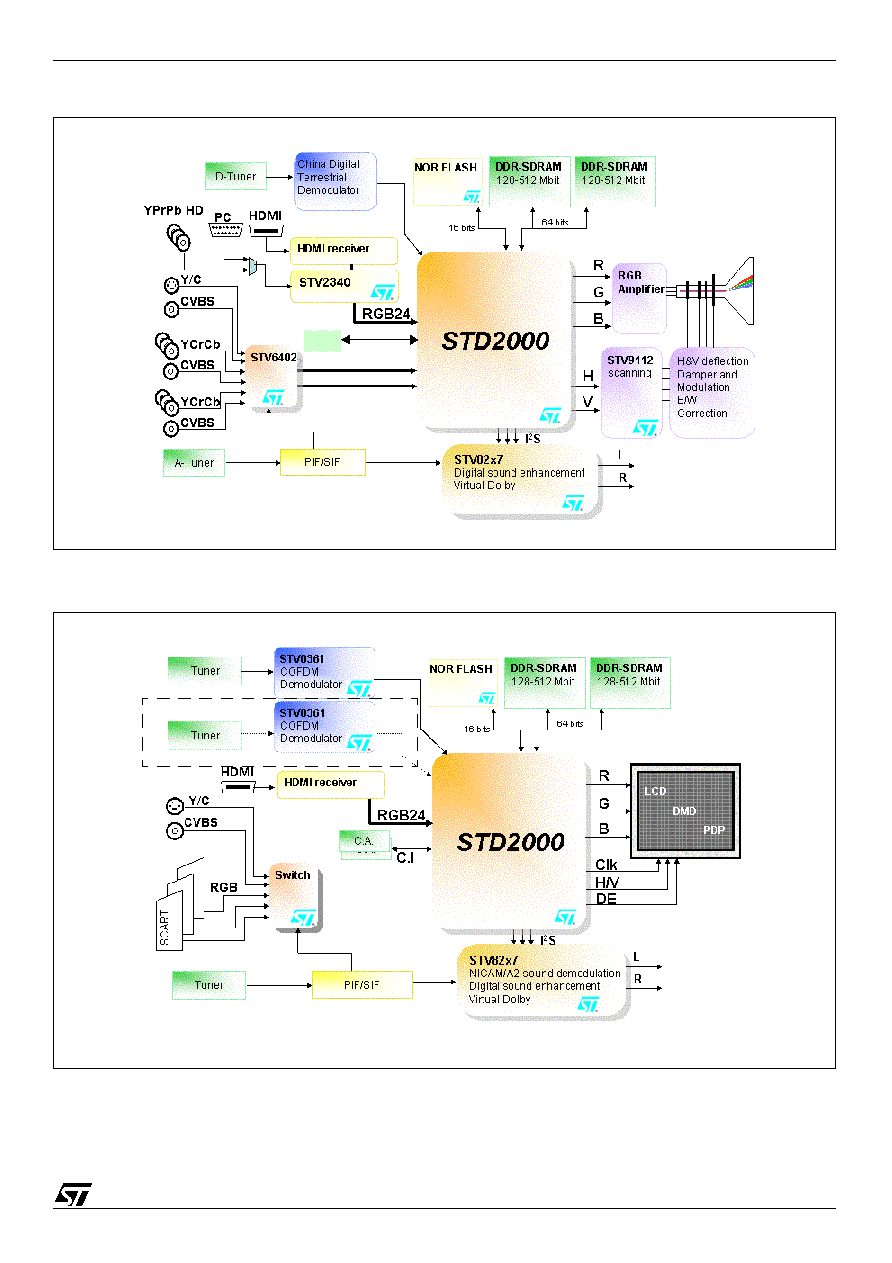

Figure 2: China CRT Digital Cable HDTV

Figure 3: Europe LCD iDTV

CA

Chinese C.I.

Optional