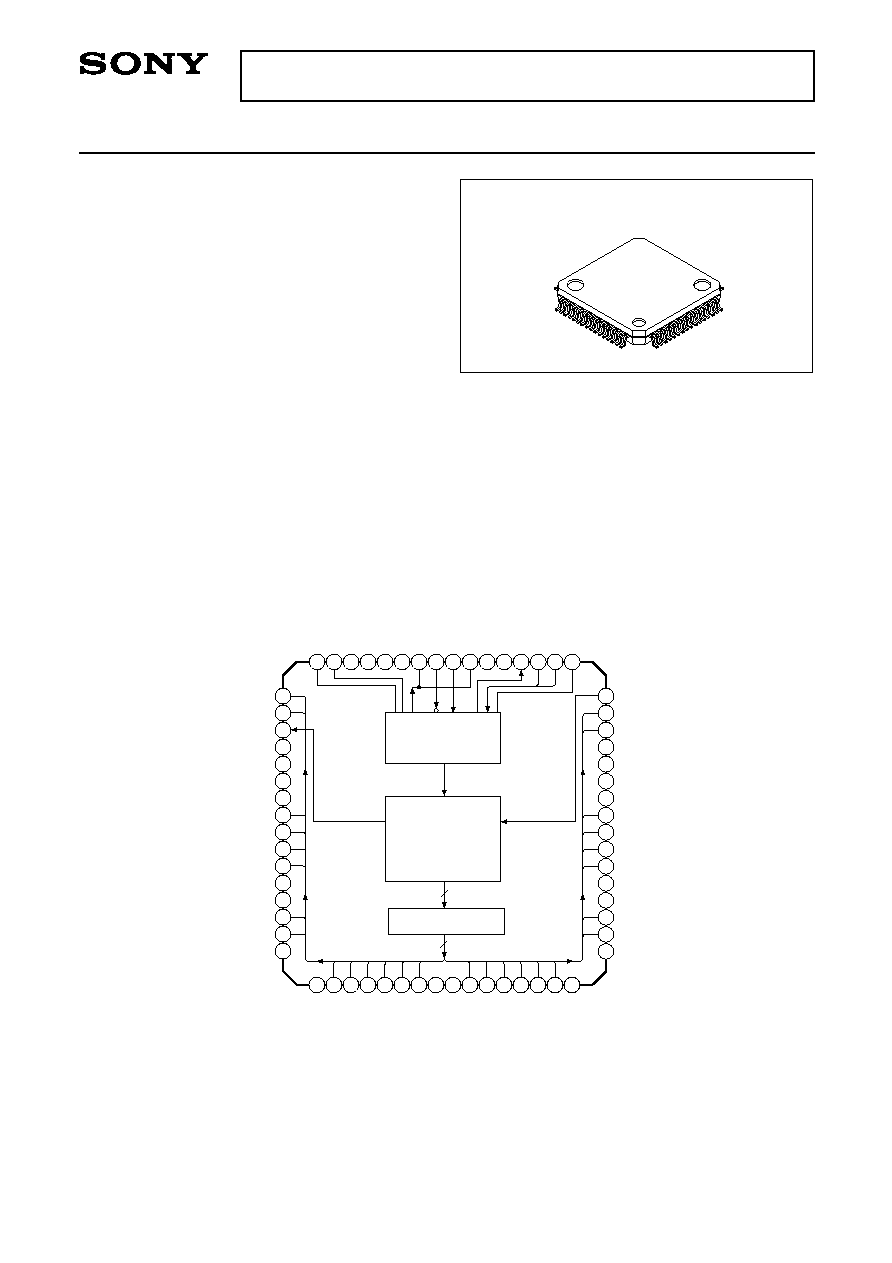

VGA/SVGA/XGA 24-bit Receiver

Description

CXB1456R is the 1 chip deserializer for VGA/SVGA/

XGA 24-bit color digital RGB, and meet to the Gigabit

Video Interface specification.

Features

ñ 1 chip receiver for serial transmission of 24-bit color

VGA/SVGA/XGA picture

ñ On chip PLL circuit for data and clock recovery

ñ On chip panel mode automatically selectable circuit

ñ TTL compatible I/O

ñ Support 1 pixel/shiftclock mode with 1 chip and 2

pixel/shiftclock mode with 2 chip

ñ +3.3V single power supply

ñ Low power consumption

ñ 64pin plastic LQFP package with body size 10mm

æ

10mm

Application

Gigabit video interface

Structure

Bi-CMOS IC

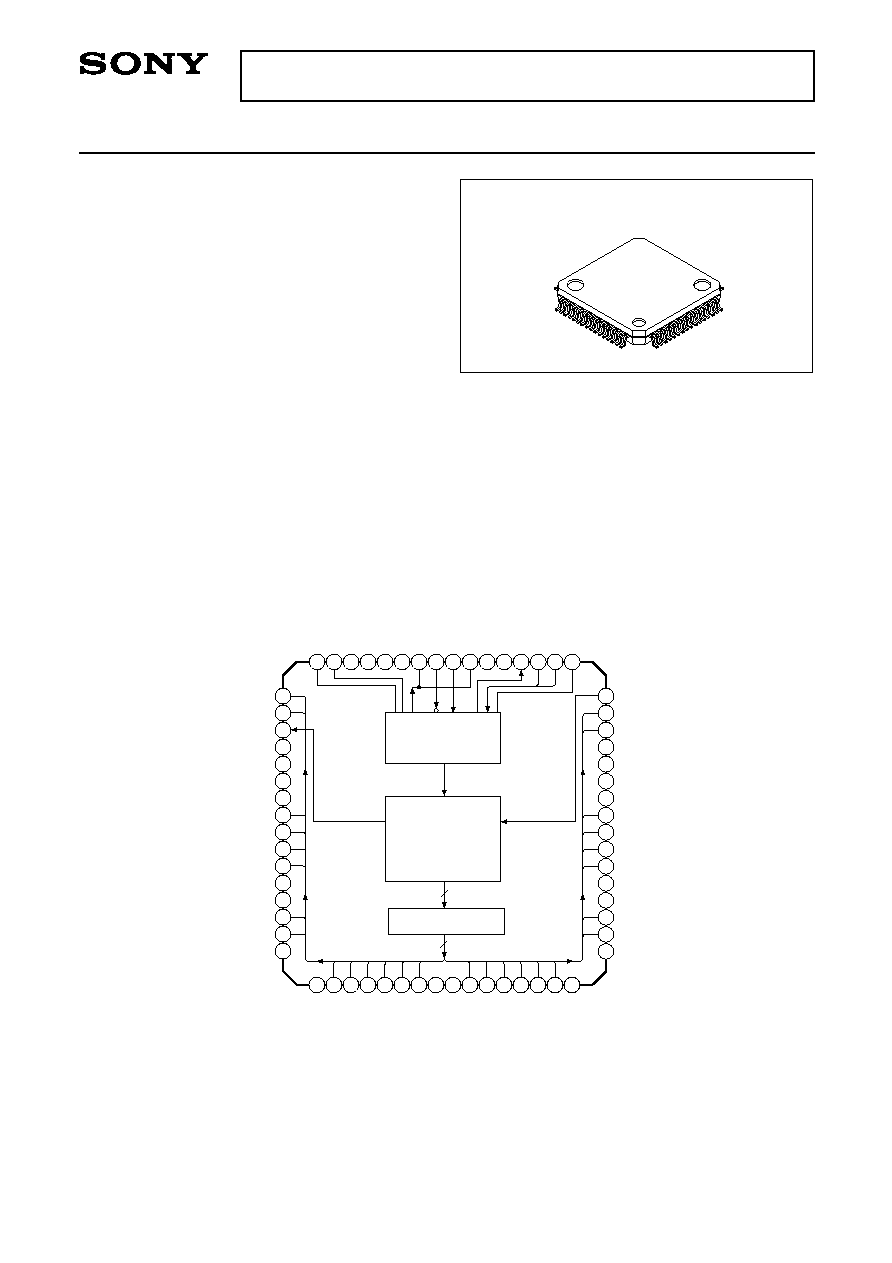

Block Digagram & Pin out

Absolute Maximum Ratings

ñ Supply voltage

Vcc

4.2

V

ñ Storage temperature

Tstg

Ù65 to +150

¯C

ñ Allowable power dissipation

P

D

650

mW

Recommended Operating Condition

ñ Supply voltage

3.3 Ý 0.3

V

ñ Operating temperature Topr

0 to +80

¯C

Ù 1 Ù

E98Y04C9X-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXB1456R

64 pin LQFP (Plastic)

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

REXT

PANEL0

PANEL1

LOS

TESTDT

CE

REFRQP

SDATAP

SDATAN

REFRQN

TESTEXN

V

CC

A

V

EE

A

V

EE

S

LPFA

LPFB

V

DD

G0

G1

G2

G3

G4

G5

GND

V

DD

G6

G7

B0

B1

B2

B3

GND

CLKPOL

R0

R1

GND

V

DD

V

EE

V

CC

R2

R3

R4

R5

GND

V

DD

R6

R7

GND

CNTL

DE

SFTCLK

GND

V

DD

V

EE

V

CC

HSYNC

VSYNC

B7

B6

GND

V

DD

B5

B4

V

DD

Serial

to

Parallel

Converter

Decoder

CDR

PLL

Fig. 1. Block Diagram & Pin out

Ù 2 Ù

CXB1456R

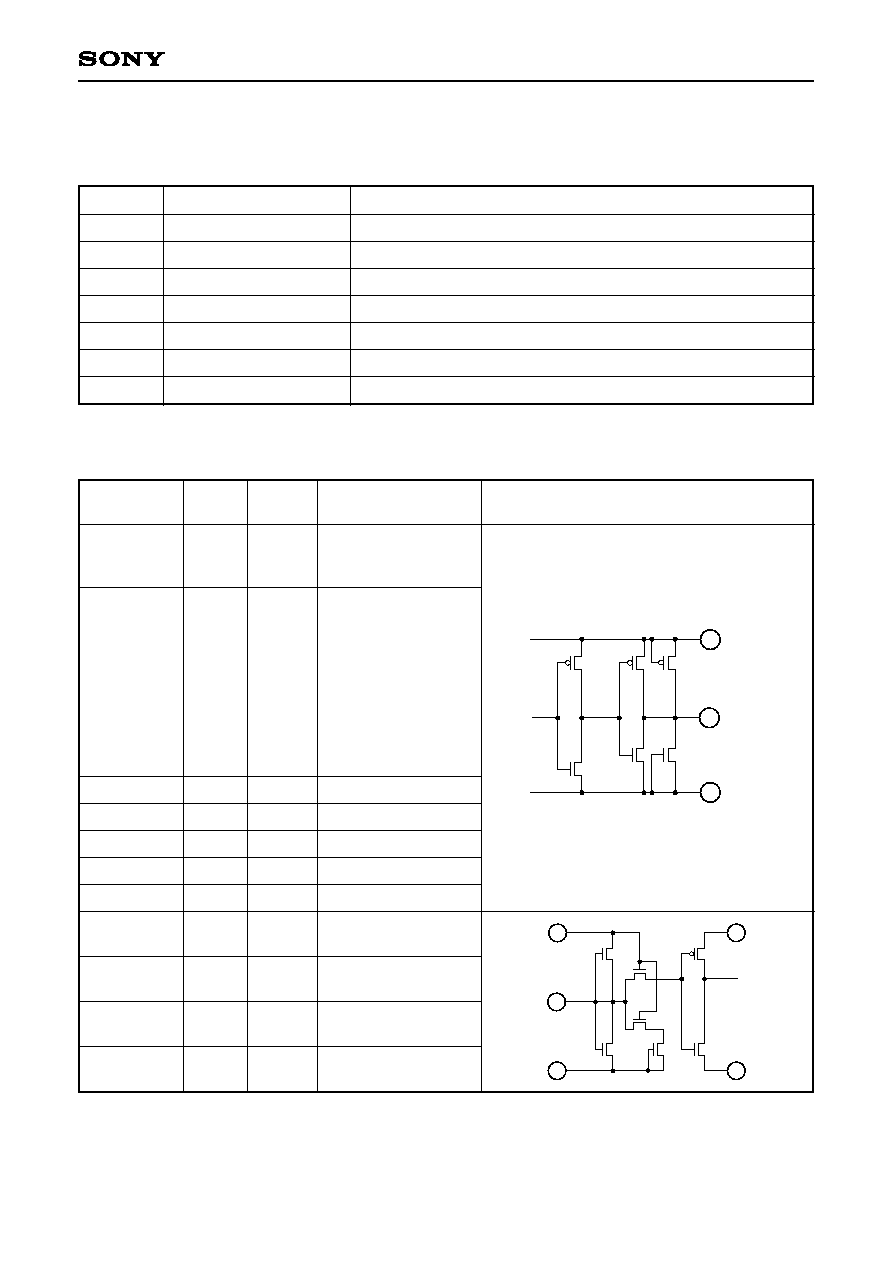

Pin List

Table 1. Power/Ground

Pin name

V

DD

GND

V

CC

V

EE

V

CC

A

V

EE

A

V

EE

S

8, 16, 20, 28, 53, 61, 64

1, 9, 17, 21, 29, 52, 60

26, 55

27, 54

44

45

46

MOS power supply, should be connected to 3.3V Ý 0.3V

MOS ground, connected to 0V

ECL power supply, connected to 3.3V Ý 0.3V

ECL ground, connected to 0V

Analog power supply, connected to 3.3V Ý 0.3V

Analog ground, connected to 0V

Substrate GND, connected to 0V

Pin number

Descriptions

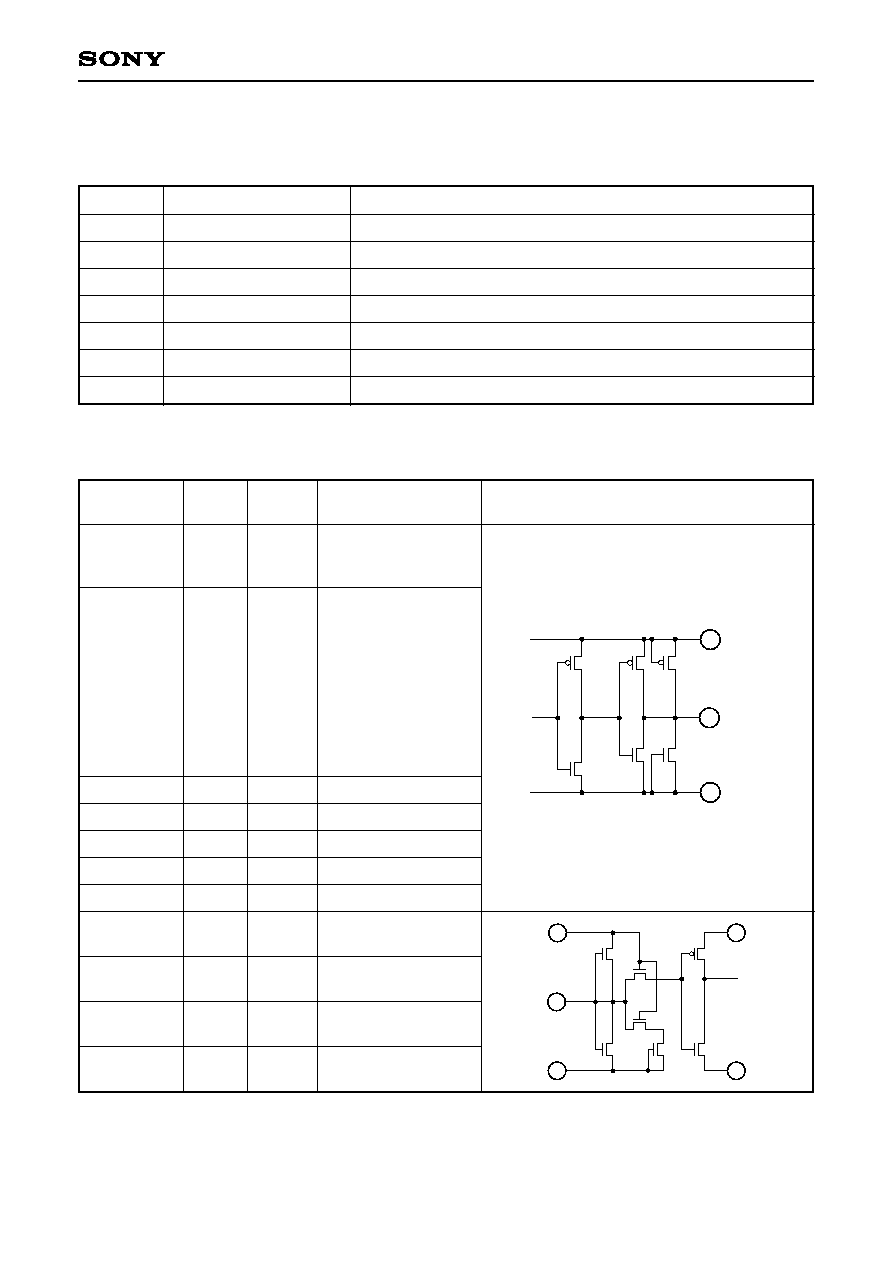

Table 2. Digital Signals

Pin name

SFTCLK

RED (7 to 0)

GRN (7 to 0)

BLU (7 to 0)

HSYNC

VSYNC

CNTL

DE

LOS

PANEL (1, 0)

CLKPOL

CE

TESTEXN

TESTDT

51

18, 19,

22, 23,

24, 25,

30, 31

6, 7, 10,

11, 12,

13, 14, 15

58, 59,

62, 63,

2, 3, 4, 5

56

57

49

50

36

35, 34

32

38

43,

37

TTL out

TTL out

TTL out

TTL out

TTL out

TTL out

TTL out

TTL in

TTL in

TTL in

TTL in

Shift clock, for the

data fetch at falling or

rising edge

Pixel data

Hsync data

Vsync data

Control data

Display enable data

Los of signal

Panel mode select

switch

Trigger edge select

switch

Chip enable

Reversed for TEST

under fabrication

Pin

number

Type

Descriptions

Equivalent circuit

V

DD

GND

V

CC

A

TTL-IN

V

EE

S

V

DD

TTL-OUT

GND

Ù 3 Ù

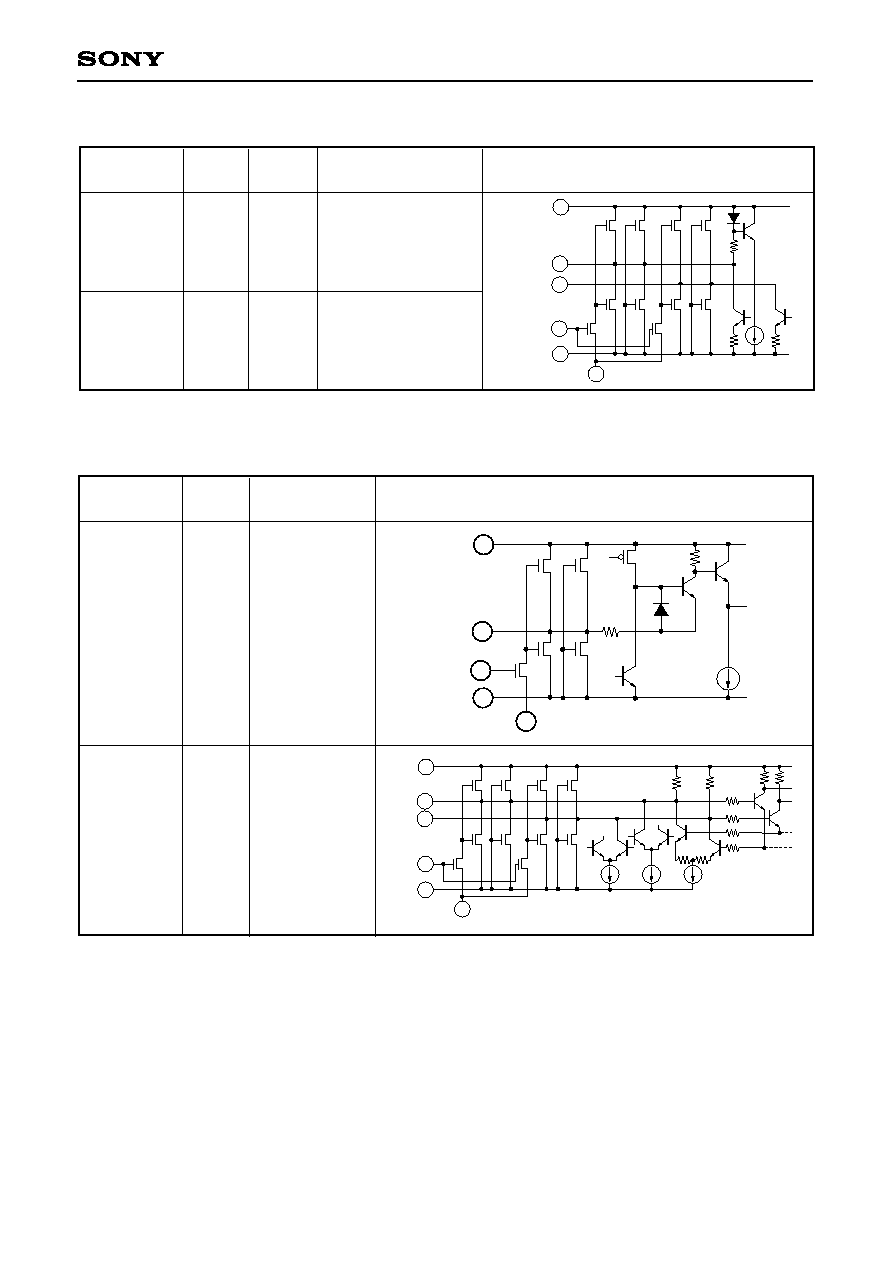

CXB1456R

Table 3. Special

Pin name

33

47, 48

External Register

External loop

filter

Pin

number

Descriptions

Equivalent circuit

REXT

LPFA/B

Table 2. Digital Signals (Cont.)

Pin name

SDATAP/N

REFRQP/N

40, 41

39, 42

Rx

Rx

Serial input

Refclk request

Pin

number

Type

Descriptions

Equivalent circuit

V

CC

A

SDATAP/N

V

EE

A

REFRQP/N

V

DD

GND

V

CC

A

LPFA

V

EE

A

V

DD

GND

LPFB

V

CC

V

EE

GND

REXT

V

DD

Ù 4 Ù

CXB1456R

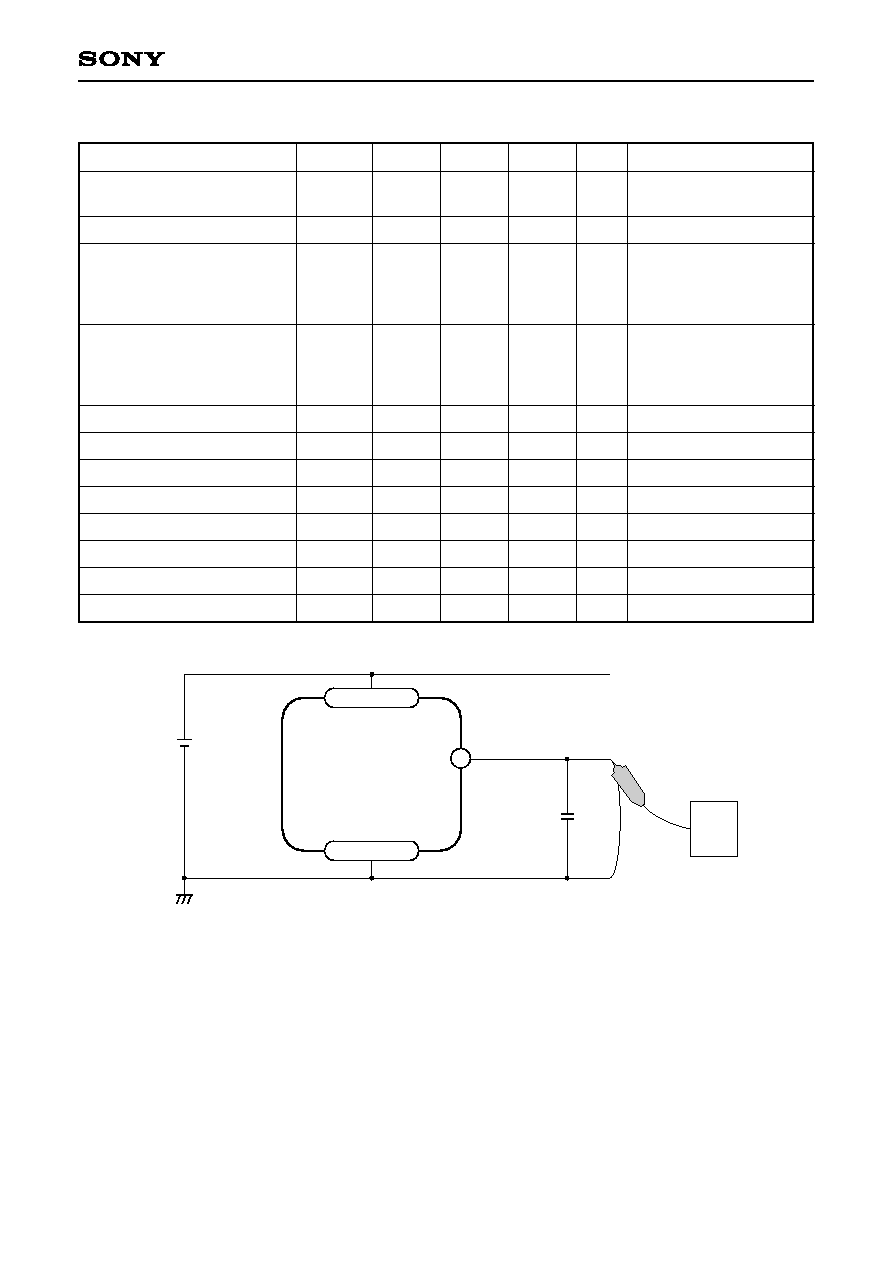

Electrical characteristics

Table 4. Absolute Maximum Rating

Description

Power supply voltage

TTL DC input voltage

TTL output current (High)

TTL output current (Low)

Serial input pin voltage

REFREQ output pin voltage

Storage temperature

V

CC

V

I

_T

I

OH

_T

I

OL

_T

Vsdin

V

RQ

out

Tstg

Ù0.3

Ù0.5

Ù10

0

Ù0.5

0.5

Ù65

4.2

4.6

0

10

V

CC

+ 0.5

V

CC

+ 0.5

150

V

V

mA

'

mA

V

V

¯C

Symbol

Min.

Typ.

Max.

Unit

Comments

Table 5. Recommended Operating Conditions

Description

Power supply voltage

Ambient temperature

V

CC

Ta

3.0

0

3.3

3.6

80

V

¯C

Symbol

Min.

Typ.

Max.

Unit

Comments

Table 6. DC Characteristics (Under the recommended conditons. See Tab. 5)

Description

Input HIGH voltage (TTL)

Input LOW voltage (TTL)

Input HIGH current (TTL)

Input LOW current (TTL)

Output HIGH voltage (TTL)

Output LOW voltage (TTL)

Output HIGH current (REFREQ)

Output LOW current (REFREQ)

Input dynamic range (SDATA)

Input dynamic range (SDATA)

Supply current

V

IH

_T

V

IL

_T

I

IH

_T

I

IL

_T

V

OH

_T

V

OL

_T

I

OH

_RQ

I

OL

_RQ

V

IM

_SD

V

ID

_SD

I

CC

2

0

Ù10

2.4

Ù0.1

7.8

V

CC

Ù 0.4

Ù0.5

0

138

77

V

CC

0.8

10

0.4

+0.1

11

V

CC

+ 0.2

+0.5

173

104

V

V

çA

çA

V

V

mA

mA

V

V

mA

mA

V

IN

= V

CC

V

IN

= 0

I

OH

= Ù3mA

I

OL

= 3mA

See Fig. 3, 4

REXT = 5.6k

Common mode voltage

Differential voltage

C

L

= 8pF, f = 65MHz

See Fig. 9, 10

Symbol

Min.

Typ.

Max.

Unit

Conditions

Worst Case

16 Grayscale

Ù 5 Ù

CXB1456R

37

38

43

39

42

TESTDT

CXB1456R

V

CC

CE

TESTEXN

REFRQP

150

50

50

150

REFRQN

V

DD

/V

CC

/V

CC

A

GND/V

EE

/V

EE

A

A

A

Fig. 3. I

OH

_RQ and I

OL

_RQ DC measurement

TESTDT

CE

TESTEXN

Fig. 4. I

OH

_RQ and I

OL

_RQ DC measurement setting

Ù 6 Ù

CXB1456R

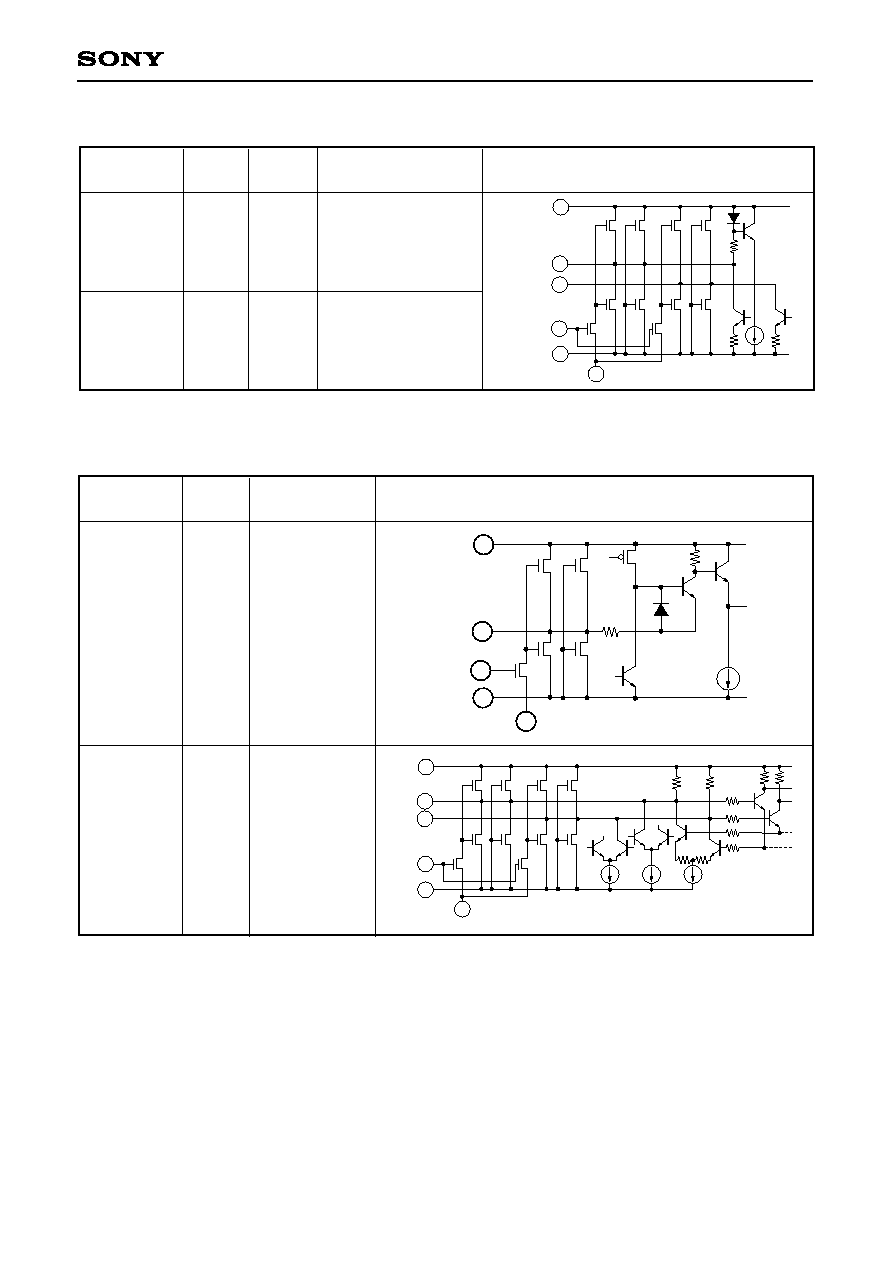

Table 7. AC Characteristics (Under the recommended conditons. See Tab. 5)

Description

Minimum SFTCLK frequency

Maximum SFTCLK frequency

SFTCLK duty factor

Pixel/Sync/Cntl/DE setup to

SFTCLK

Pixel/Sync/Cntl/DE hold to

SFTCLK

SFTCLK rise time

SFTCLK fall time

Pixel/Sync/Cntl/DE rise time

Pixel/Sync/Cntl/DE fall time

CLOCK mode assert time

CLOCK mode deassert time

LOS signal assert time

LOS signal deassert time

Fsftclk

Dsftclk

Tsetup

Thold

Torc

Tofc

Tord

Tord

TAclk

TDclk

TAlos

TDlos

65.0

35

17

9

4.5

16

9

4.5

0.5

20

0.5

0.15

25.0

65

5

3

5

3

MHz

MHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

çs

çs

çs

çs

Vth = 1.4V, C

L

= 8pF

Vth = 1.4V, C

L

= 8pF

25MHz

40MHz

65MHz

Vth = 1.4V, C

L

= 8pF

25MHz

40MHz

65MHz

0.8V to 2.0V, C

L

= 8pF

2.0V to 0.8V, C

L

= 8pF

0.8V to 2.0V, C

L

= 8pF

2.0V to 0.8V, C

L

= 8pF

Symbol

Min.

Typ.

Max.

Unit

Conditions

CXB1456R

TTLout

Cprobe

CL' + Cprobe = 8pF

oscillo-

scope

V

CC

CL'

V

DD

/V

CC

/V

CC

A

GND/V

EE

/V

EE

A

Fig. 5. Pixel/Sync/Cntl/DE waveform measurement

Ù 7 Ù

CXB1456R

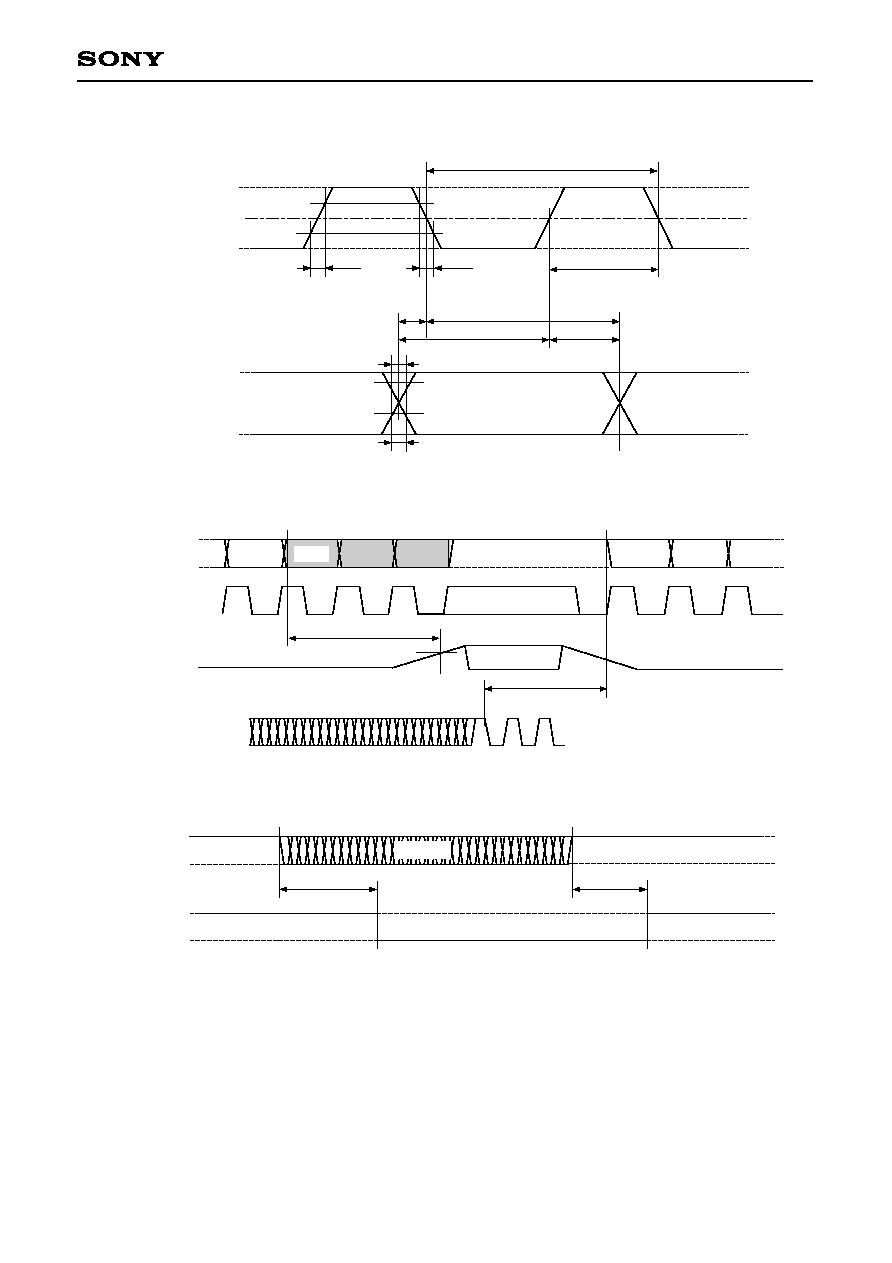

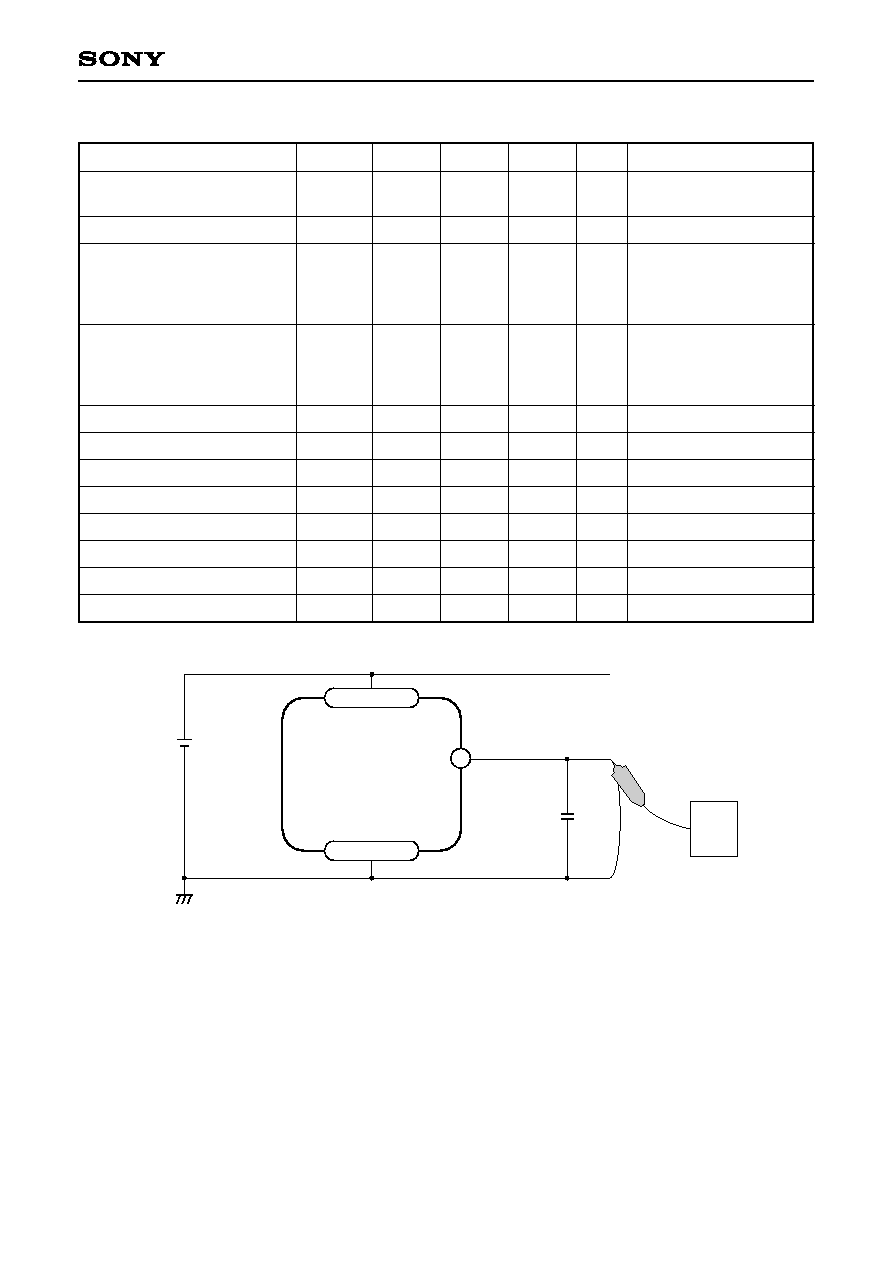

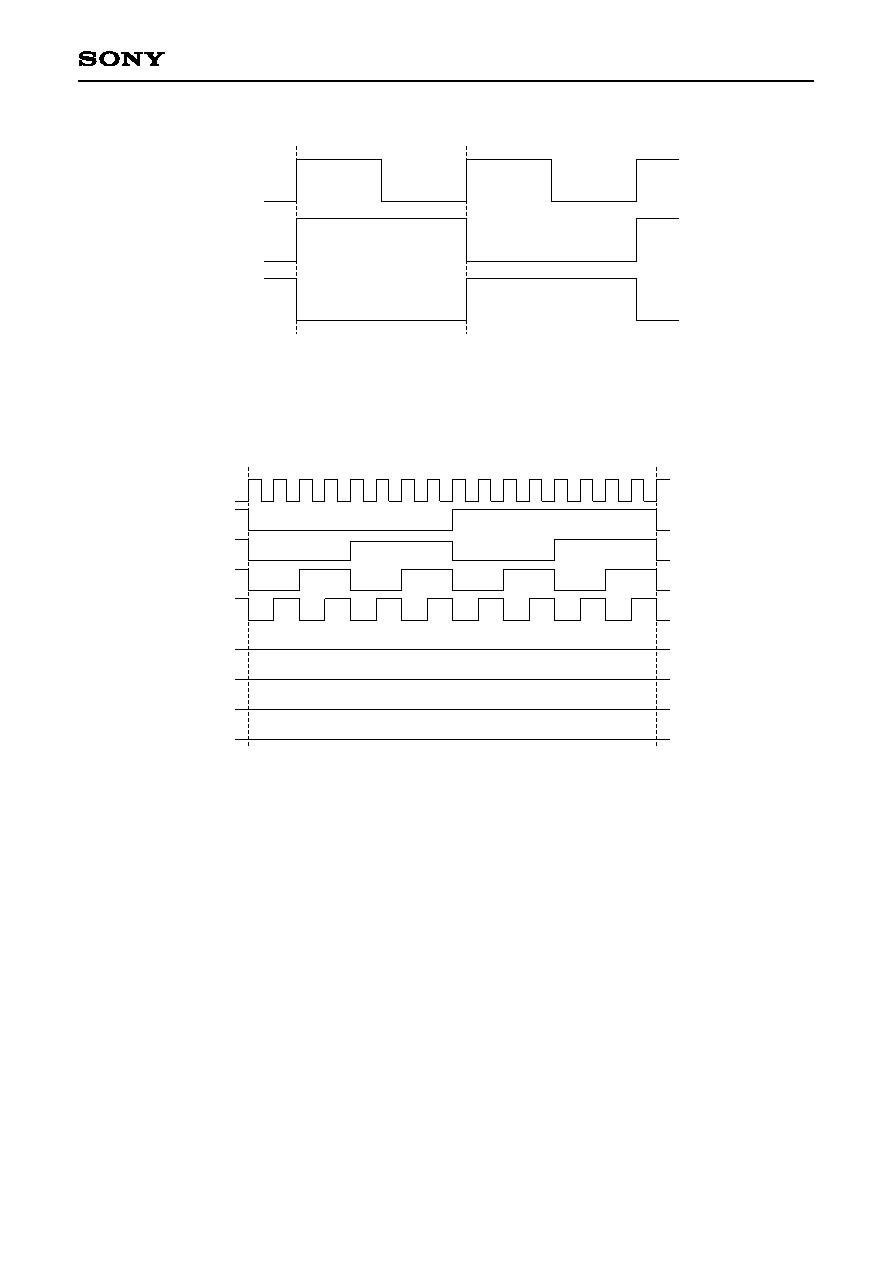

Timing Chart

SFTCLK

Torc

Tsetup

Tofc

Thold

Tord

2.0V

2.0V

0.8V

0.8V

Vth

1/Fsftclk

REDxx

Setup/hold time is referred from

rising edge in CLKPOL = GND

falling edge in CLKPOL = V

DD

GRNxx

BLUxx

H/Vsync

CNTL

DE

Tofd

Dsftclk/Fsftclk

Fig. 7. Refclk request timing

Pixel

Sync/Cntl/DE

SftClk

REFRQP

REFRQN

SDATAP

SDATAN

TAclk

Indefinite

Indefinite

TDclk

error

Fig. 8. Idle mode timing

LOS

SDATAP

SDATAN

TDlos

TAlos

NRZ data

Fig. 6. TTL output timing

Ù 8 Ù

CXB1456R

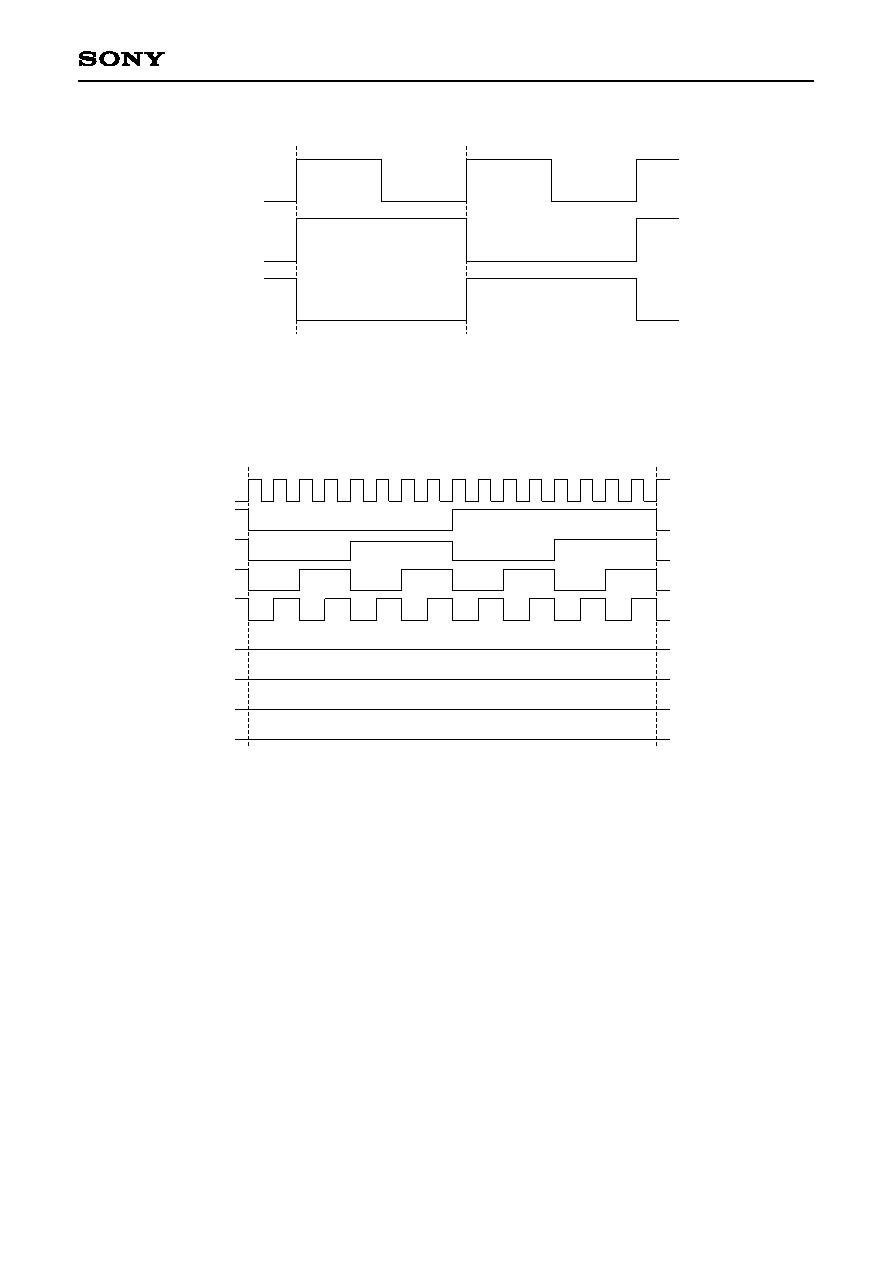

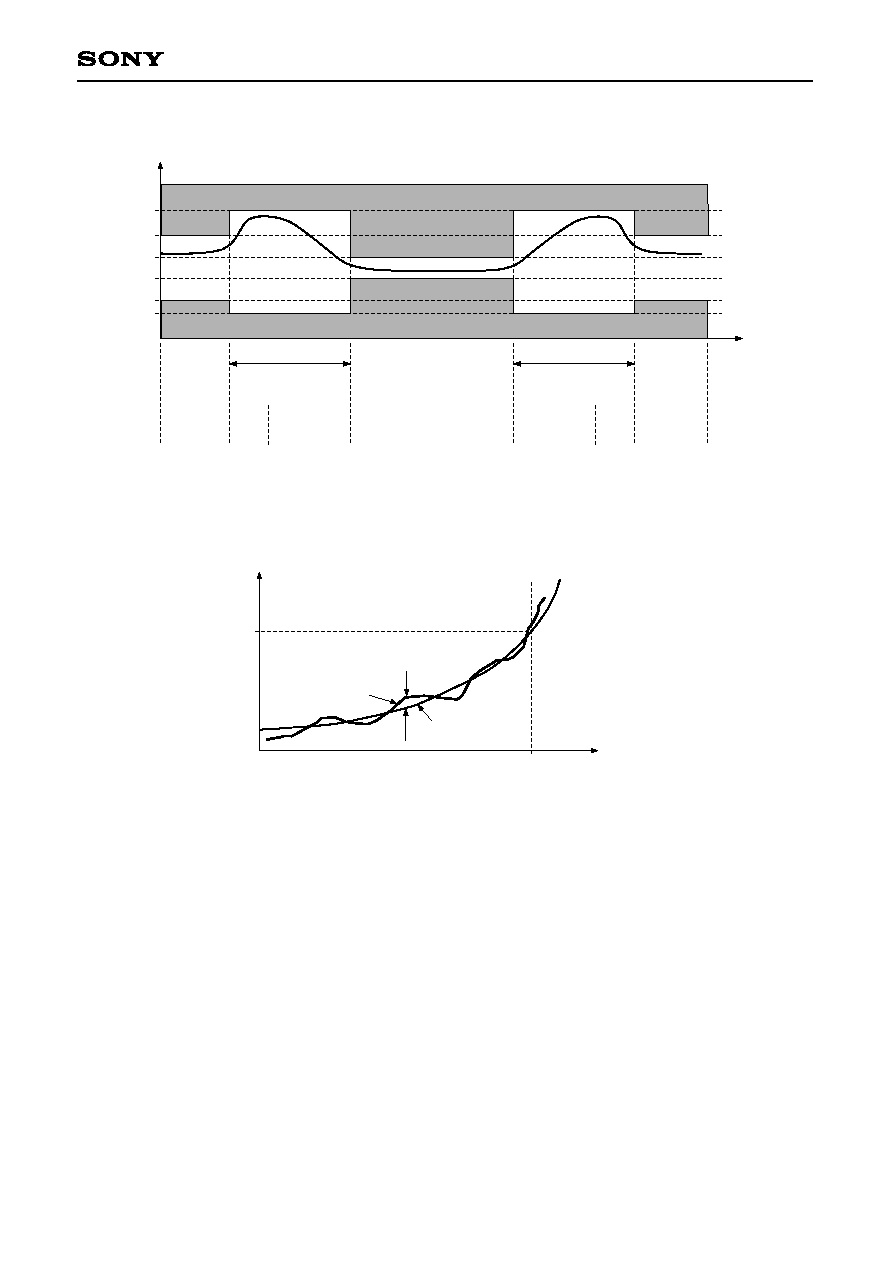

Fig. 9. Worst case test pattern

SFTCLK

RGB

<7, 5, 3, 1>

RGB

<6, 4, 2, 0>

f

f/2

f/2

Fig. 10. 16 Grayscale test pattern

SFTCLK

RGB <7>

RGB <6>

f

f/8

f/16

f/2

f/4

Fix Low

Fix Low

Fix Low

Fix Low

RGB <4>

RGB <5>

RGB <3>

RGB <2>

RGB <1>

RGB <0>

Ù 9 Ù

CXB1456R

CLKPOL Pin Control

The CLKPOL pin is used to select the SFTCLK trigger edge. (See Table 8.)

The CLKPOL pin is open High-impedance TTL input, and this should not be left open for use. (See Fig. 12.

Recommended application circuit.)

Table 8. SFTCLK Polarity

PANEL1

L

L

H

H

L

H

L

H

VGA (640

æ

480)

SVGA (800

æ

600)

XGA (1024

æ

768)

VGA to XGA

PANEL0

Supporting panel size

25MHz

40MHz

65MHz

25MHz to 65MHz

Shift Clock

750Mbps

1200Mbps

1950Mbps

750Mbps to 1950Mbps

Serial rate

CLKPOL

L

H

Rising edge

Falling edge

Receiver operation trigger

Table 9. Panel Mode

LOS Pin Output

The LOS pin shows the absence of proper level of SDATA signal. The LOS pin is High when the connector is

disconnected or the transmitter is idle.

The LOS pin is TTL output.

PANEL1 and 0 Pin Control

The PANEL1 and 0 pins are used to select the panel mode. (See Table 9.)

For the normal use, the all frequencies of SFTCLK (25MHz to 65MHz) can be covered by fixing both PANEL1

and 0 to High.

The PANEL1 and 0 pins are open High-impedance TTL inputs, and they should not be left open for use. (See

Fig. 12. Recommended application circuit.)

Test Pin Control

The TESTEXN and TESTDT pins are for test only. Select normal mode. (See Table 11.)

The TESTEXN and TESTDT pins are open High-impedance TTL inputs, and they should not be left open for use.

CE Pin Control

The CE pin is used to select the standby mode. (See Table 10.)

The CE pin is open High-impedance TTL input, and this should not be left open for use. (See Fig. 12.

Recommended application circuit.)

Table 10

Table 11. Test mode

TESTEXN

L

H

TESTDT

X

X

Test mode

Normal mode

Operation mode

CE

L

H

Standby mode, all TTL outputs fixed to Low (excluding LOS)

Normal mode

Operation mode

Ù 10 Ù

CXB1456R

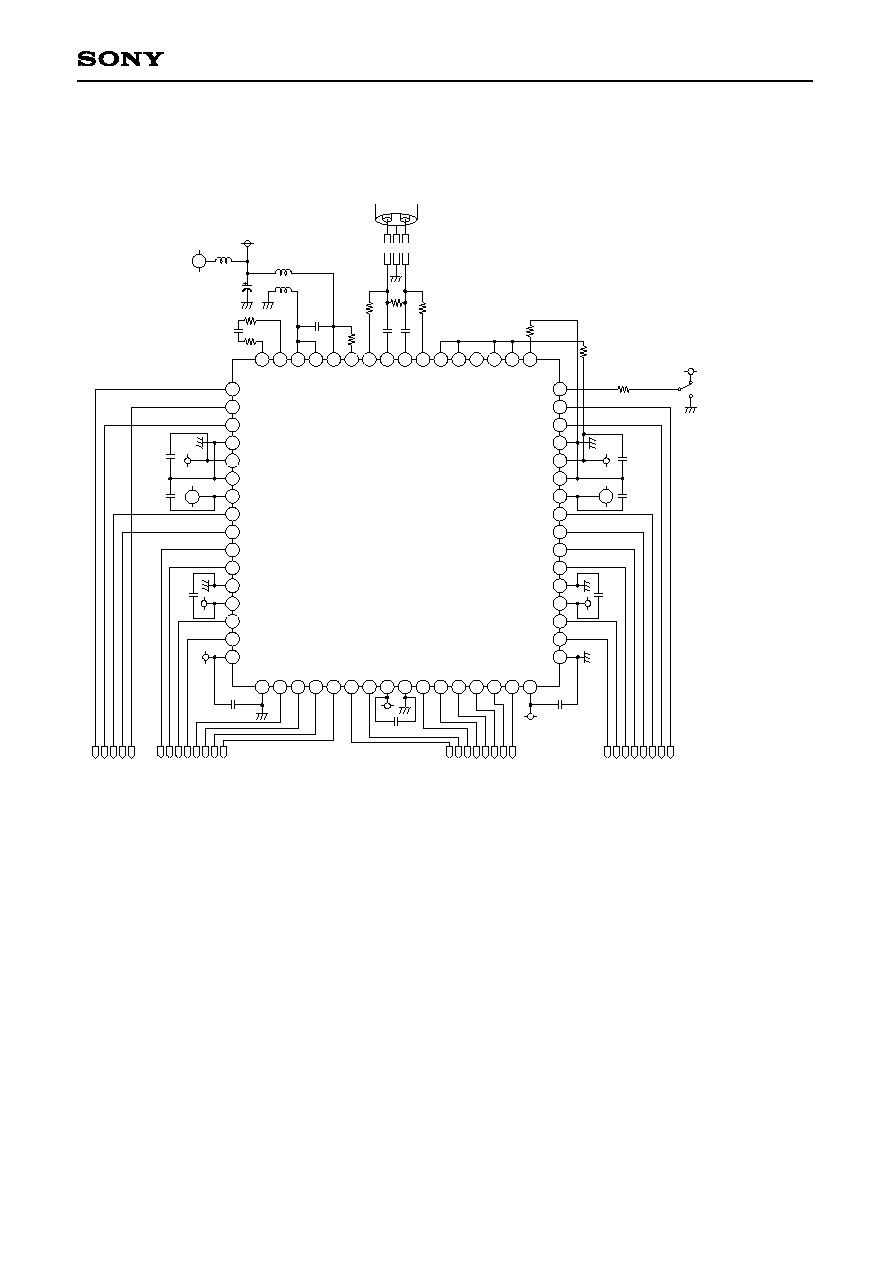

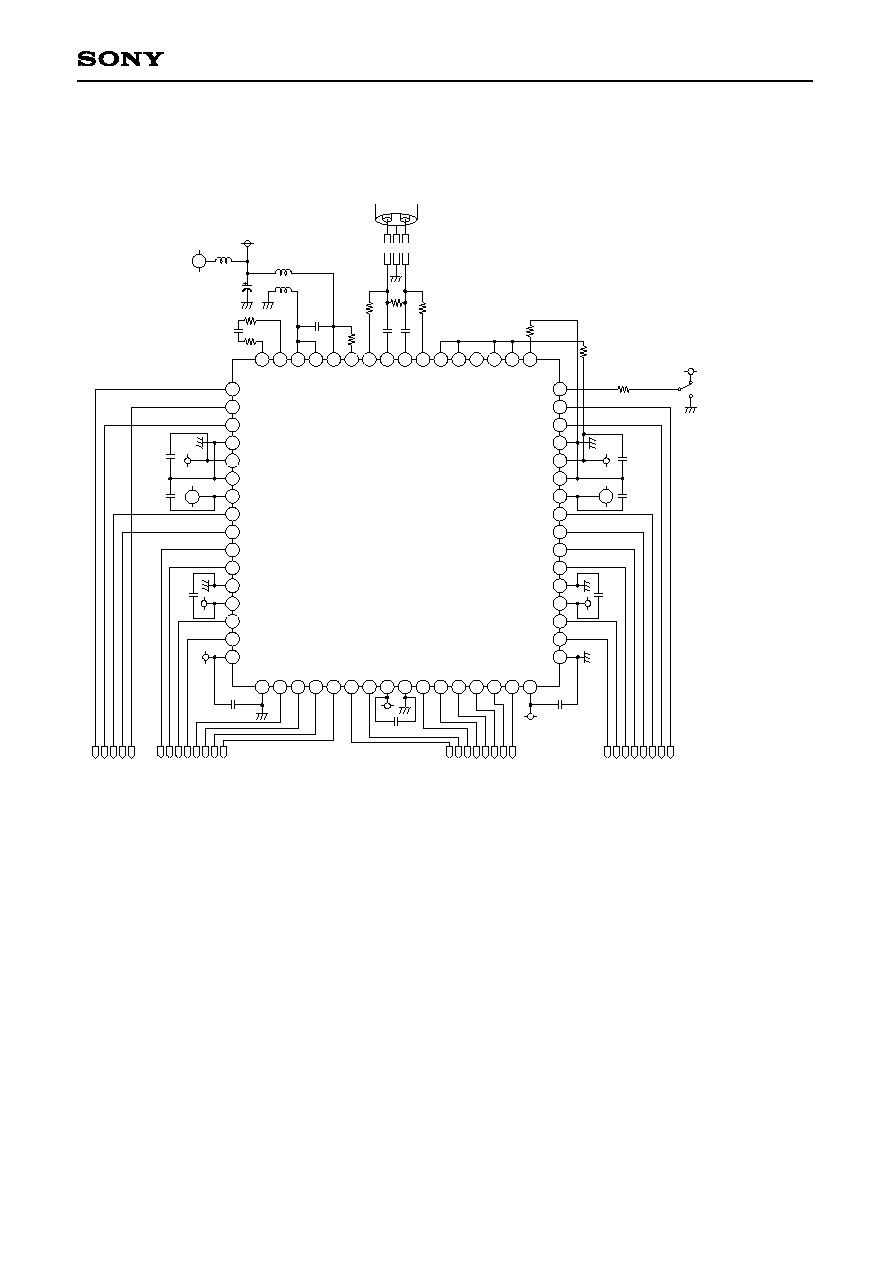

Applications

CXB1456R GVIF receiver is applied to the digital RGB signal transmission for

P/C with LCD monitor

Video on demand system

Monitoring system

Graphical controller

Projector

Digital TV monitor

Car navigation system

with GVIF transmitter, CXB1455R.

CXB1455R GVIF Transmitter

CXB1456R GVIF Receiver

Parallel

to

Serial

Converter

Cable

Driver

PLL

RED (7 to 0)

GRN (7 to 0)

BLU (7 to 0)

SYNC/

DE/CNTL

SHIFTCLOCK

RED (7 to 0)

GRN (7 to 0)

BLU (7 to 0)

SYNC/

DE/CNTL

SHIFTCLOCK

STP or Twin axial

8

8

8

4

E

n

c

o

d

e

r

Serial

to

Parallel

Converter

PLL

D

e

c

o

d

e

r

8

8

8

Fig. 11. Block Diagram of GVIF transceiver chip set

Ù 11 Ù

CXB1456R

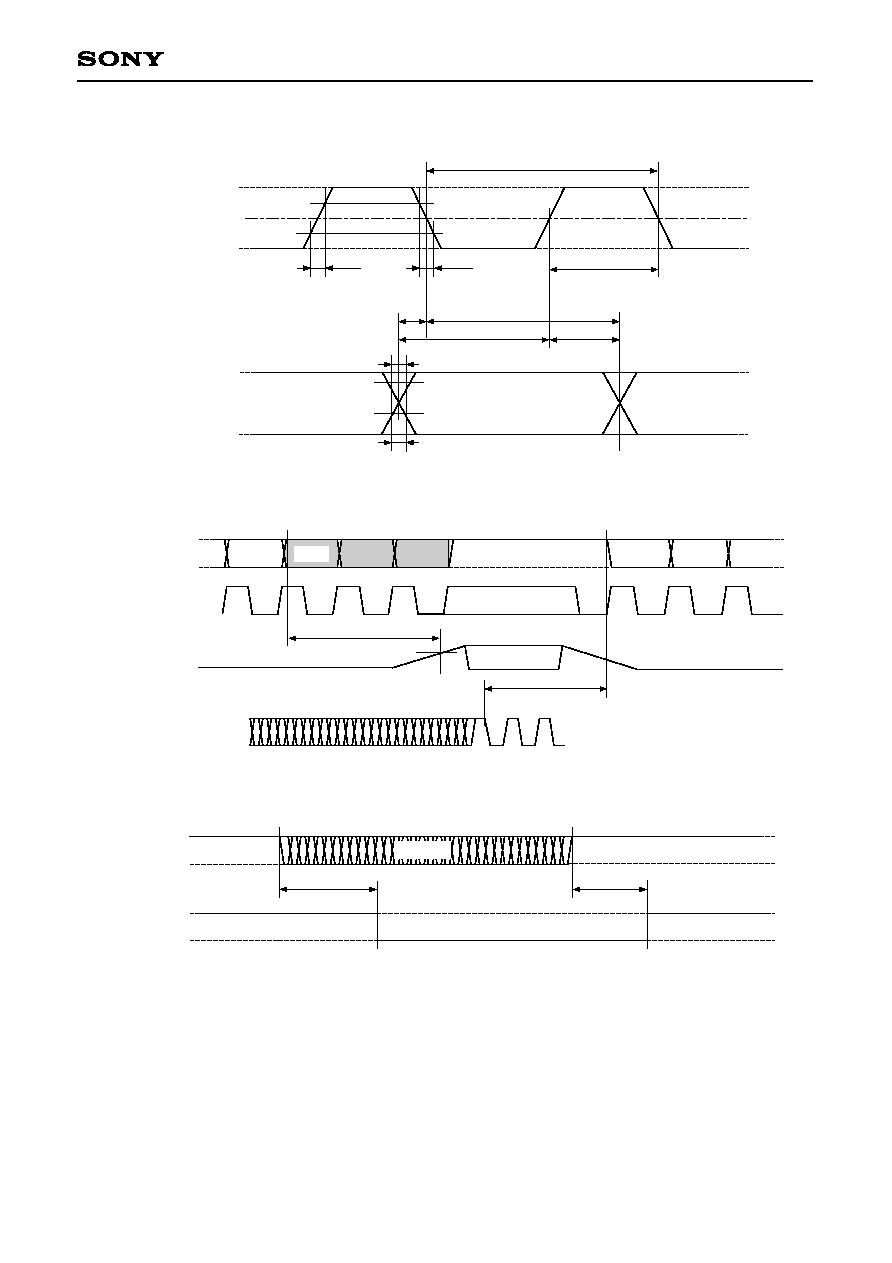

Application Cicuit

5.6k (1)

(1) CHIP RESISTOR (1%)

(2) CHIP CAPACITOR

(3) FORMED BY THE PRINTED CIRCUIT PATTERN

(L = 0.5 to 1.0mm/W = 0.5 to 1.0mm)

H: FALLING EDGE TRIGGER

L: RISING EDGE TRIGGER

100

(1)

150

(1)

150

(1)

47p

(2)

47p

(2)

0.1

ç

(2)

0.1 to 0.4n (3)

0.1 to 0.4n (3)

0.1 to 0.4n (3)

33

ç

16V

V

CC

V

CC

V

CC

0.1

ç

(2)

V

CC

Differential cable

47 (1)

470p (2)

47 (1)

330

330

330

Connector

0.1

ç

(2)

0.1

ç

(2)

0.1

ç

(2)

7

V

CC

0.1

ç

(2)

0.1

ç

(2)

0.1

ç

(2)

6 5 4

RED DATA

3 2 1 0

MSB

LSB

V

CC

V

CC

V

CC

0.1

ç

(2)

0.1

ç

(2)

7 6 5 4

GREEN DATA

3 2 1 0

MSB

LSB

7 6 5 4

BLUE DATA

3

C

N

T

L

S

F

T

C

L

K

H

S

Y

N

C

V

S

Y

N

C

D

E

2 1 0

MSB

LSB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

CNTL

DE

SFTCLK

GND

V

DD

V

EE

V

CC

HSYNC

VSYNC

CXB1456R

B7

B6

GND

V

DD

B5

B4

V

DD

G

N

D

B

3

B

2

B

1

B

0

G

7

G

6

V

D

D

G

N

D

G

5

G

4

G

3

G

2

G

1

G

0

V

D

D

L

P

F

B

L

P

F

A

V

E

E

S

V

E

E

A

V

C

C

A

T

E

S

T

E

X

N

R

E

F

R

Q

N

S

D

A

T

A

N

S

D

A

T

A

P

R

E

F

R

Q

P

C

E

T

E

S

T

D

T

L

O

S

P

A

N

E

L

1

P

A

N

E

L

0

R

E

X

T

CLKPOL

R0

R1

GND

V

DD

V

EE

V

CC

R2

R3

R4

R5

GND

V

DD

R6

R7

GND

SW1

E

E

E

V

CC

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

Fig. 12. Recommended application circuit

Ù 12 Ù

CXB1456R

Recommended Printed Circuit Board Structure

,

,

,

,

,

,

,

,

L1 : Cu plate (18

ç

m) + solder coat

l1 : Fiber-glass epoxy core (0.3mm)

L2 : Cu plate (36

ç

m)

l2 : Fiber-glass epoxy core (0.8mm)

L3 : Cu plate (36

ç

m)

l3 : Fiber-glass epoxy core (0.3mm)

L4 : Cu plate (18

ç

m) + solder coat

Recommended Printed Circuit Board Pattern

POWER and special signal routing example

CNTL

DE

SFTCLK

GND

V

DD

V

EE

V

CC

HSYNC

VSYNC

B7

B6

GND

V

DD

B5

B4

V

DD

G

N

D

B

3

B

2

B

1

B

0

G

7

G

6

V

D

D

G

N

D

G

5

G

4

G

3

G

2

G

1

G

0

V

D

D

L

P

F

B

L

P

F

A

V

E

E

S

V

E

E

A

V

C

C

A

T

E

S

T

E

X

N

R

E

F

R

Q

N

S

D

A

T

A

N

S

D

A

T

A

P

R

E

F

R

Q

P

C

E

T

E

S

T

D

T

L

O

S

P

A

N

E

L

1

P

A

N

E

L

0

R

E

X

T

CLKPOL

R0

R1

GND

V

DD

V

EE

V

CC

R2

R3

R4

R5

GND

V

DD

R6

R7

GND

D

D

D

D

D

D

D

D

G

G

G

G

G

1

64

49

16

17

32

33

48

0.5mm

L2 doesn't have plane

in this area

G

G

G

Through hole to the GND plane (L2)

Through hole to the V

CC

plane (L3)

Through hole to the V

DD

plane (L3)

Chip capacitor

Chip resistor

G

E

D

E

G

G

E

Fig. 13. Recommended Printed Circuit Board Structure

Fig. 14. Recommended Printed Circuit Board Pattern

Ù 13 Ù

CXB1456R

Micro Strip Line

For maximum performance, the impedance between the pins SDDATAP/N of the LSI and the footprint of the

connector should be 50

using a micro strip line. 50

impedance can be reached when using 0.5mm width

pattern lines on L1 using this circuit board structure. The length of the lines should be identical and through-

hole should not be used. L2 is recommended as the large ground plane.

Terminators

Terminators (100

resistor) should be located as close to the LSI as possible.

Filter Devices and Reference Registors

Capacitors and resistors which are connected to LPFA/B and REXT are filters and reference resistors. The

region of Layer 2 (L2) is under the device and conductive patterns. The ground plane should be taken off in

order to reduce parasitic capacitors.

Bypass Capacitors

Bypass capacitors (0.1çF SMD type) should be located as close to the pins as possible. Refer to the

recommendation.

Ù 14 Ù

CXB1456R

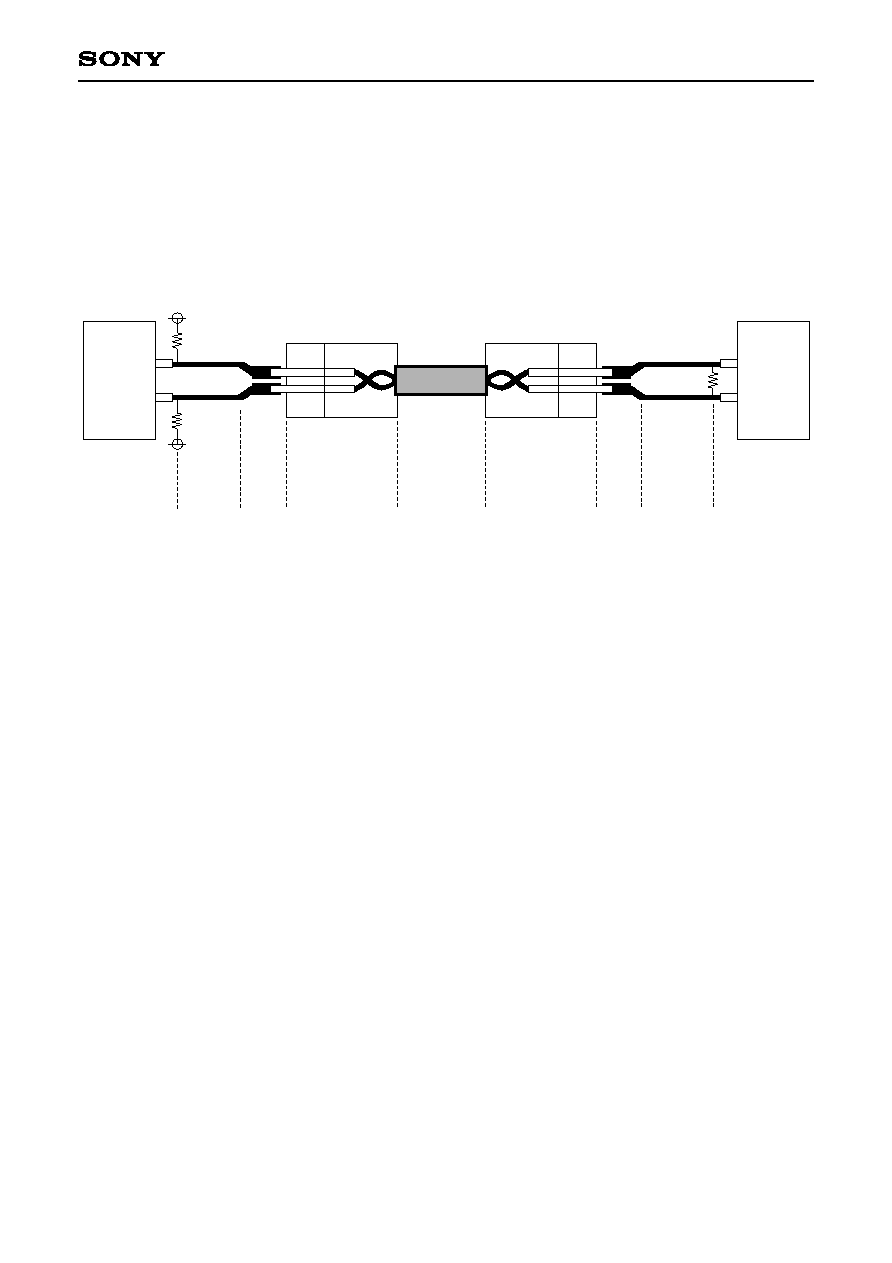

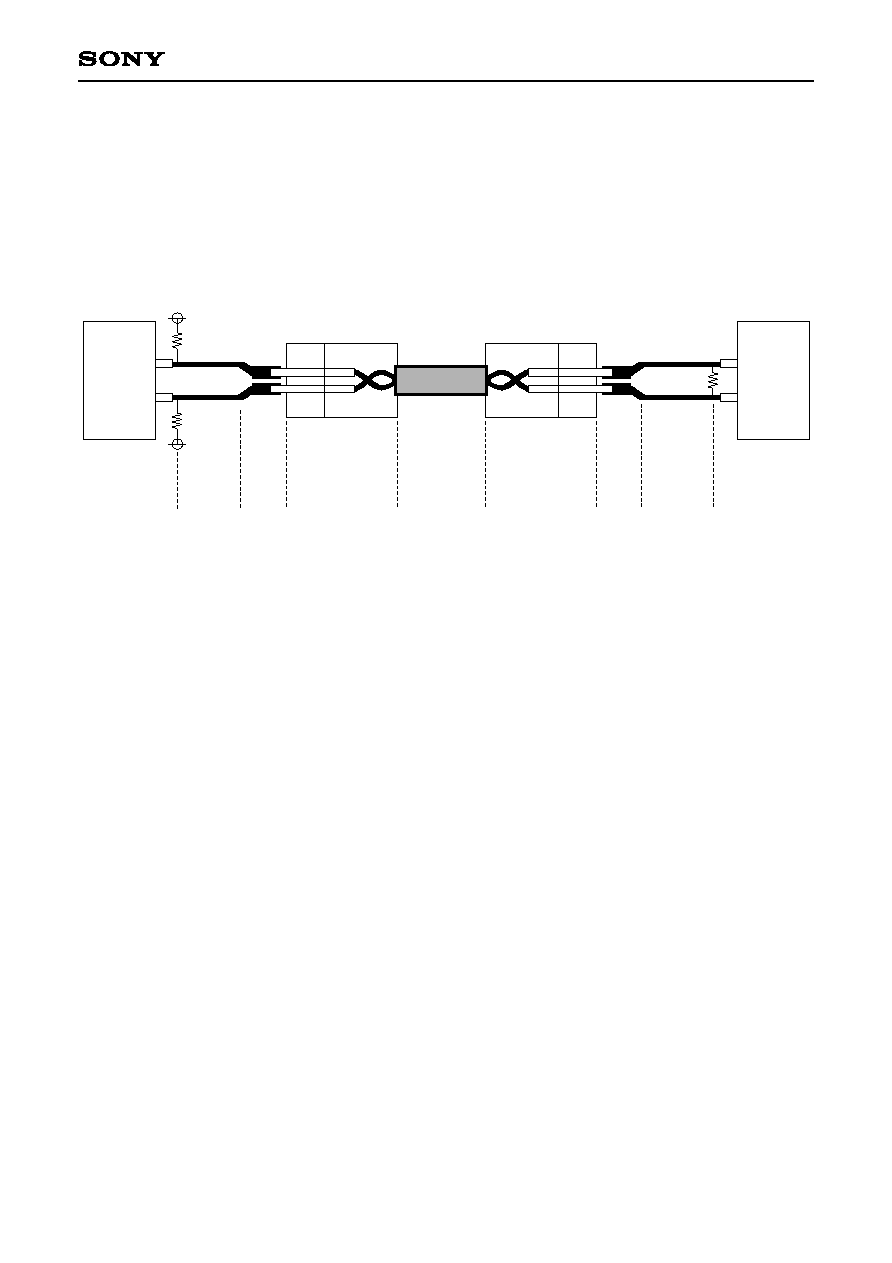

Recommendation for Cable and Connector Characteristics

The GVIF system uses terminators at both ends (transmitter and receiver), a cable equalizer and a small

amplitude differential signal. In order to solve the problems of high speed data transmission such as signal

reflection, reduce the signal level and EMI. In order to achieve the best solution, note the following:

Tx

LSI

Rx

LSI

Tx

termination

50

Tx

termination

100

Microstrip

line

(50

)

Microstrip

line

(50

)

Foot

print

Foot

print

Cable

(diff. 100

)

Connector

Connector

It is important to note the following issues for a good data transmission system:

ñ Good impedance matching

Differential impedance should be fit to the recommended template on the next page.

ñ Cable loss should be small and the loss curve should be smooth.

Maximum loss should be less than 6dB at 1GHz.

See the next page.

ñ Skew of POS/NEG (differential signal) should be small

Less than 12% of 1-bit time or 160ps@VGA, 100ps@SVGA, 60ps@XGA.

ñ Good EMI performance cable and connectors.

In order to satisfy these issues, the recommendations are as follows:

ñ Use the differential cable which provides good controlled impedance, low loss and good skew matching.

A shielded twisted pair (STP) cable is recommended.

ñ Use a low reflectance connector.

ñ To minimize interference from other signals, high speed signal lengths should be identical.

ñ Use double shielded cable.

Ù 15 Ù

CXB1456R

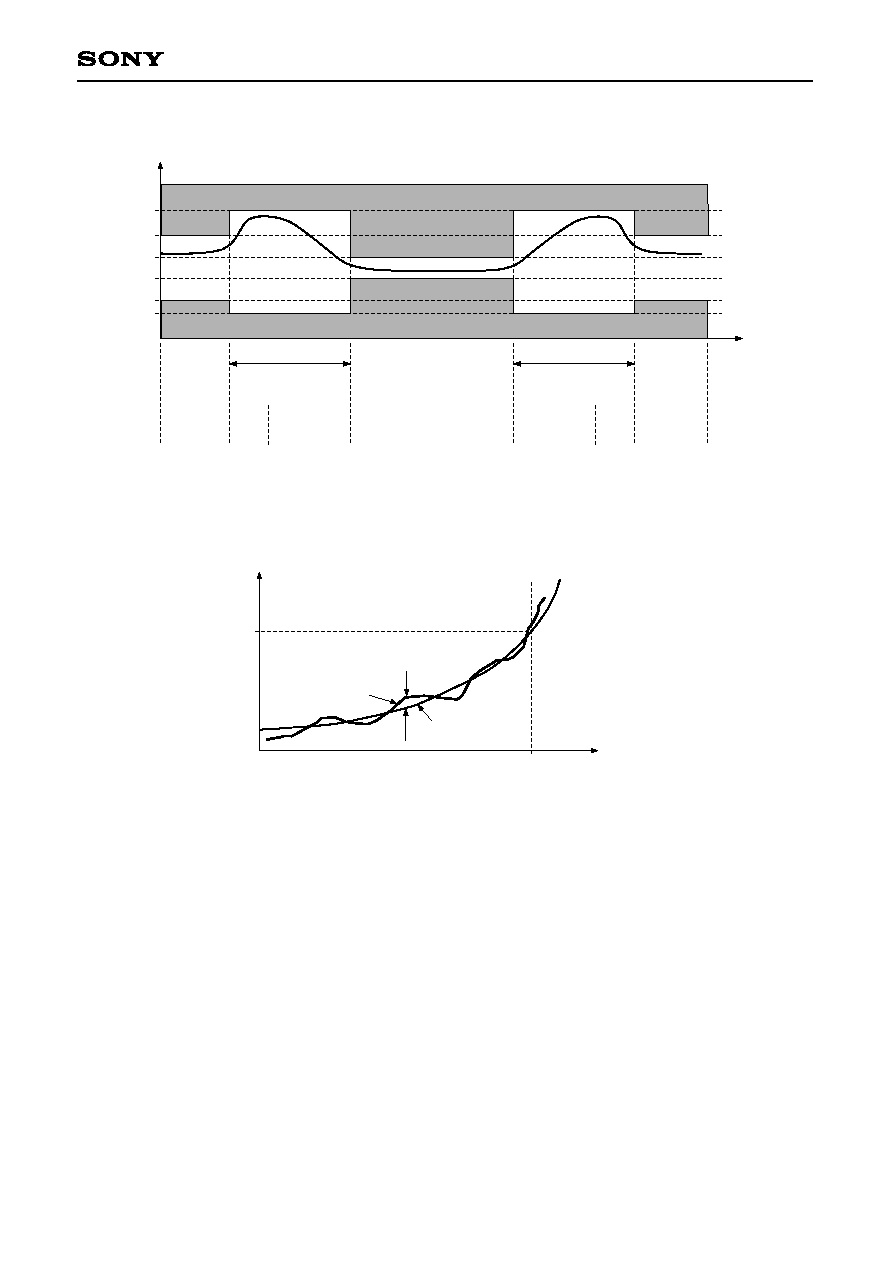

Recommended Transmission Path : Differential impedance template

150

Zo

(

)

110

106

94

90

75

Microstrip

line

Microstrip

line

Foot

print

Foot

print

Connector

< 500ps

< 500ps

Connector

Recommended Transmission Path : Attennation Characteristics

Loss

< 6dB

Measured curve

Fitting curve

2dB

1GHz

Frequency

Ù 16 Ù

CXB1456R

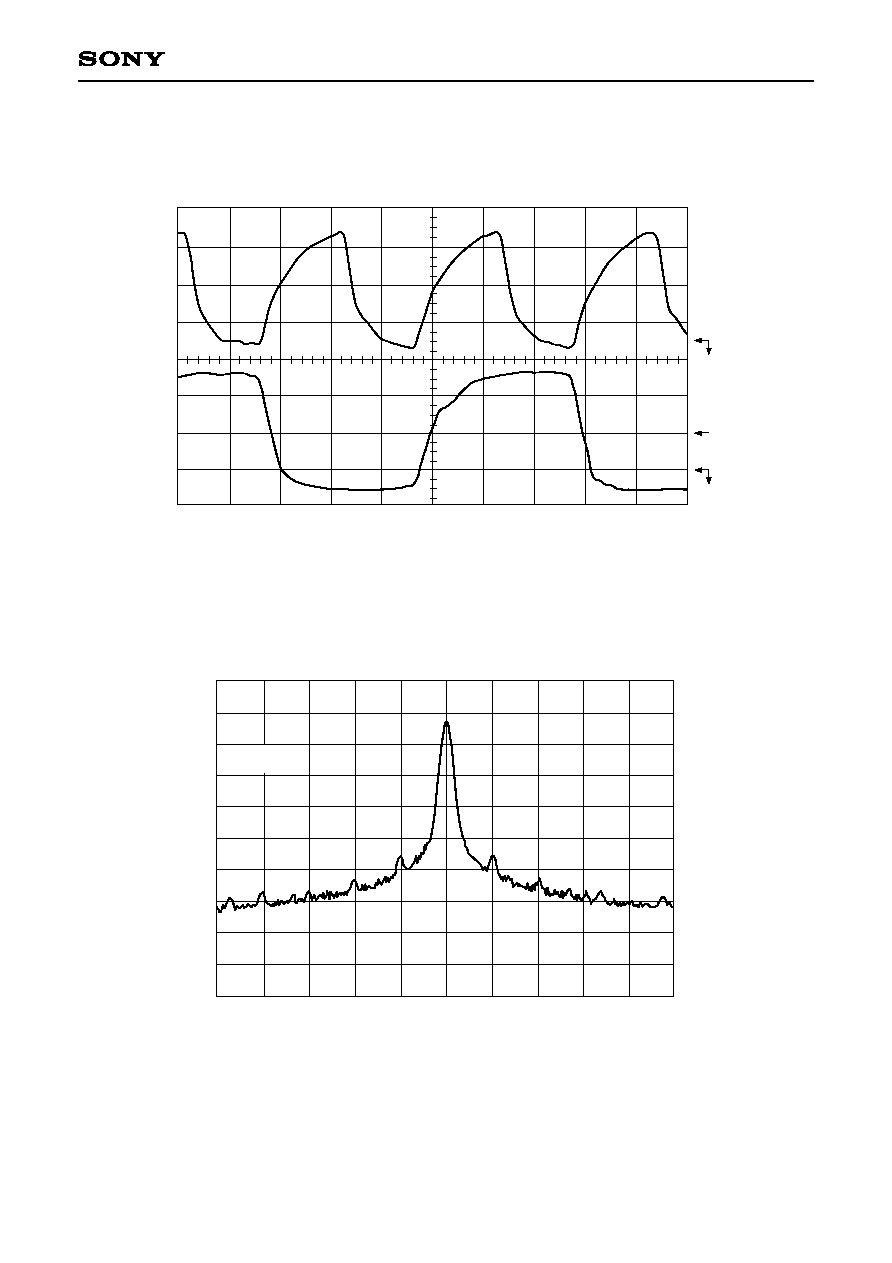

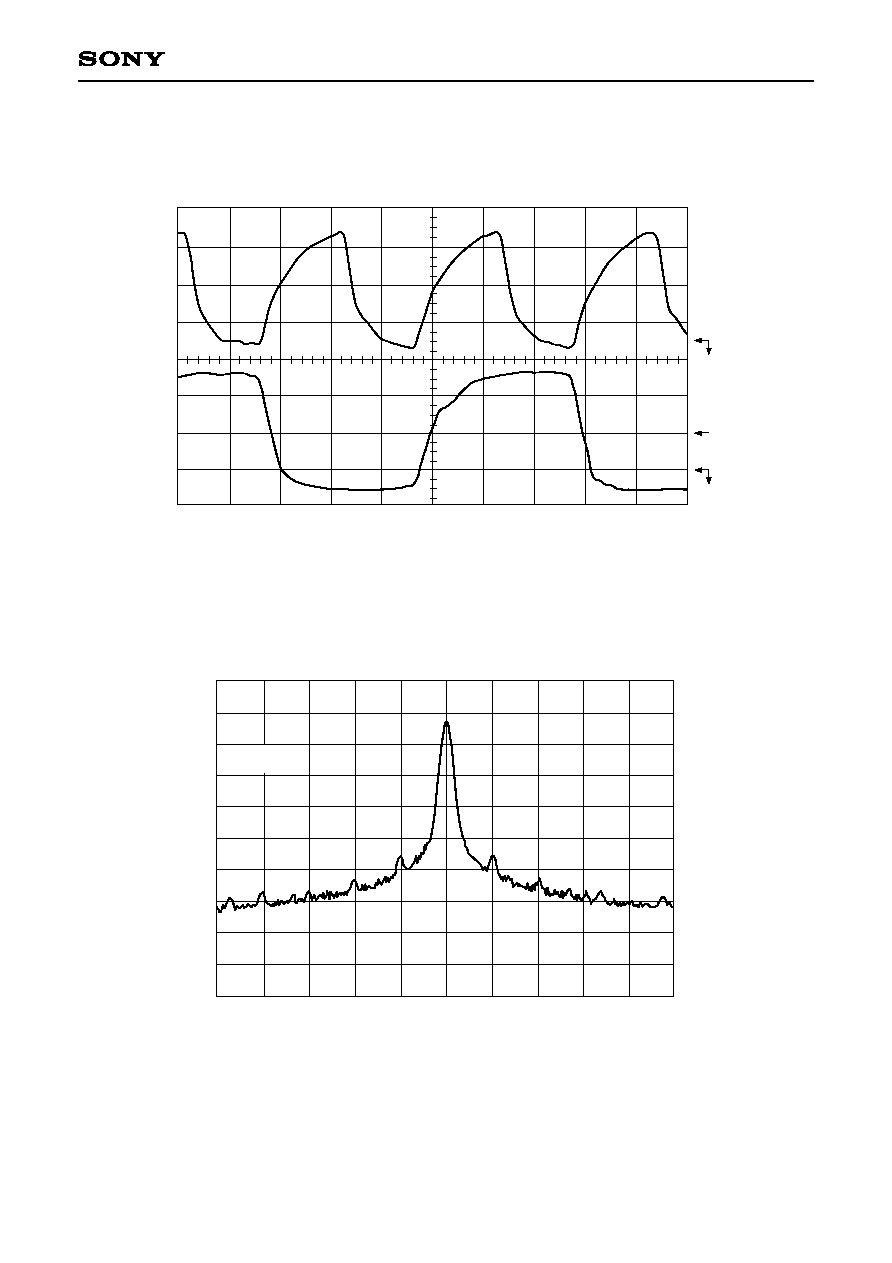

TTL output waveform with C

L

= 8pF

1.00V/div

1.00V/div

5ns/div

T

SFTCLK

65MHz

TTL output

B0

65Mbps

TTL output

ATTEN 10dB

RL 0dBm

CENTER 65.00MHz

RBW 100kHz

SPAN 10.00MHz

SWP 50.0ms

VBW 100kHz

10dB/

SFTCLK Power spectrum

D

CENTER

65.00MHz

Ù 17 Ù

CXB1456R

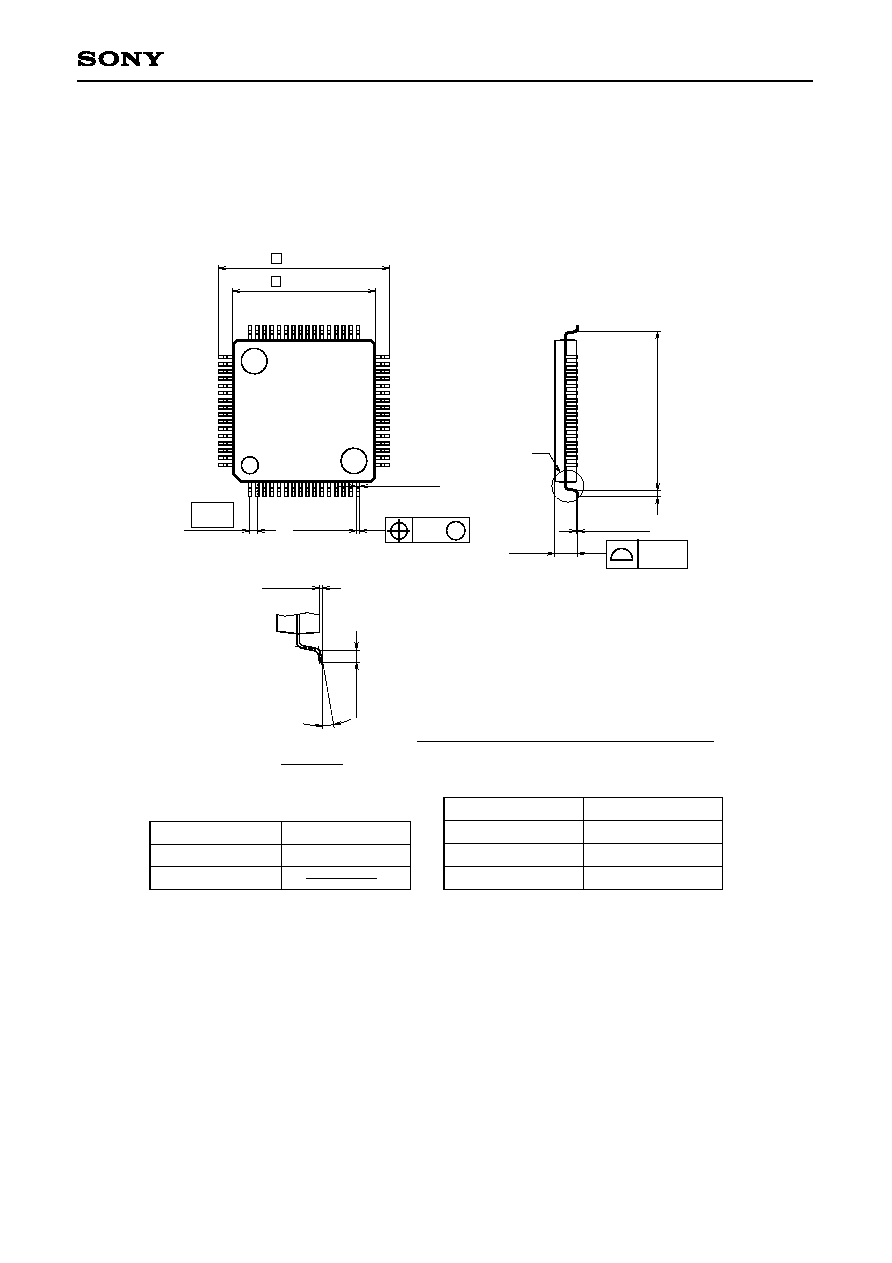

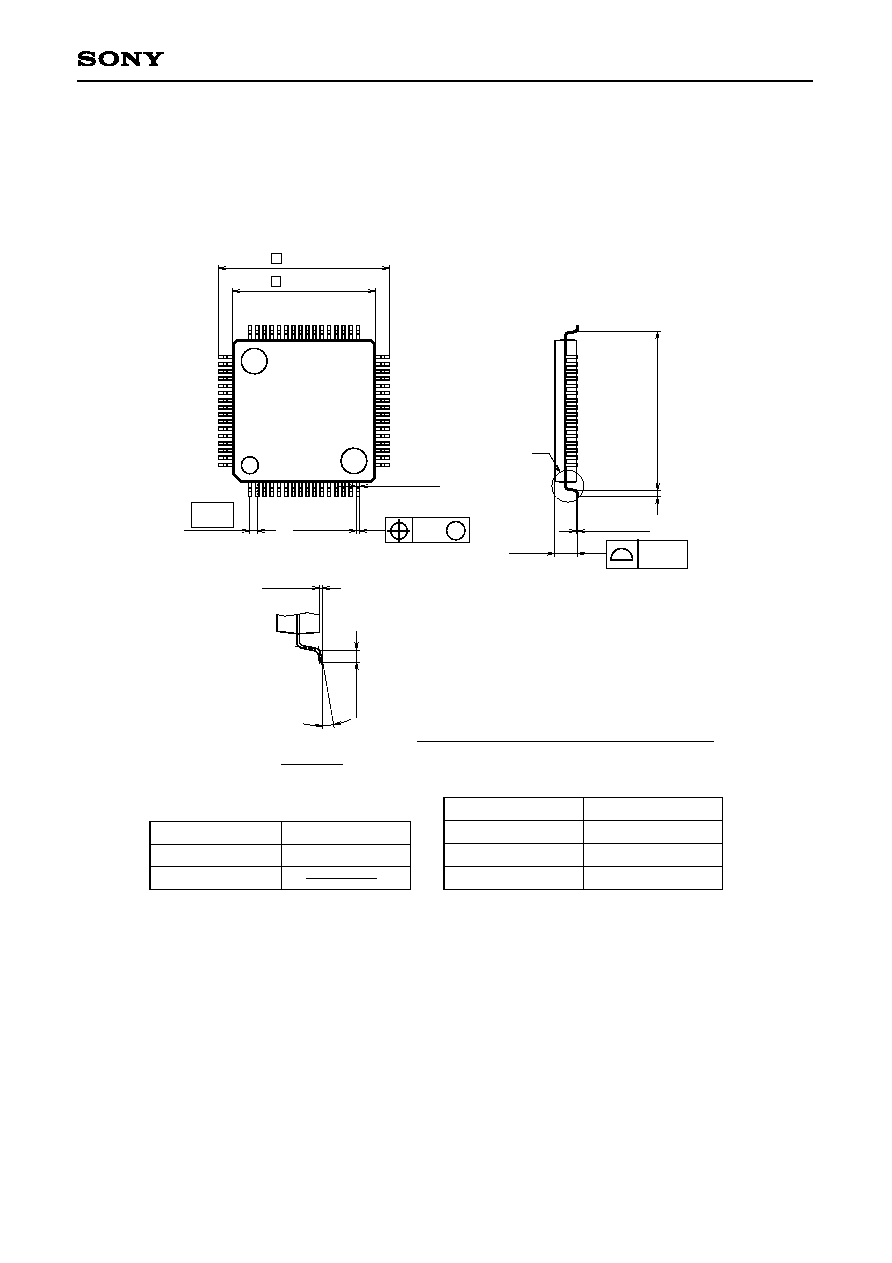

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

PLATING

42/COPPER ALLOY

PACKAGE STRUCTURE

12.0 Ý 0.2

10.0 Ý 0.1

(0.22)

0.18 Ù 0.03

+ 0.08

1

16

17

32

33

48

49

64

0.1 Ý 0.1

0

.

5

Ý

0

.

2

0¯ to 10¯

64PIN LQFP (PLASTIC)

LQFP-64P-L01

LQFP064-P-1010

0.3g

DETAIL A

0

.

5

Ý

0

.

2

(

1

1

.

0

)

0.127 Ù 0.02

+ 0.05

A

1.5 Ù 0.1

+ 0.2

0.1

SOLDER/PALLADIUM

NOTE: Dimension "

" does not include mold protrusion.

0.13 M

0.5

NOTE : PALLADIUM PLATING

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).