1998 Aug 24

2

Philips Semiconductors

Objective specification

SDH/SONET STM1/OC3 optical receiver

TZA3030

FEATURES

�

Low equivalent input noise, typically 1 pA/

Hz

�

Wide dynamic range, typically 0.5

�

A to 2 mA

�

On-chip low-pass filter. The bandwidth can be varied

between 90 and 150 MHz using an external resistor.

Default value is 120 MHz.

�

Differential transimpedance of 1.8 M

�

On-chip Automatic Gain Control (AGC)

�

Positive Emitter Coupled Logic (PECL) or

Current-Mode Logic (CML) compatible data outputs

�

LOS (Loss Of Signal) detection

�

LOS threshold level can be adjusted using a single

external resistor

�

On-chip DC offset compensation

�

Single supply voltage from 3.0 to 5.5 V

�

Bias voltage for PIN diode.

APPLICATIONS

�

Digital fibre optic receiver in short, medium and long

haul optical telecommunications transmission systems

or in high speed data networks

�

Wideband RF gain block.

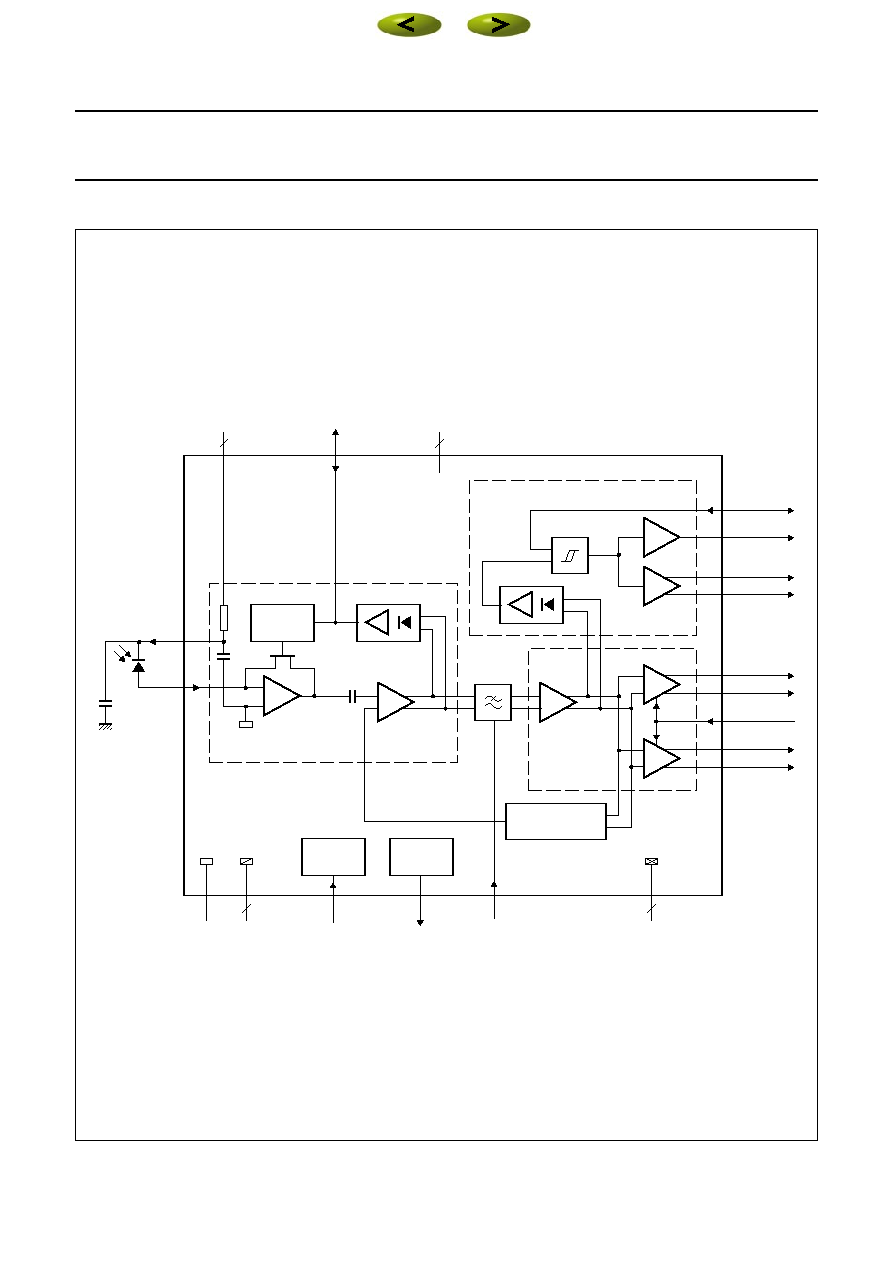

GENERAL DESCRIPTION

The TZA3030 optical receiver is a low-noise

transimpedance amplifier with AGC plus a limiting

amplifier designed to be used in SDH/SONET fibre optic

links. The TZA3030 amplifies the current generated by a

photo detector (PIN diode or avalanche photodiode) and

converts it to a differential output voltage.

ORDERING INFORMATION

TYPE

NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

TZA3030HL

LQFP32

plastic low profile quad flat package; 32 leads; body 5

�

5

�

1.4 mm

SOT401-1

TZA3030U

-

naked die in waffle pack carriers; die dimensions 1.58

�

1.58 mm

-

1998 Aug 24

4

Philips Semiconductors

Objective specification

SDH/SONET STM1/OC3 optical receiver

TZA3030

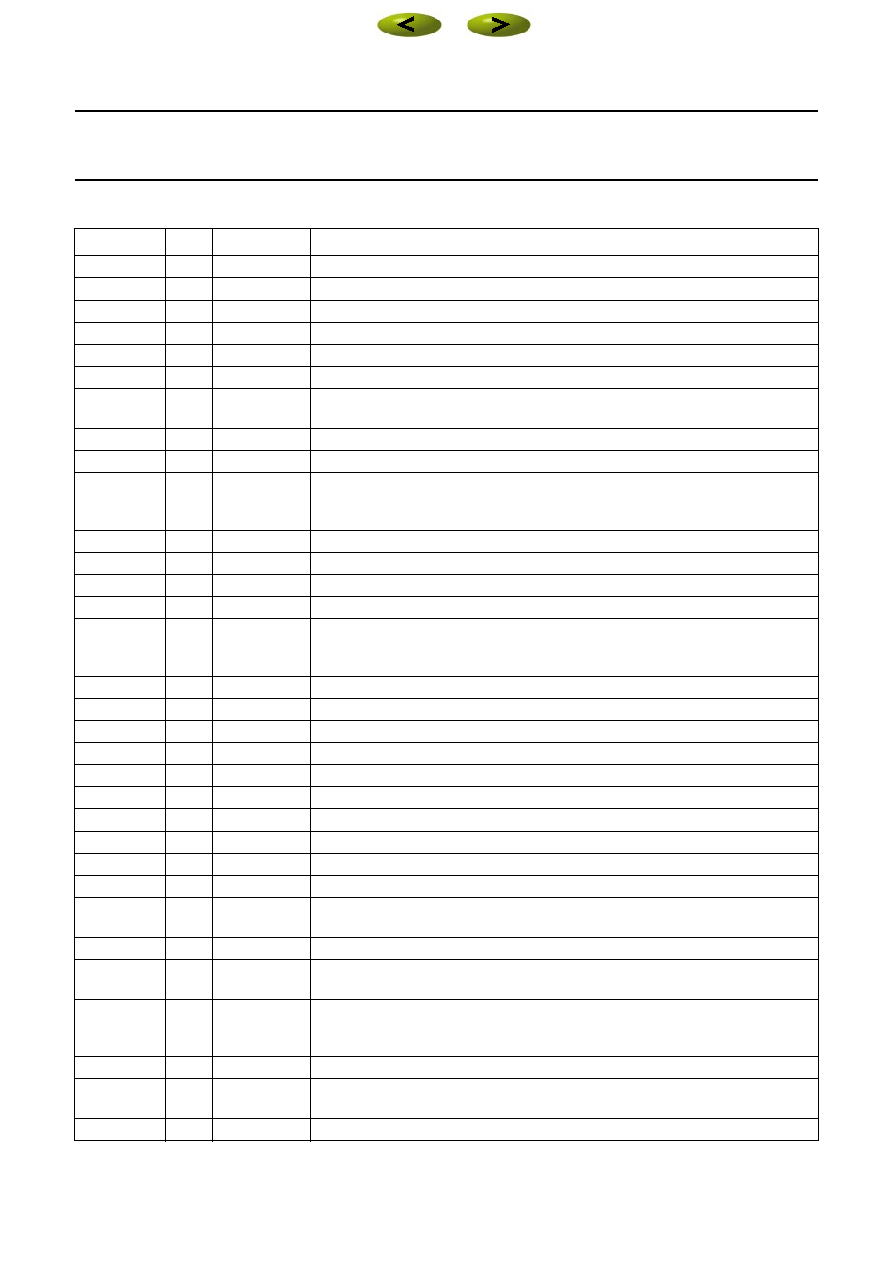

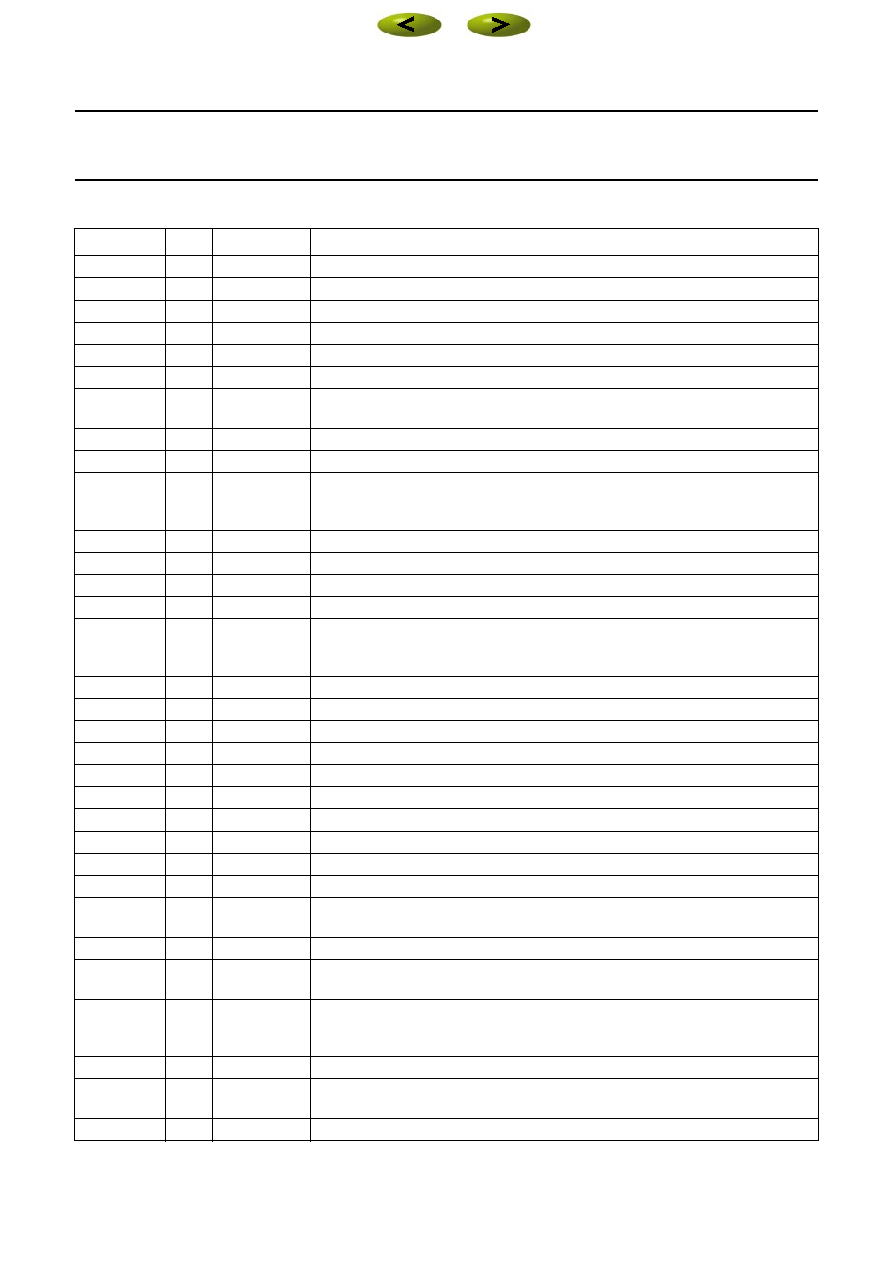

PINNING

SYMBOL

PIN

TYPE

DESCRIPTION

AGND

1

ground

analog ground

V

CCA

2

supply

analog supply voltage

AGND

3

ground

analog ground

DREF

4

analog output bias voltage for PIN diode (V

CCA

); cathode should be connected to this pin

V

CCA

5

supply

analog supply voltage

AGND

6

ground

analog ground

IPhoto

7

analog input

current input; connect the anode of PIN diode to this pin; DC bias level is

1048 mV

AGND

8

ground

analog ground

AGND

9

ground

analog ground

BWC

10

analog input

bandwidth control pin; default bandwidth is 120 MHz; a resistor should be

connected between V

ref

(pin 11) and BWC (pin 10) to decrease bandwidth, or

between BWC (pin 10) and AGND to increase bandwidth

V

ref

11

analog output band gap reference voltage; nominal value approximately 1.2 V

SUB

12

substrate

substrate pin; to be connected to AGND

DGND

13

ground

digital ground

RFTEST

14

analog input

test pin; not connected; not used in application

OUTSEL

15

CMOS input

output select pin; when OUTSEL is HIGH, CML data outputs are active and

PECL data outputs are disabled; OUTSEL is pulled LOW if left unconnected,

PECL data outputs will then be active and CML data outputs disabled

DGND

16

ground

digital ground

V

CCD

17

supply

digital supply voltage

OUTCML

18

CML output

CML data output; OUTCML goes HIGH when current flows into IPhoto (pin 7)

OUTQCML

19

CML output

CML compliment of OUTCML (pin 18)

V

CCD

20

supply

digital supply voltage

DGND

21

ground

digital ground

OUTPECL

22

PECL output

PECL data output; OUTPECL goes HIGH when current flows into IPhoto (pin 7)

OUTQPECL

23

PECL output

PECL compliment of OUTPECL (pin 22)

DGND

24

ground

digital ground

DGND

25

ground

digital ground

LOS

26

PECL output

PECL-compatible LOS detection pin; LOS output is HIGH when the input signal

is below the user programmable threshold level

LOSQ

27

PECL output

PECL compliment of LOS (pin 26)

LOSTTL

28

TTL output

CMOS-compatible LOS detection pin; the LOSTTL output is HIGH when the

input signal is below the user programmable threshold level

LOSTH

29

analog I/O

pin for setting input threshold level; nominal DC voltage is V

CCA

-

1.5 V;

threshold level set by connecting an external resistor between LOSTH and

V

CCA

or by forcing a current into LOSTH; default value for this resistor is 400 k

AGND

30

ground

analog ground

AGC

31

analog I/O

AGC monitor voltage; the internal AGC circuit can be disabled by applying an

external voltage to this pin

AGND

32

ground

analog ground