Philips Semiconductors Advanced BiCMOS Products

Product specification

MB2543

Dual octal latched transceivers with dual enable

(3-State)

1

August 23, 1993

8531656 10584

FEATURES

·

Two 8-bit octal transceivers with D-type

latch

·

Live insertation/extraction permitted

·

Power-up 3-State

·

Power-up reset

·

Multiple V

CC

and GND pins minimize

switching noise

·

Back-to-back registers for storage

·

Separate controls for data flow in each

direction

·

Output capability: +64mA/32mA

·

Latch-up protection exceeds 500mA per

Jedec JC40.2 Std 17

·

ESD protection exceeds 2000V per MIL

STD 883 Method 3015 and 200V per

Machine Model

DESCRIPTION

The MB2543 high-performance BiCMOS

device combines low static and dynamic

power dissipation with high speed and high

output drive.

The MB2543 dual octal registered transceiver

contains two sets of D-type latches for

temporary storage of data flowing in either

direction. Separate Latch Enable (nLEAB,

nLEBA) and Output Enable (nOEAB,

nOEBA) inputs are provided for each

register to permit independent control of data

transfer in either direction. The outputs are

guaranteed to sink 64mA.

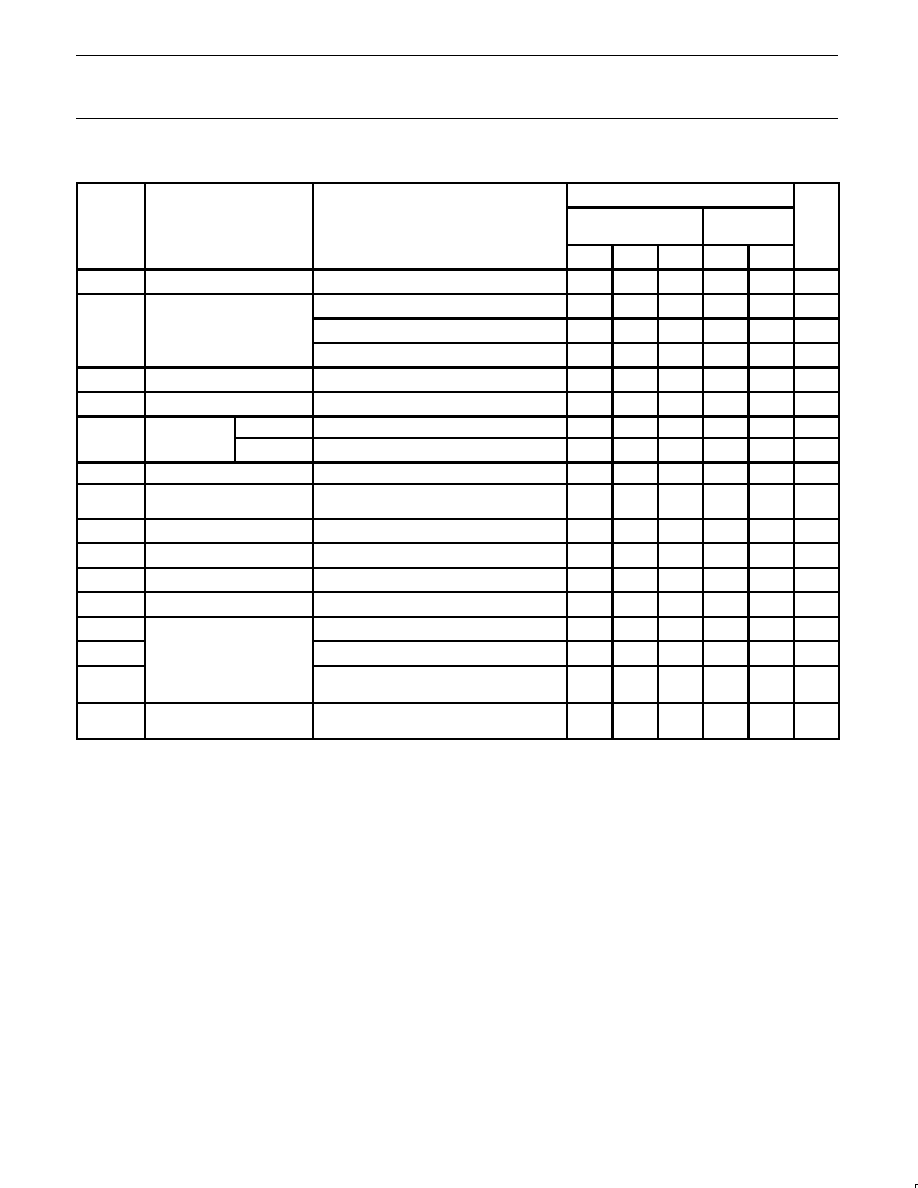

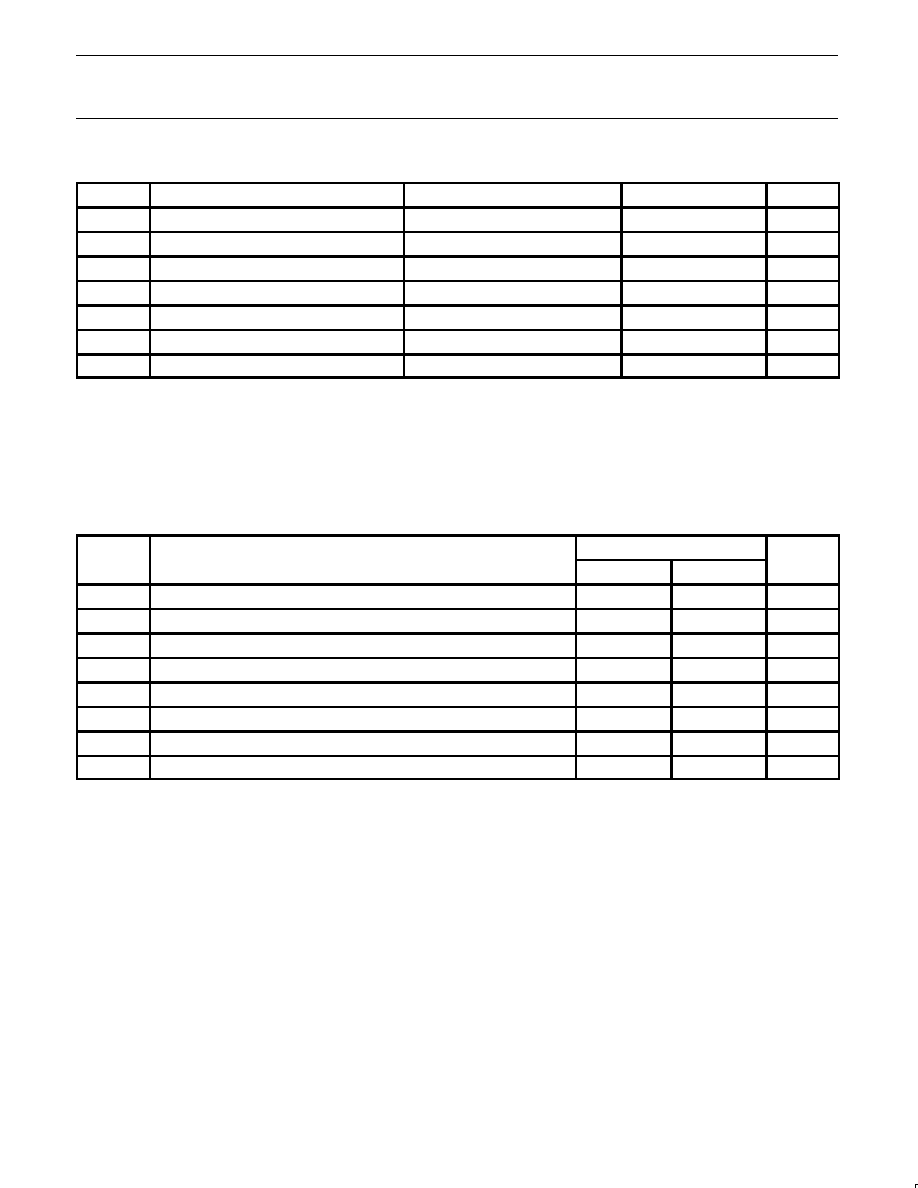

QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

T

amb

= 25

°

C; GND = 0V

TYPICAL

UNIT

t

PLH

t

PHL

Propagation delay

nAx to nBx

C

L

= 50pF; V

CC

= 5V

3.3

ns

C

IN

Input capacitance

V

I

= 0V or V

CC

4

pF

C

I/O

I/O capacitance

V

O

= 0V or V

CC;

3-State

7

pF

I

CCZ

Total supply current

Outputs disabled; V

CC

= 5.5V

120

µ

A

ORDERING INFORMATION

PACKAGES

TEMPERATURE RANGE

ORDER CODE

DRAWING NUMBER

52-pin plastic Quad Flat Pack

40

°

C to +85

°

C

MB2543BB

1418B

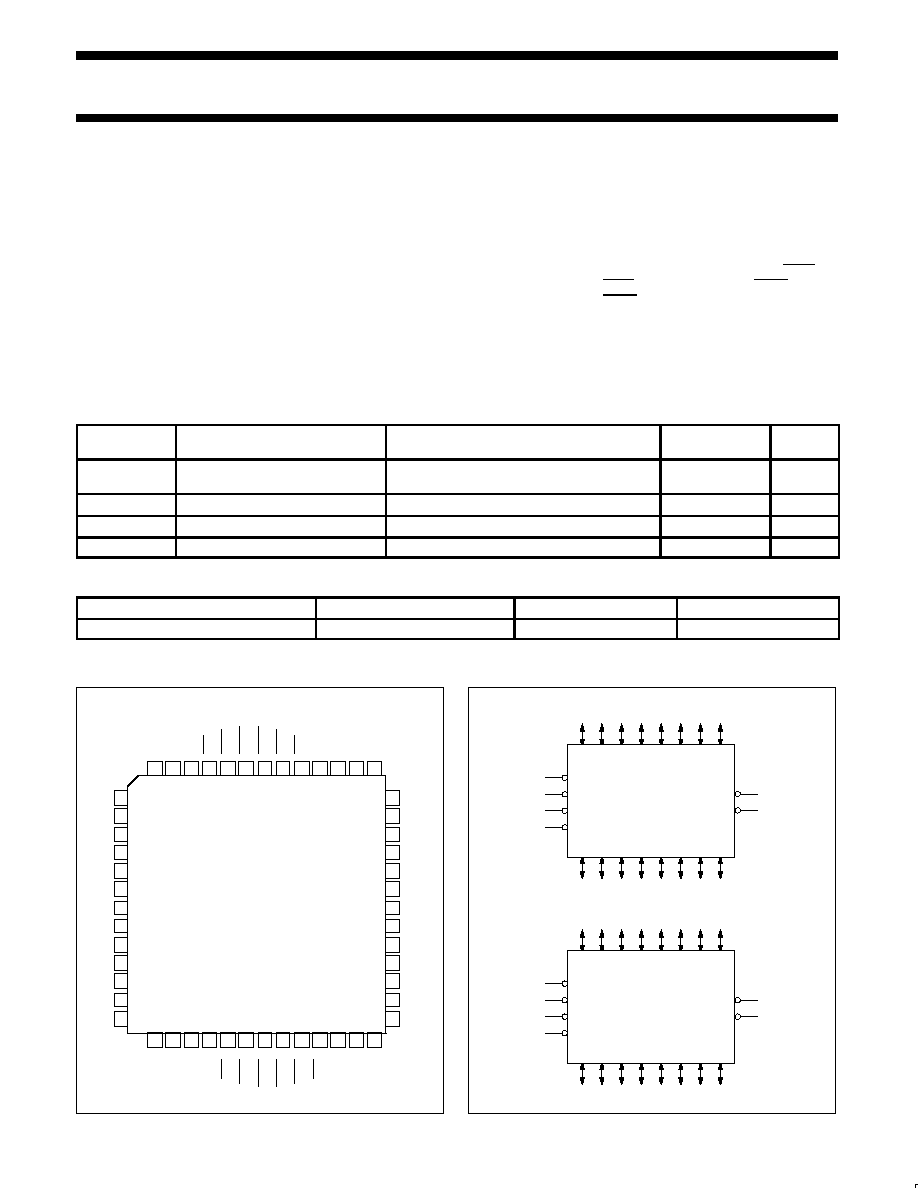

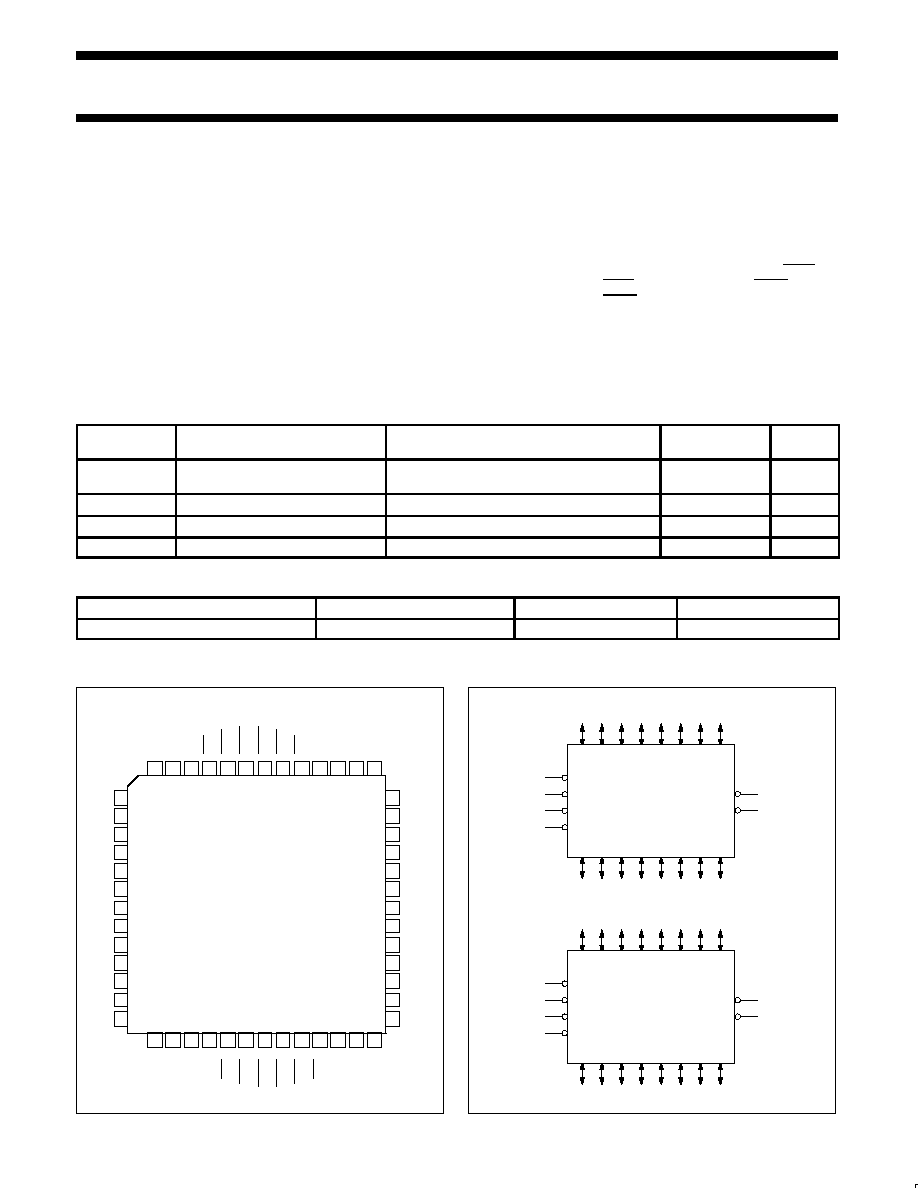

PIN CONFIGURATION

LOGIC SYMBOL

Vcc

19

22

20

23

17

16

25

26

24

15

14

21

18

2A6

2A7

GND

2EAB

2LEAB

2OEAB

2OEBA

2LEBA

2EBA

2B7

2B6

Vcc

Vcc

1A2

1A3

1A4

GND

1A5

1A6

1A7

2A0

2A1

2A2

2A3

2A4

2A5

1

2

3

4

5

6

7

8

9

10

11

12

13

47

44

46

43

49

50

41 40

42

51

52

45

48

1B2

1B3

1B4

1B5

1B6

1B7

2B0

2B1

2B2

GND

2B3

2B4

2B5

39

38

37

36

35

34

33

32

31

30

29

28

27

MB2543

52-pin PQFP

1A1

1A0

1EAB

1LEAB

1OEAB

1OEBA

1LEBA

1EBA

GND

1B0

1B1

Vcc

42

41

39

38

37

36

35

34

1B0 1B1 1B2 1B3 1B4 1B5 1B6 1B7

50

51

1

2

3

5

6

7

1A0 1A1 1A2 1A3 1A4 1A5 1A6 1A7

49

44

1EAB

1EBA

48

1LEAB

45

1LEBA

47

1OEAB

46

1OEBA

33

32

31

29

28

27

25

24

2B0 2B1 2B2 2B3 2B4 2B5 2B6 2B7

8

9

10

11

12

13

15

16

2A0 2A1 2A2 2A3 2A4 2A5 2A6 2A7

18

23

2EAB

2EBA

19

2LEAB

22

2LEBA

20

2OEAB

21

2OEBA

Philips Semiconductors Advanced BiCMOS Products

Product specification

MB2543

Dual octal latched transceivers with dual enable

(3-State)

August 23, 1993

2

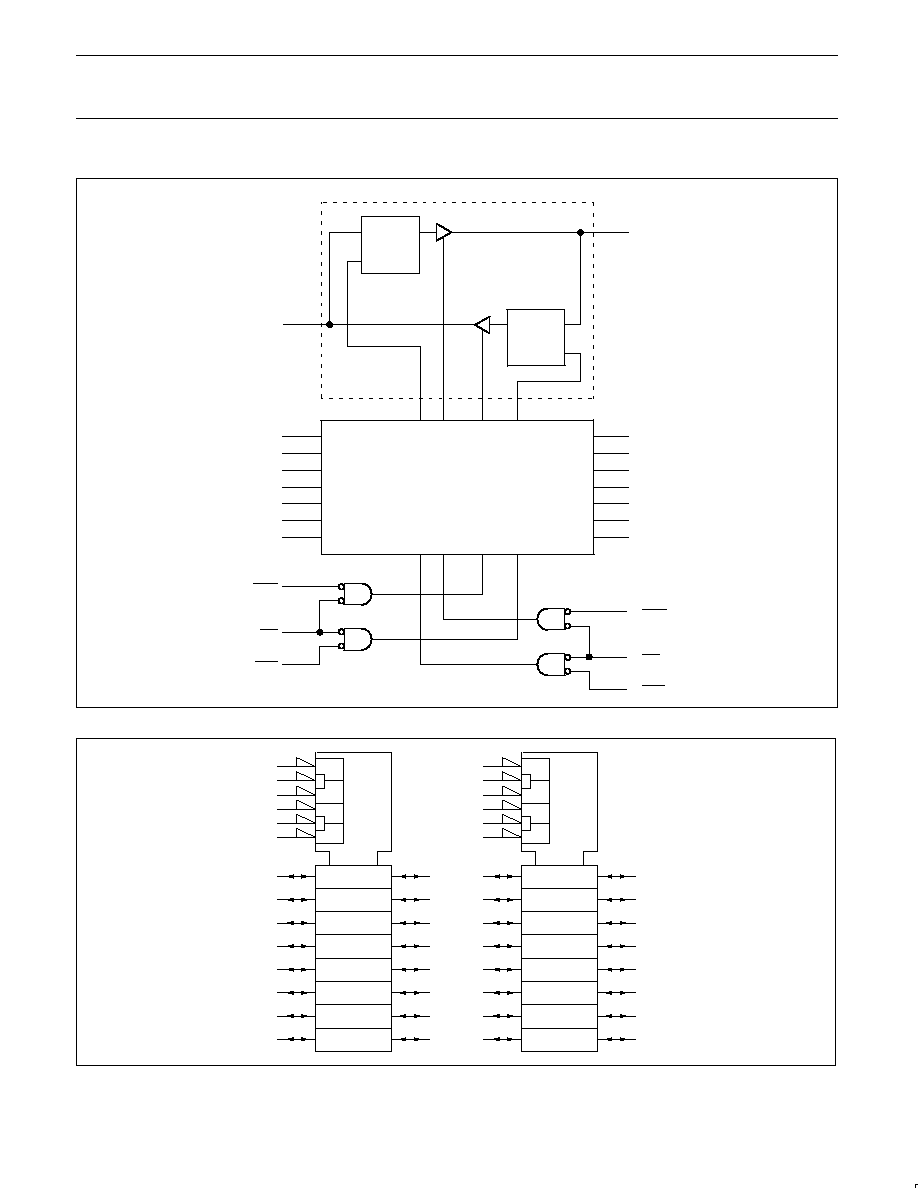

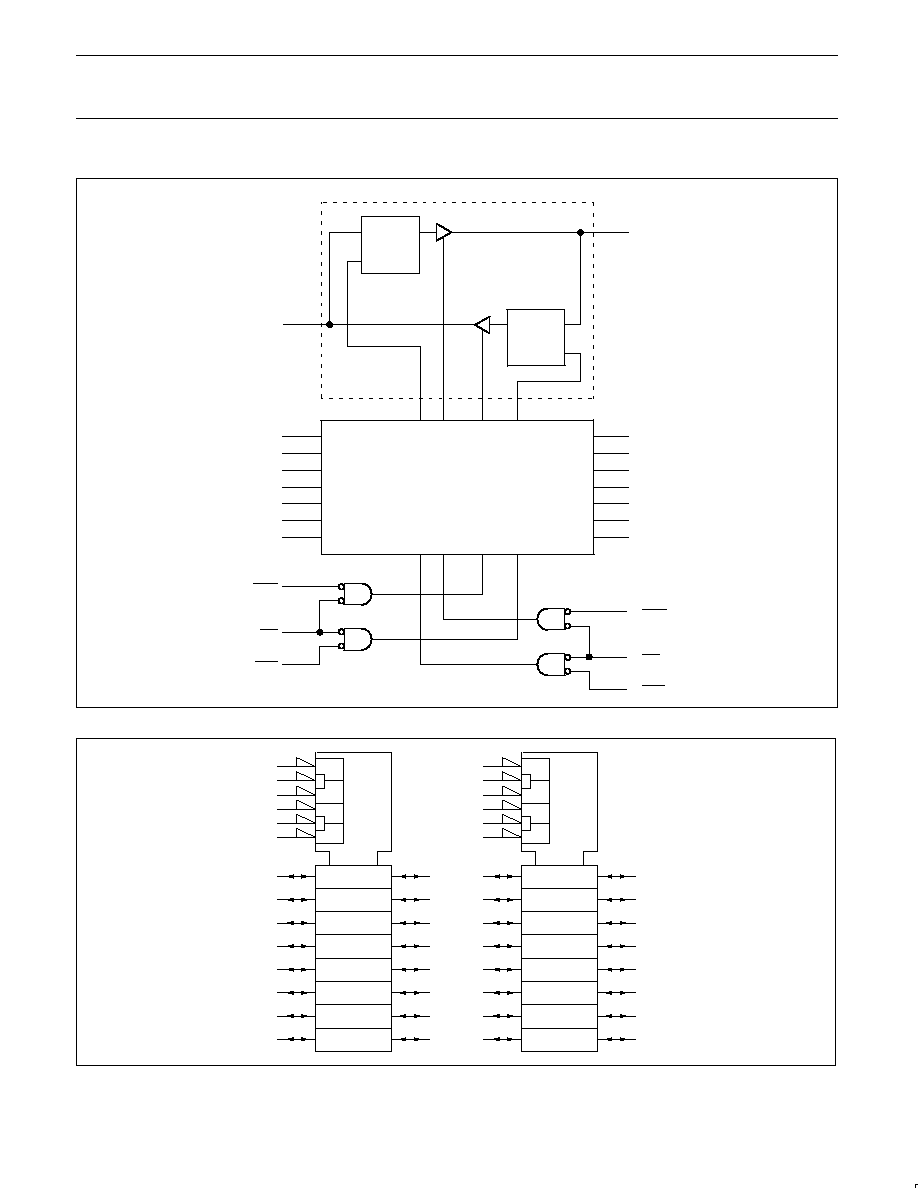

LOGIC DIAGRAM

D

LE

Q

D

LE

Q

DETAIL A

nB0

nB1

nA1

nB2

nA2

nB3

nA3

nB4

nA4

nB5

nA5

nB6

nA6

nB7

nA7

DETAIL A X 7

nOEAB

nEAB

nLEAB

nOEBA

nEBA

nLEBA

nA0

LOGIC SYMBOL (IEEE/IEC)

42

41

39

38

37

36

35

34

&

&

&

&

50

51

1

2

3

5

6

7

47

49

48

46

44

45

EN1(AB)

EN2(BA)

1

&

&

&

&

8

9

10

11

12

13

15

16

20

18

19

21

23

22

EN1(AB)

EN2(BA)

33

32

31

29

28

27

25

24

1

2

2

Philips Semiconductors Advanced BiCMOS Products

Product specification

MB2543

Dual octal latched transceivers with dual enable

(3-State)

August 23, 1993

3

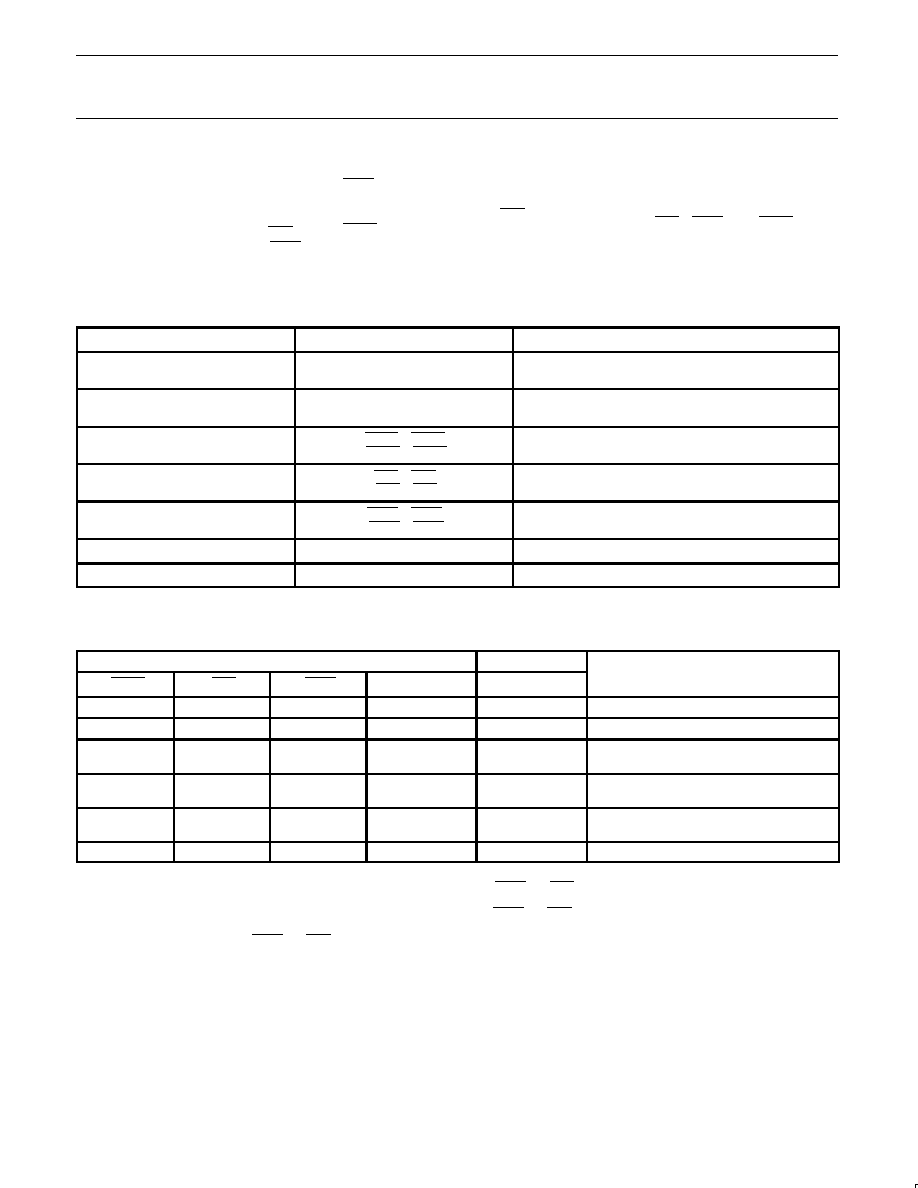

FUNCTIONAL DESCRIPTION

The MB2543 contains two sets of eight

D-type latches, with separate control pins for

each set. Using data flow from A to B as an

example, when the A-to-B Enable (nEAB)

input and the A-to-B Latch Enable (nLEAB)

input are Low the A-to-B path is transparent.

A subsequent Low-to-High transition of the

nLEAB signal puts the A data into the latches

where it is stored and the B outputs no longer

change with the A inputs. With EAB and

nOEAB both Low, the 3-State B output

buffers are active and display the data

present at the outputs of the A latches.

Control of data flow from B to A is similar, but

using the nEBA, nLEBA, and nOEBA inputs.

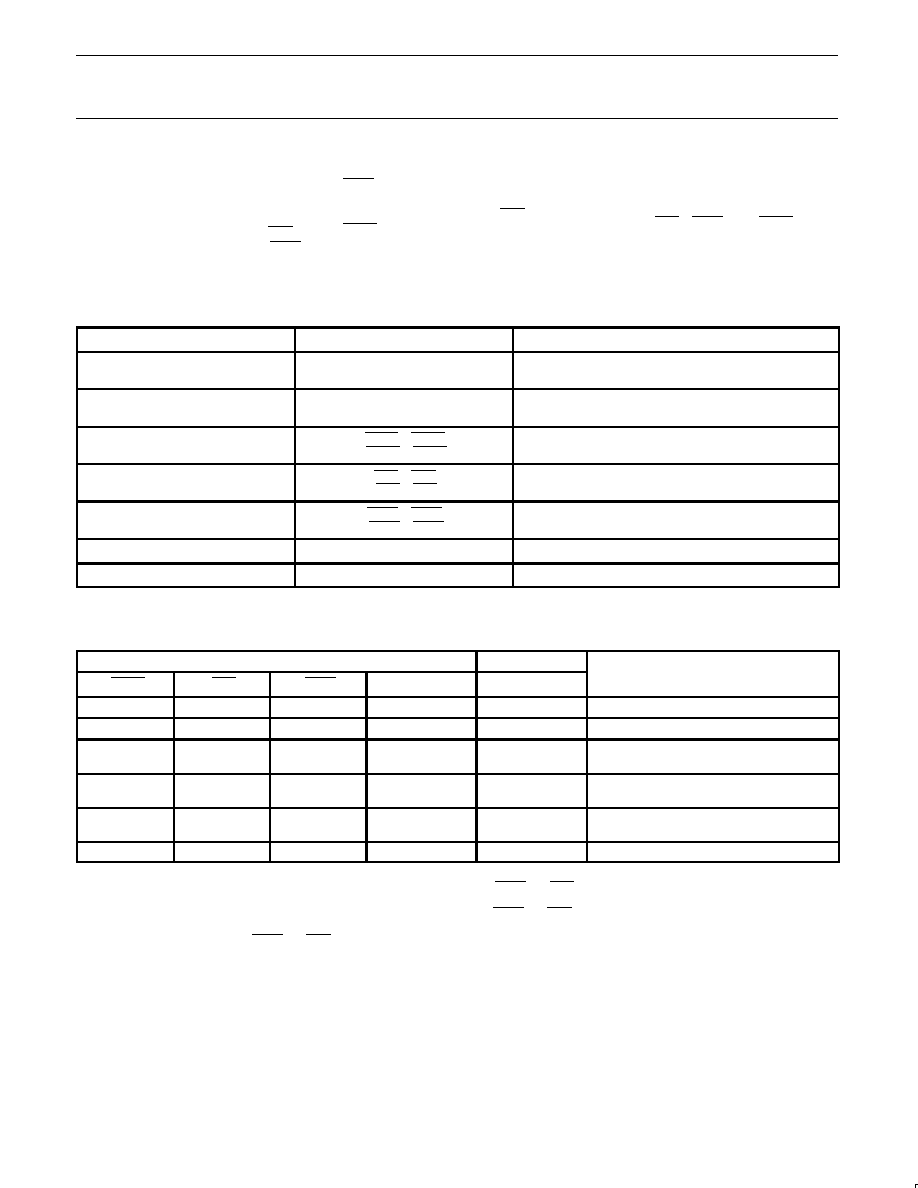

PIN DESCRIPTION

PIN NUMBER

SYMBOL

NAME AND FUNCTION

50, 51, 1, 2, 3, 5, 6, 7,

8, 9, 10, 11, 12, 13, 15, 16

1A0 1A7,

2A0 2A7

Data inputs/outputs

42, 41, 39, 38, 37, 36, 35, 34,

33, 32, 31, 29, 28, 27, 25, 24

1B0 1B7,

2B0 2B7

Data inputs/outputs

47, 46, 20, 21

1OEAB, 1OEBA,

2OEAB, 2OEBA

A to B / B to A Output Enable inputs (active-Low)

49, 44, 18, 23

1EAB, 1EBA,

2EAB, 2EBA

A to B / B to A Enable inputs (active-Low)

48, 45, 19, 22

1LEAB, 1LEBA,

2LEAB, 2LEBA

A to B / B to A Latch Enable inputs (active-Low)

4, 17, 30, 43

GND

Ground (0V)

14, 26, 40, 52

V

CC

Positive supply voltage

FUNCTION TABLE

INPUTS

OUTPUTS

STATUS

nOEXX

nEXX

nLEXX

nAx or nBx

nBx or nAx

H

X

X

X

Z

Disabled

X

H

X

X

Z

Disabled

L

L

L

L

h

l

Z

Z

Disabled + Latch

L

L

L

L

h

l

H

L

Latch + Display

L

L

L

L

L

L

H

L

H

L

Transparent

L

L

H

X

NC

Hold

H = High voltage level

h

= High voltage level one set-up time prior to the Low-to-High transition of nLEXX or nEXX (XX = AB or BA)

L

= Low voltage level

l

= Low voltage level one set-up time prior to the Low-to-High transition of nLEXX or nEXX (XX = AB or BA)

X = Don't care

= Low-to-High transition of nLEXX or nEXX (XX = AB or BA)

NC= No change

Z = High impedance or "off" state

Philips Semiconductors Advanced BiCMOS Products

Product specification

MB2543

Dual octal latched transceivers with dual enable

(3-State)

August 23, 1993

4

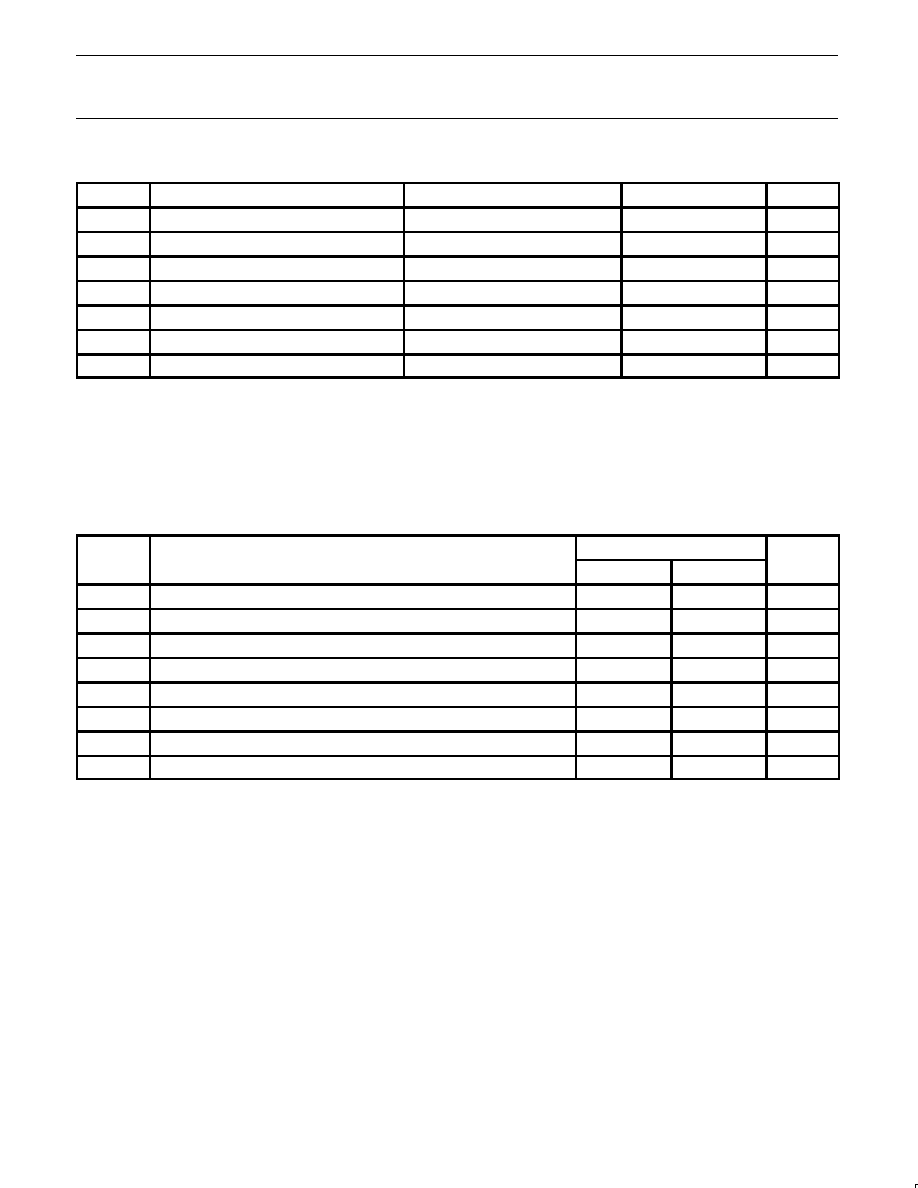

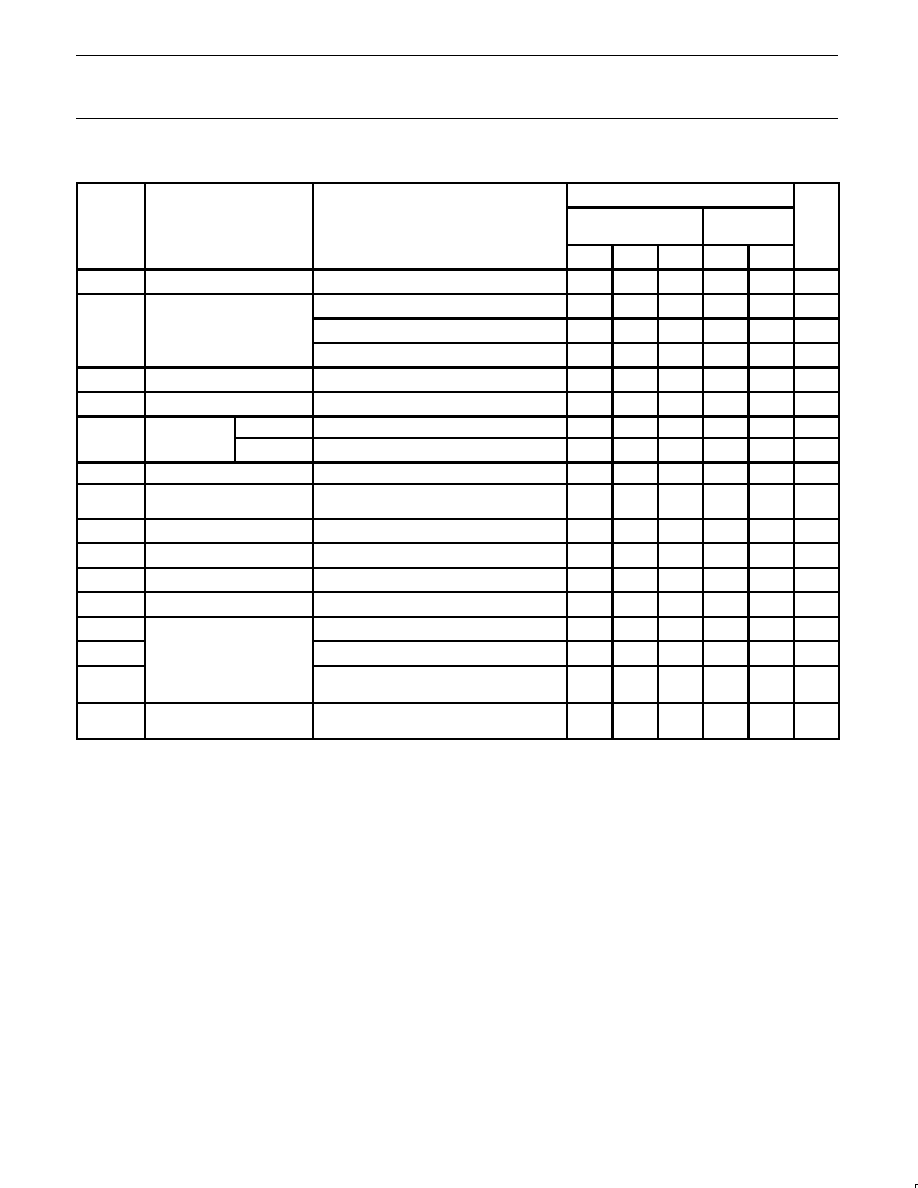

ABSOLUTE MAXIMUM RATINGS

1 , 2

SYMBOL

PARAMETER

CONDITIONS

RATING

UNIT

V

CC

DC supply voltage

0.5 to +7.0

V

I

IK

DC input diode current

V

I

< 0

18

mA

V

I

DC input voltage

3

1.2 to +7.0

V

I

OK

DC output diode current

V

O

< 0

50

mA

V

OUT

DC output voltage

3

output in Off or High state

0.5 to +5.5

V

I

OUT

DC output current

output in Low state

128

mA

T

stg

Storage temperature range

65 to 150

°

C

NOTES:

1 . Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability.

2 . The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150

°

C.

3 . The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

LIMITS

UNIT

Min

Max

V

CC

DC supply voltage

4.5

5.5

V

V

I

Input voltage

0

V

CC

V

V

IH

High-level input voltage

2.0

V

V

IL

Low-level Input voltage

0.8

V

I

OH

High-level output current

32

mA

I

OL

Low-level output current

64

mA

t/

v

Input transition rise or fall rate

0

10

ns/V

T

amb

Operating free-air temperature range

40

+85

°

C

Philips Semiconductors Advanced BiCMOS Products

Product specification

MB2543

Dual octal latched transceivers with dual enable

(3-State)

August 23, 1993

5

DC ELECTRICAL CHARACTERISTICS

LIMITS

SYMBOL

PARAMETER

TEST CONDITIONS

T

amb

= +25

°

C

T

amb

= 40

°

C

to +85

°

C

UNIT

MIN

TYP

MAX

MIN

MAX

V

IK

Input clamp voltage

V

CC

= 4.5V; I

IK

= 18mA

0.9

1.2

1.2

V

V

CC

= 4.5V; I

OH

= 3mA; V

I

= V

IL

or V

IH

2.5

2.9

2.5

V

V

OH

High-level output voltage

V

CC

= 5.0V; I

OH

= 3mA; V

I

= V

IL

or V

IH

3.0

3.4

3.0

V

V

CC

= 4.5V; I

OH

= 32mA; V

I

= V

IL

or V

IH

2.0

2.4

2.0

V

V

OL

Low-level output voltage

V

CC

= 4.5V; I

OL

= 64mA; V

I

= V

IL

or V

IH

0.42

0.55

0.55

V

V

RST

Power-up output voltage

3

V

CC

= 5.5V; I

O

= 1mA; V

I

= GND or V

CC

0.13

0.55

0.55

V

I

I

Input leakage

Control pins

V

CC

= 5.5V; V

I

= GND or 5.5V

±

0.01

±

1.0

±

1.0

µ

A

current

Data pins

V

CC

= 5.5V; V

I

= GND or 5.5V

±

5

±

100

±

100

µ

A

I

OFF

Power-off leakage current

V

CC

= 0.0V; V

O

or V

I

4.5V

±

5.0

±

100

±

100

µ

A

I

PU/PD

Power-up/down 3-State

output current

4

V

CC

= 2.1V; V

O

= 0.5V; V

I

= GND or V

CC

;

V

OE

= Don't care

±

5.0

±

50

±

50

µ

A

I

IH

+ I

OZH

3-State output High current

V

CC

= 5.5V; V

O

= 2.7V; V

I

= V

IL

or V

IH

5.0

50

50

µ

A

I

IL

+ I

OZL

3-State output Low current

V

CC

= 5.5V; V

O

= 0.5V; V

I

= V

IL

or V

IH

5.0

50

50

µ

A

I

CEX

Output High leakage current

V

CC

= 5.5V; V

O

= 5.5V; V

I

= GND or V

CC

5.0

50

50

µ

A

I

O

Output current

1

V

CC

= 5.5V; V

O

= 2.5V

50

100

180

50

180

mA

I

CCH

V

CC

= 5.5V; Outputs High, V

I

= GND or V

CC

120

250

250

µ

A

I

CCL

Quiescent supply current

V

CC

= 5.5V; Outputs Low, V

I

= GND or V

CC

38

60

60

mA

I

CCZ

V

CC

= 5.5V; Outputs 3-State;

V

I

= GND or V

CC

120

250

250

µ

A

I

CC

Additional supply current per

input pin

2

V

CC

= 5.5V; one input at 3.4V,

other inputs at V

CC

or GND

0.5

1.5

1.5

mA

NOTES:

1 . Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

2 . This is the increase in supply current for each input at 3.4V.

3 . For valid test results, data must not be loaded into the flip-flops (or latches) after applying the power.

4 . This parameter is valid for any V

CC

between 0V and 2.1V, with a transition time of up to 10msec. From V

CC

= 2.1V to V

CC

= 5V

±

10% a

transition time of up to 100

µ

sec is permitted.