ę

Semiconductor Components Industries, LLC, 1999

December, 1999 ş Rev. 6

1

Publication Order Number:

SN74LS299/D

SN74LS299

8-Bit Shift/Storage Register

with 3-State Outputs

The SN74LS299 is an 8-Bit Universal Shift / Storage Register with

3-state outputs. Four modes of operation are possible: hold (store),

shift left, shift right and load data.

The parallel load inputs and flip-flop outputs are multiplexed to

reduce the total number of package pins. Separate outputs are provided

for flip-flops Q

0

and Q

7

to allow easy cascading. A separate active

LOW Master Reset is used to reset the register.

Ě

Common I/O for Reduced Pin Count

Ě

Four Operation Modes: Shift Left, Shift Right, Load and Store

Ě

Separate Shift Right Serial Input and Shift Left Serial Input for Easy

Cascading

Ě

3-State Outputs for Bus Oriented Applications

Ě

Input Clamp Diodes Limit High-Speed Termination Effects

Ě

ESD > 3500 Volts

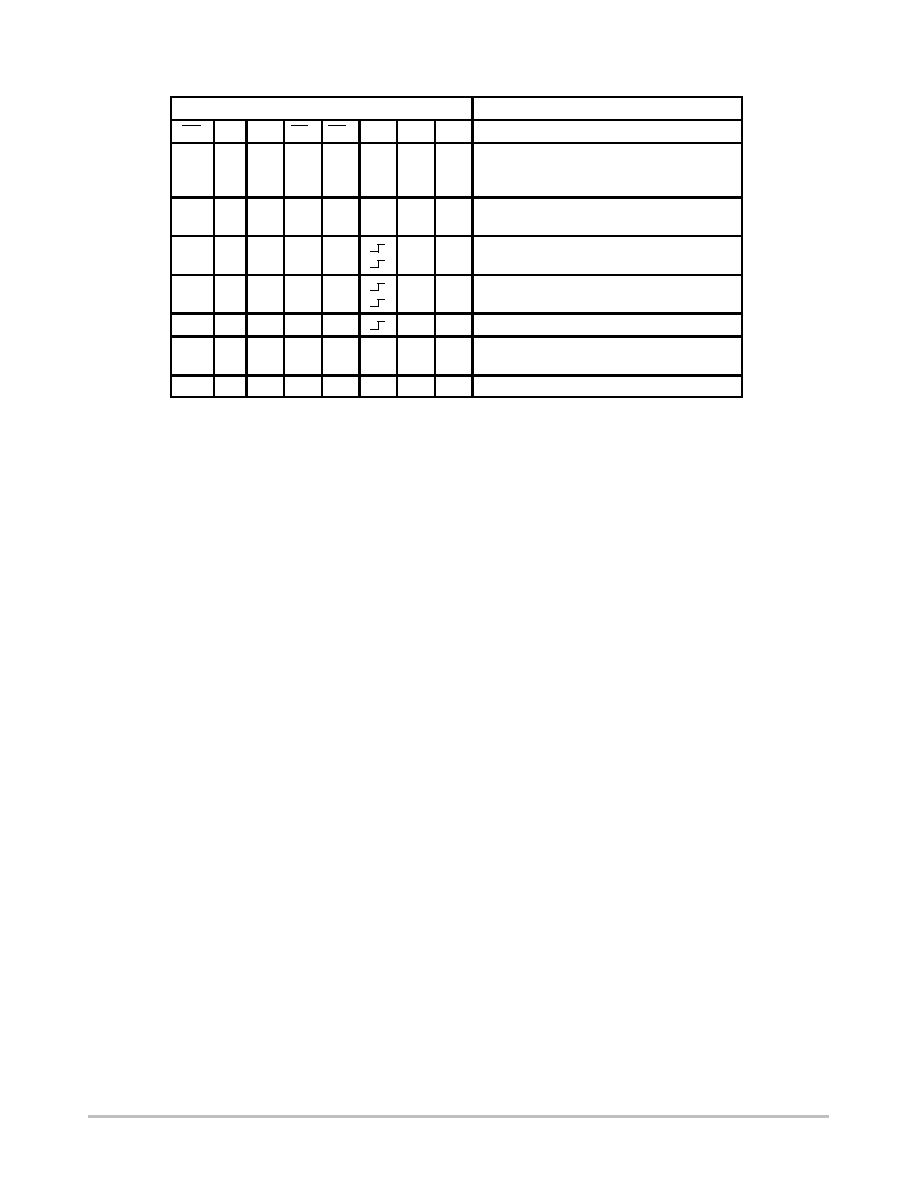

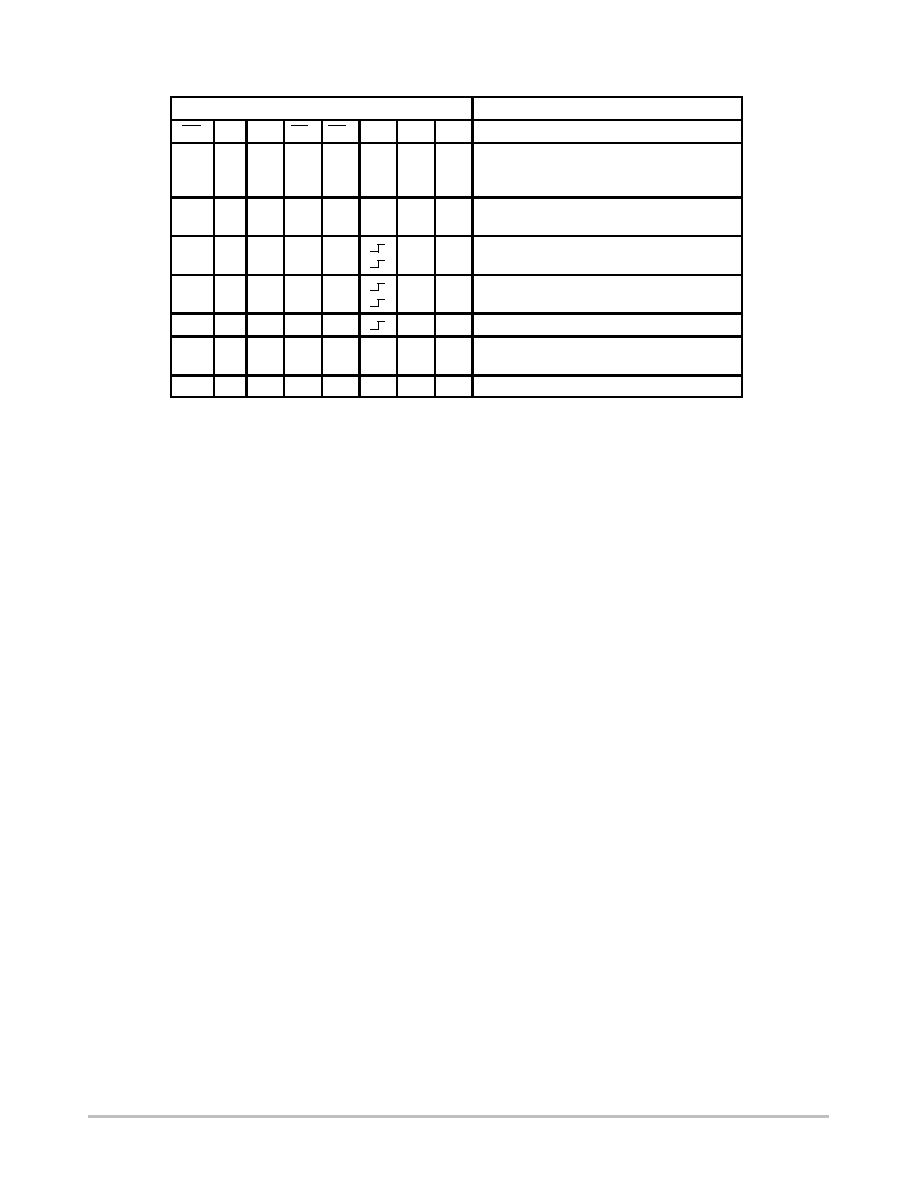

GUARANTEED OPERATING RANGES

Symbol

Parameter

Min

Typ

Max

Unit

V

CC

Supply Voltage

4.75

5.0

5.25

V

T

A

Operating Ambient

Temperature Range

0

25

70

░

C

I

OH

Output Current ş High

Q

0

, Q

7

ş 0.4

mA

I

OL

Output Current ş Low

Q

0

, Q

7

8.0

mA

I

OH

Output Current ş High

I/O

0

ş 1/O

7

ş 2.6

mA

I

OL

Output Current ş Low

I/O

0

ş 1/O

7

24

mA

LOW

POWER

SCHOTTKY

Device

Package

Shipping

ORDERING INFORMATION

SN74LS299N

16 Pin DIP

1440 Units/Box

SN74LS299DW

16 Pin

SOIC

DW SUFFIX

CASE 751D

http://onsemi.com

2500/Tape & Reel

PLASTIC

N SUFFIX

CASE 738

20

1

20

1

SN74LS299

http://onsemi.com

2

CONNECTION DIAGRAM DIP (TOP VIEW)

Clock Pulse (Active PositiveşGoing Edge) Input

Serial Data Input for Right Shift

Serial Data Input for Left Shift

Parallel Data Input or

Parallel Output (3şState)

3şState Output Enable (Active LOW) Inputs

Serial Outputs

Asynchronous Master Reset (Active LOW) Input

Mode Select Inputs

CP

DS0

DS7

I/O

n

OE

1

, OE

2

Q

0

, Q

7

MR

S

0

, S

1

0.5 U.L.

0.5 U.L.

0.5 U.L.

0.5 U.L.

65 U.L.

0.5 U.L.

10 U.L.

0.5 U.L.

1 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

15 U.L.

0.25 U.L.

5 U.L.

0.25 U.L.

0.5 U.L.

NOTES:

a) 1 TTL Unit Load (U.L.) = 40

mA HIGH/1.6 mA LOW.

HIGH

LOW

(Note a)

LOADING

PIN NAMES

18

17

16

15

14

13

1

2

3

4

5

6

7

20

19

8

V

CC

S

0

S

1

D

s7

Q

7

I/O

7

I/O

3

I/O

5

I/O

1

OE

1

OE

2

I/O

6

I/O

4

I/O

2

I/O

0

Q

0

9

10

MR GND

12

11

CP

DS

0

NOTE:

The Flatpak version has the same

pinouts (Connection Diagram) as

the Dual In-Line Package.

S

1

S

0

DS

0

CLOCK

Q

0

MR

OE

1

OE

2

D

CLR

Q

CK

I/O

0

I/O

1

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

D

S7

Q

7

V

CC

= PIN 20

GND = PIN 10

= PIN NUMBERS

14

1

2

6

7

3

8

4

5

9

11

12

13

15

16

17

18

19

D

CLR

Q

CK

D

CLR

Q

CK

D

CLR

Q

CK

D

CLR

Q

CK

D

CLR

Q

CK

D

CLR

Q

CK

D

CLR

Q

CK

LOGIC DIAGRAM

SN74LS299

http://onsemi.com

3

FUNCTION TABLE

INPUTS

RESPONSE

MR

S

1

S

0

OE

1

OE

2

CP

DS

0

DS

7

L

X

X

H

X

X

X

X

Asynchronous Reset; Q

0

= Q

7

= LOW

L

X

X

X

H

X

X

X

Asynchronous Reset Q

0

= Q

7

= LOW

I/O Voltage Undetermined

L

H

H

X

X

X

X

X

I/O Voltage Undetermined

L

L

X

L

L

X

X

X

Asynchronous Reset; Q

0

= Q

7

= LOW

L

X

L

L

L

X

X

X

I/O Voltage LOW

H

L

H

X

X

D

X

Shift Right; D

│

Q

0

; Q

0

│

Q

1

; etc.

H

L

H

L

L

D

X

Shift Right; D

│

Q

0

& I/O

0

; Q

0

│

O

1

& I/O

1

; etc.

H

H

L

X

X

X

D

Shift Left; D

│

Q

7

; Q

7

│

Q

6

; etc.

H

H

L

L

L

X

D

Shift Left; D

│

Q

7

& I/O

7

; Q

7

│

Q

6

& I/O

6

; etc.

H

H

H

X

X

X

X

Parallel Load; I/O

n

│

Q

n

H

L

L

H

X

X

X

X

Hold: I/O Voltage undetermined

H

L

L

X

H

X

X

X

Hold: I/O Voltage undetermined

H

L

L

L

L

X

X

X

Hold: I/O

n

= Q

n

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

SN74LS299

http://onsemi.com

4

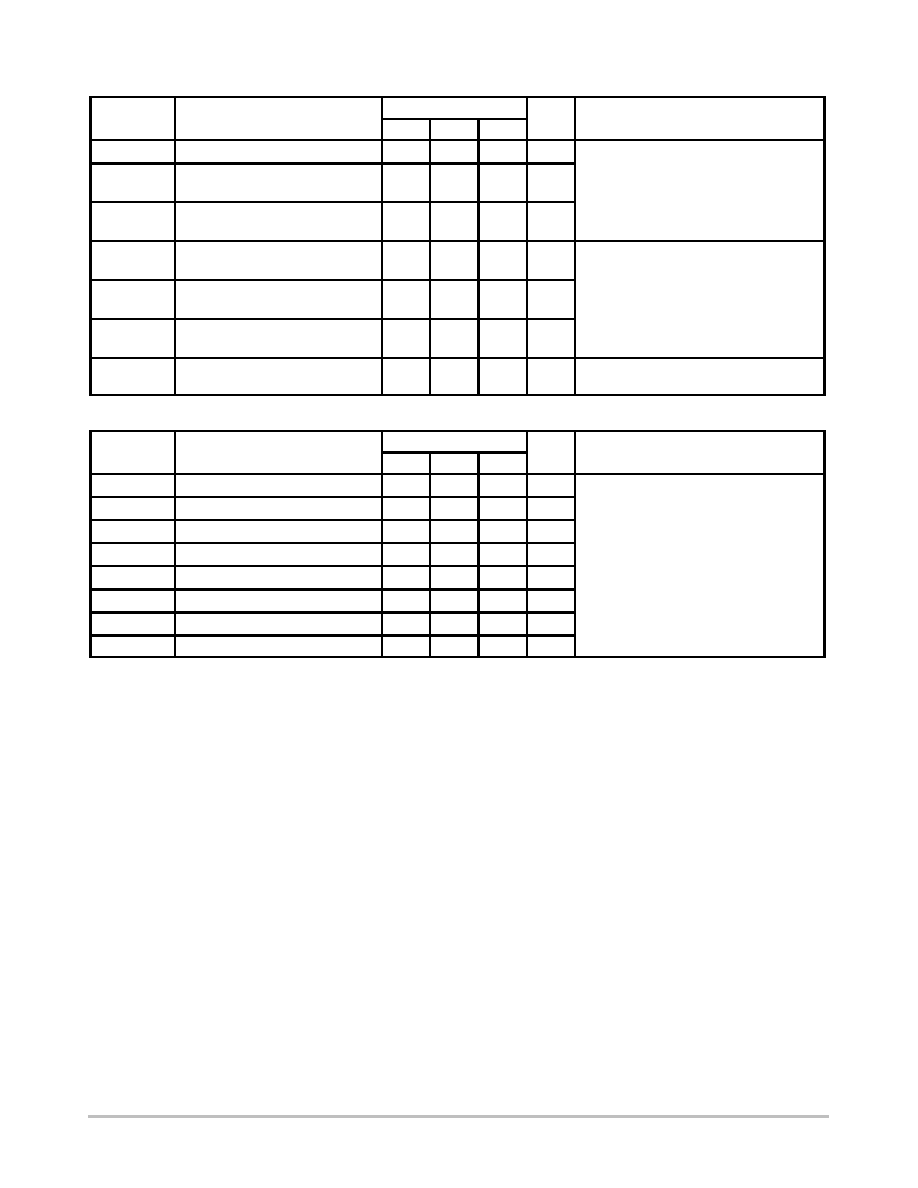

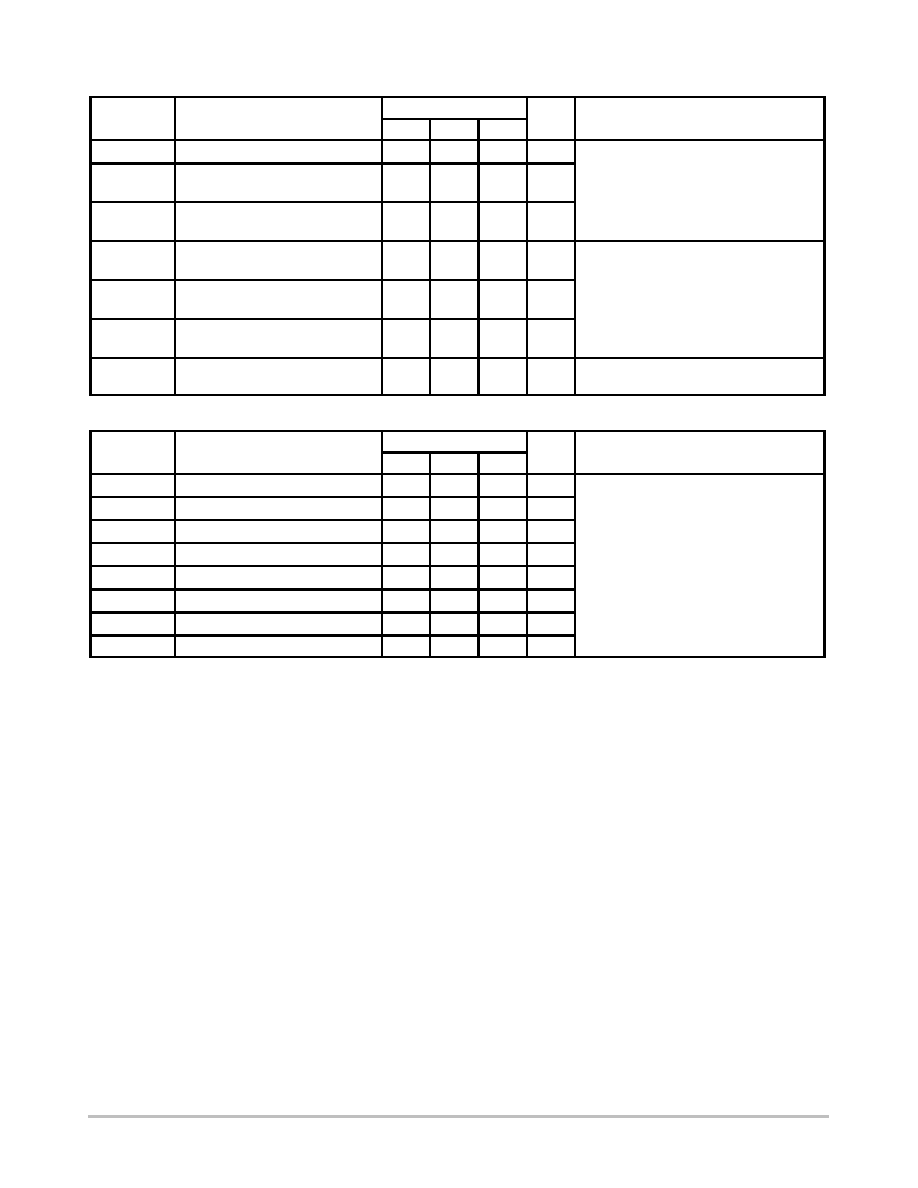

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

(unless otherwise specified)

Limits

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

V

IH

Input HIGH Voltage

2.0

V

Guaranteed Input HIGH Voltage for

All Inputs

V

IL

Input LOW Voltage

0.8

V

Guaranteed Input LOW Voltage for

All Inputs

V

IK

Input Clamp Diode Voltage

ş 0.65

ş 1.5

V

V

CC

= MIN, I

IN

= ş 18 mA

V

OH

Output HIGH Voltage

I/O

0

ş I/O

7

2.4

3.1

V

V

CC

= MIN, I

OH

= MAX

V

OH

Output HIGH Voltage

Q

0

, Q

7

2.7

3.4

V

V

CC

= MIN, I

OH

= MAX

V

O

Output LOW Voltage

0.25

0.4

V

I

OL

= 12 mA

V

CC

= V

CC

MIN,

V

IN

= V

IL

or V

IH

V

OL

g

I/O

0

ş I/O

7

0.35

0.5

V

I

OL

= 24 mA

V

IN

= V

IL

or V

IH

per Truth Table

V

O

Output LOW Voltage

0.4

V

I

OL

= 4.0 mA

V

CC

= V

CC

MIN,

V

IN

= V

IL

or V

IH

V

OL

g

I/O

0

ş I/O

7

0.5

V

I

OL

= 8.0 mA

V

IN

= V

IL

or V

IH

per Truth Table

I

OZH

Output Off Current HIGH

I/O

0

ş I/O

7

40

Á

A

V

CC

= MAX, V

OUT

= 2.7 V

I

OZL

Output Off Current LOW

I/O

0

ş I/O

7

ş 400

Á

A

V

CC

= MAX, V

OUT

= 0.4 V

Others

20

Á

A

I

I

t HIGH C

t

S

0

, S

1

,

I/O

0

ş I/O

7

40

Á

A

V

CC

= MAX, V

IN

= 2.7 V

I

IH

Input HIGH Current

Others

0.1

mA

V

CC

= MAX V

= 7 0 V

S

0

, S

1

0.2

mA

V

CC

= MAX, V

IN

= 7.0 V

I/O

0

ş I/O

7

0.1

mA

V

CC

= MAX, V

IN

= 5.5 V

I

Input LOW Current

Others

ş 0.4

mA

V

CC

= MAX V

= 0 4 V

I

IL

Input LOW Current

S

0

, S

1

ş 0.8

mA

V

CC

= MAX, V

IN

= 0.4 V

I

OS

Short Circuit Current

Q

0

, Q

7

ş 20

ş100

mA

V

CC

= MAX

(Note 1)

I/O

0

ş I/O

7

ş 30

ş130

mA

V

CC

= MAX

I

CC

Power Supply Current

53

mA

V

CC

= MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

SN74LS299

http://onsemi.com

5

AC CHARACTERISTICS

(T

A

= 25

░

C, V

CC

= 5.0 V)

Limits

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

f

MAX

Maximum Clock Frequency

25

35

MHz

t

PHL

t

PLH

Propagation Delay, Clock

to Q

0

or Q

7

26

22

39

33

ns

C

L

= 15 pF

t

PHL

Propagation Delay, Clear

to Q

0

or Q

7

27

40

ns

t

PHL

t

PLH

Propagation Delay, Clock

to I/O

0

ş I/O

7

26

17

39

25

ns

t

PHL

Propagation Delay, Clear

to I/O

0

ş I/O

7

26

40

ns

C

L

= 45 pF,

R

L

= 667

t

PZH

t

PZL

Output Enable Time

13

19

21

30

ns

t

PHZ

t

PLZ

Output Disable Time

10

10

15

15

ns

C

L

= 5.0 pF

AC SETUP REQUIREMENTS

(T

A

= 25

░

C, V

CC

= 5.0 V)

Limits

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

t

W

Clock Pulse Width HIGH

25

ns

t

W

Clock Pulse Width LOW

13

ns

t

W

Clear Pulse Width LOW

20

ns

t

s

Data Setup Time

20

ns

V

CC

= 5 0 V

t

s

Select Setup Time

35

ns

V

CC

= 5.0 V

t

h

Data Hold Time

0

ns

t

h

Select Hold Time

10

ns

t

rec

Recovery Time

20

ns