Oxford Semiconductor Ltd.

69 Milton Park, Abingdon, Oxon, OX14 4RX, UK

Tel: +44 (0)1235 824900 Fax: +44(0)1235 821141

©

©

Oxford Semiconductor 1999

OX9162 1.0 PRELIMINARY October 1999

Part No. OX9162-TQC-A

F

EATURE

·

8 bit pass-through local bus

·

IEEE1284 SPP/EPP/ECP parallel port

·

Single function target PCI controller, fully PCI 2.2 and

PCI Power Management 1.0 compliant

·

2 multi-purpose IO pins which can be configured as

interrupt input pins

·

Can be reconfigured using optional non-volatile

configuration memory (EEPROM)

·

5.0V operation

·

128 TQFP package

D

ESCRIPTION

The OX9162 is a single chip solution for PCI-based parallel

expansion add-in cards, or local bus bridges. It is a single

function PCI device, where function 0 offers either an 8 bit

Local Bus or a bi-directional parallel port.

For legacy applications the PCI resources are arranged so

that the parallel port can be located at standard I/O

addresses.

The efficient 32-bit, 33MHz target-only PCI interface is

compliant with version 2.2 of the PCI Bus Specification and

version 1.0 of PCI Power Management Specification. For

full flexibility, all the default register values can be

overwritten using an optional Microwire

TM

serial EEPROM.

Bridging applications can be realised using the 8-bit pass-

through Local Bus function. The addressable space can be

increased up to 256 bytes for each chip-select region.

The OX9162 alternatively provides an IEEE1284 EPP/ECP

parallel port which fully supports the existing Centronics

interface. The parallel port can be enabled in place of the

Local Bus.

OX9162

Integrated Parallel Port/Local

Bus and PCI interface

Data Sheet Revision 1.1 PRELIMINARY Page 2

OX9162

OXFORD SEMICONDUCTOR LTD.

C

ONTENTS

1 PIN INFORMATION...................................3

2 PIN DESCRIPTIONS .................................4

3 CONFIGURATION & OPERATION............8

4 PCI TARGET CONTROLLER....................9

4.1

OPERATION............................................................9

4.2

CONFIGURATION SPACE ....................................9

4.2.1

PCI CONFIGURATION SPACE REGISTER

MAP 10

4.3

ACCESSING LOGICAL FUNCTIONS.................11

4.3.1

PCI ACCESS TO 8-BIT LOCAL BUS ..............11

4.3.2

PCI ACCESS TO PARALLEL PORT...............11

4.4

ACCESSING LOCAL CONFIGURATION

REGISTERS ........................................................................12

4.4.1

LOCAL CONFIGURATION AND CONTROL

REGISTER `LCC' (OFFSET 0X00) ....................................12

4.4.2

MULTI-PURPOSE I/O CONFIGURATION

REGISTER `MIC' (OFFSET 0X04).....................................13

4.4.3

LOCAL BUS TIMING PARAMETER REGISTER

1 `LT1' (OFFSET 0X08): .....................................................13

4.4.4

LOCAL BUS TIMING PARAMETER/BAR

SIZING REGISTER 2 `LT2' (OFFSET 0X0C):...................15

4.4.5

GLOBAL INTERRUPT STATUS AND

CONTROL REGISTER `GIS' (OFFSET 0X10).................16

4.5

PCI INTERRUPTS.................................................17

4.6

POWER MANAGEMENT......................................18

4.6.1

POWER MANAGEMENT USING MIO ............18

5 LOCAL BUS ...........................................19

5.1

OVERVIEW............................................................19

5.2

OPERATION..........................................................19

5.3

CONFIGURATION & PROGRAMMING ..............20

6 BI-DIRECTIONAL PARALLEL PORT......21

6.1

OPERATION AND MODE SELECTION..............21

6.1.1

SPP MODE........................................................21

6.1.2

PS2 MODE ........................................................21

6.1.3

EPP MODE........................................................21

6.1.4

ECP MODE........................................................21

6.2

PARALLEL PORT INTERRUPT ..........................21

6.3

REGISTER DESCRIPTION.................................. 22

6.3.1

PARALLEL PORT DATA REGISTER `PDR'... 22

6.3.2

ECP FIFO ADDRESS / RLE............................ 22

6.3.3

DEVICE STATUS REGISTER `DSR' .............. 22

6.3.4

DEVICE CONTROL REGISTER `DCR'........... 23

6.3.5

EPP ADDRESS REGISTER `EPPA' ............... 23

6.3.6

EPP DATA REGISTERS `EPPD1-4' ............... 23

6.3.7

ECP DATA FIFO............................................... 23

6.3.8

TEST FIFO........................................................ 23

6.3.9

CONFIGURATION A REGISTER.................... 23

6.3.10

CONFIGURATION B REGISTER.................... 24

6.3.11

EXTENDED CONTROL REGISTER `ECR' .... 24

7 SERIAL EEPROM ...................................25

7.1

SPECIFICATION................................................... 25

7.2

EEPROM DATA ORGANISATION...................... 25

7.2.1

ZONE0: HEADER............................................. 25

7.2.2

ZONE1: LOCAL CONFIGURATION

REGISTERS........................................................................ 27

7.2.3

ZONE2: IDENTIFICATION REGISTERS........ 28

7.2.4

ZONE3: PCI CONFIGURATION REGISTERS28

7.2.5

ZONE4: FUNCTION ACCESS......................... 28

8 OPERATING CONDITIONS.....................30

9 DC ELECTRICAL CHARACTERISTICS ..30

9.1

NON-PCI I/O BUFFERS....................................... 30

9.2

PCI I/O BUFFERS................................................. 31

10 AC ELECTRICAL CHARACTERISTICS

32

10.1

PCI BUS ................................................................ 32

10.2

LOCAL BUS.......................................................... 32

11 TIMING WAVEFORMS ........................34

12 ERRATA 1 IMMEDIATE POWER

DOWN FILTERING.........................................39

Data Sheet Revision 1.1 PRELIMINARY Page 4

OX9162

OXFORD SEMICONDUCTOR LTD.

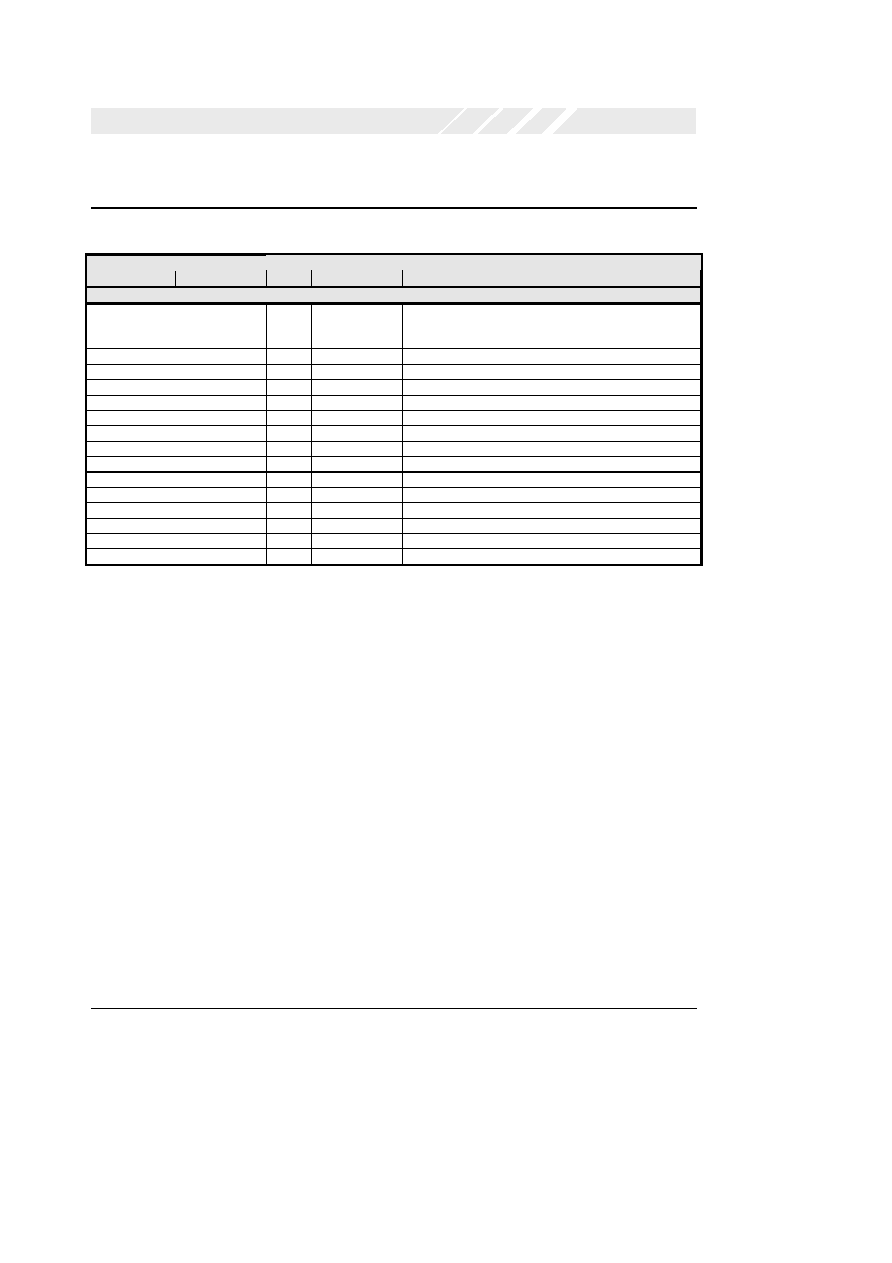

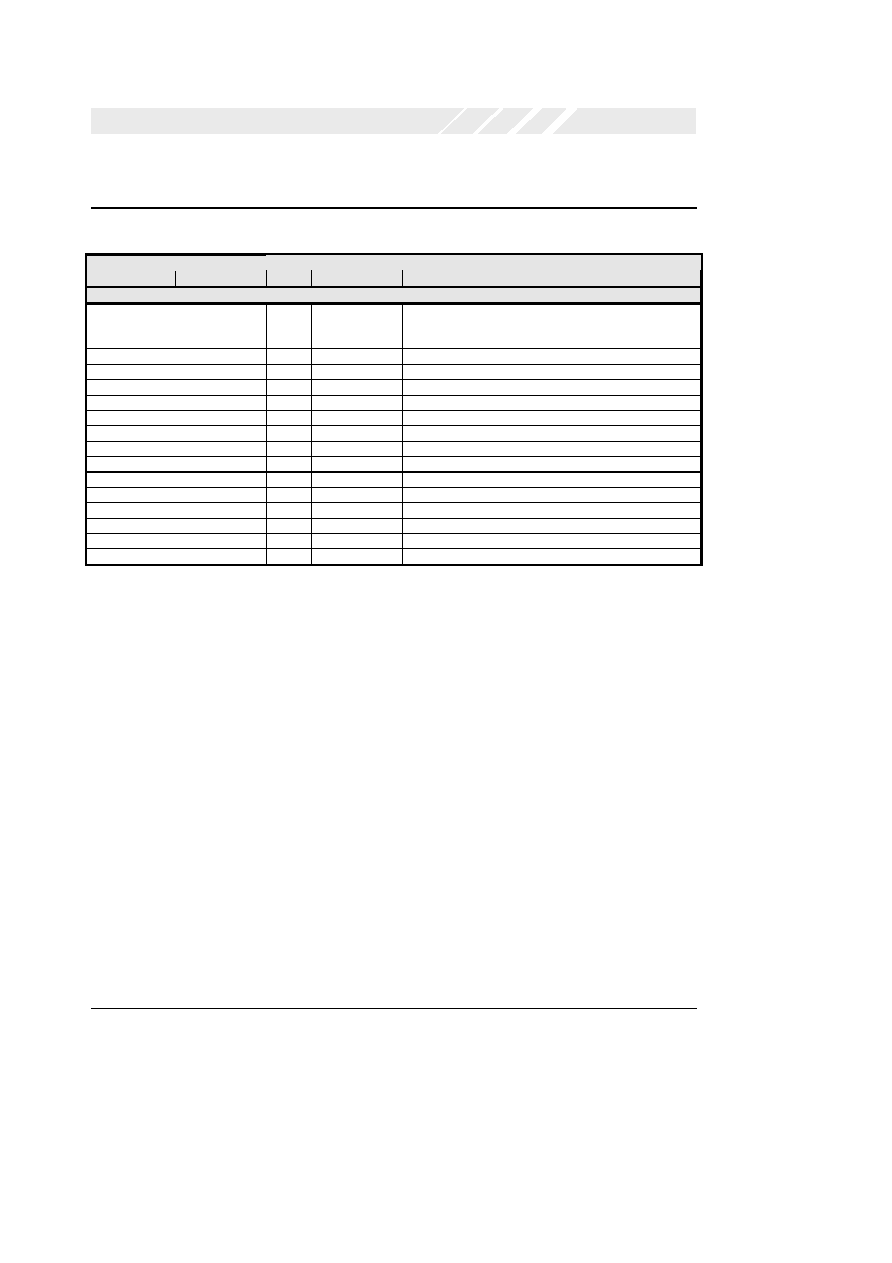

2 P

IN

D

ESCRIPTIONS

Mode

Parallel

Local Bus

Dir

1

Name

Description

PCI interface

115,117,118,120,121,122,125,126,

3,5,6,7,10,11,12,13,27,28,29,34,35

,38,39,41,45,46,49,50,55,56,58,59

P_I/O AD[31:0]

Multiplexed PCI Address/Data bus

127, 14, 26 ,42

P_I

C/BE[3:0]#

PCI Command/Byte enable

112

P_I

CLK

PCI system clock

15

P_I

FRAME#

Cycle Frame

20

P_O

DEVSEL#

Device Select

18

P_I

IRDY#

Initiator ready

19

P_O

TRDY#

Target ready

22

P_O

STOP#

Target Stop request

25

P_I/O PAR

Parity

24

P_O

SERR#

System error

23

P_I/O PERR#

Parity error

2

P_I

IDSEL

Initialisation device select

110

P_I

RST#

PCI system reset

109

P_OD INTA#

PCI interrupt

114

P_OD PME#

Power management event

Data Sheet Revision 1.1 PRELIMINARY Page 5

OX9162

OXFORD SEMICONDUCTOR LTD.

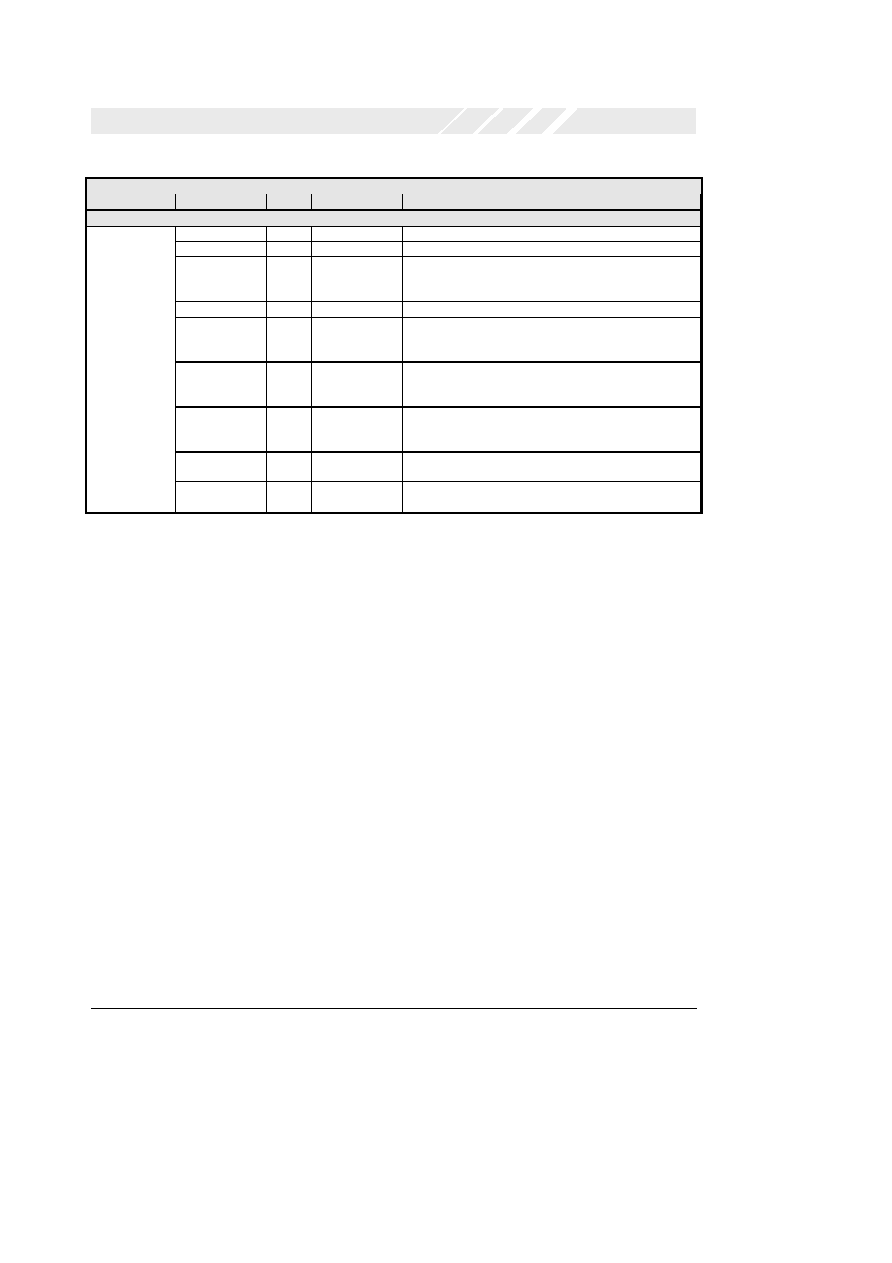

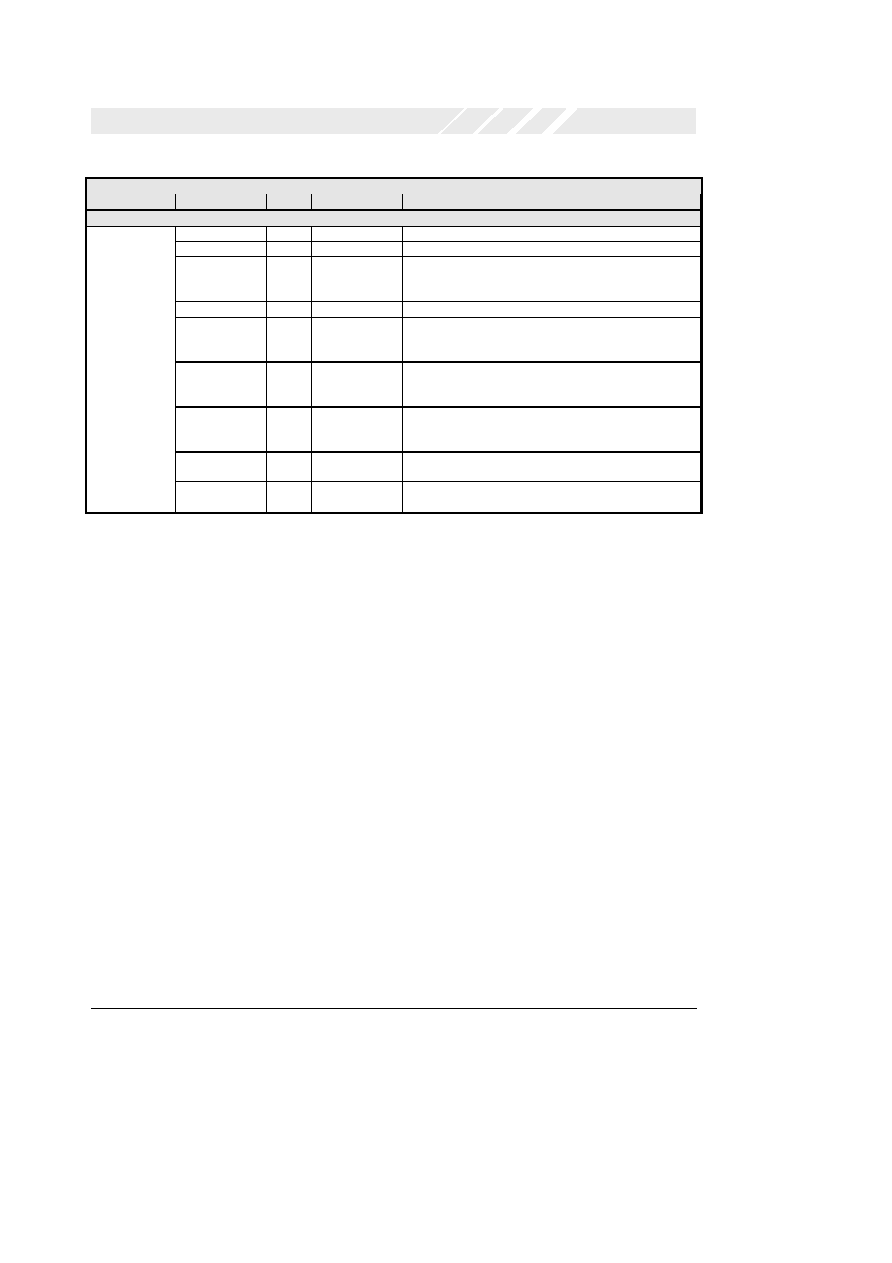

Mode

Parallel

Local Bus

Dir

1

Name

Description

Local Bus

62

O

LBRST

Local bus active-high reset

61

O

LBRST#

Local bus active-low reset

83

O

LBDOUT

Local bus data out enable. This pin can be used by external

transceivers; it is high when LBD[7:0] are in output mode and

low when they are in input mode.

101

O

LBCLK

Buffered PCI clock. Can be enabled / disabled by software

99, 91

O

O

LBCS[1:0]#

LBDS[1:0]#

Local bus active-low Chip-Select (Intel mode)

Local bus active-low Data-Strobe (Motorola mode)

63

O

O

LBWR#

LBRDWR#

Local Bus active-low write-strobe (Intel mode)

Local Bus Read-not-Write control (Motorola mode)

85

O

O

LBRD#

Hi

Local Bus active-low read-strobe (Intel mode)

Permanent high (Motorola mode)

77,78,79,82,

87,88,89,90

O

LBA[7:0]

Local bus address signals

N/A

66,67,68,71,

72,73,74,76

I/O

LBD[7:0]

Local bus data signals