SM8230A

NIPPON PRECISION CIRCUITS--1

NIPPON PRECISION CIRCUITS INC.

OVERVIEW

The SM8230A is a dual-tone signal generator LSI

developed for DTMF (dual tone multi-frequency)

dialing. It features a built-in piezo-electric speaker

driver for direct connection to a piezo-electric

buzzer.

The DTMF frequencies can be set to correspond to

the DTMF standards of any country. The output level

is also adjustable under software control. These

features, combined with its small package and low

power dissipation, make the SM8230A a very use

device to use.

FEATURES

s

3-line serial interface to external CPU

s

2 independent, adjustable frequency outputs

s

Piezo driver for direct connection to a piezo-

electric buzzer

s

4 system clock frequencies selectable (480 kHz,

960 kHz, 1.92 MHz, 3.84 MHz)

s

2.6 to 3.3 V supply voltage

s

Low current consumption

� 3.0 mA (max) operating current

� 1 �A (max) standby current

s

8-pin plastic SOP

PINOUT

PACKAGE DIMENSIONS

VDD

5

4

8

1

BZH

BZL

CLK

SD

SCL

OE

VSS

8230

AS

4.4 0.2

6.2 0.3

0.4 0.1

1.27

0.05 0.05

1.5 0.1

0.4 0.2

0 10

5.2 0.3

0.15

+

0.10

-

0.05

Tone Dialer with Built-in Piezo Driver

S M 8 2 3 0 A

NIPPON PRECISION CIRCUITS--2

BLOCK DIAGRAM

PIN DESCRIPTION

N u m b e r

N a m e

I/O

Description

1

SD

I

Serial data input

2

SCL

I

Serial data transfer clock input.

(For valid transfer, OE must stay LOW for 16 clock cycles.)

3

OE

I

DTMF output enable/serial data transfer select input.

Serial data transfer is selected when LOW.

4

VSS

�

Ground

5

CLK

I

System clock input. The clock can be set to one of four frequencies (480 kHz, 960

kHz, 1.92 MHz, 3.84 MHz).

6

BZL

O

DTMF low-frequency group analog output

7

BZH

O

DTMF high-frequency group analog output

8

VDD

�

Supply voltage

CLK

OE

BZL

VSS

SCL

VDD

SD

BZH

LATCH

SELECTOR

Programmable

Counter

High Group

ROM

D/A

Converter

Output

Control

Programmable

Counter

Low Group

ROM

D/A

Converter

Output

Control

S M 8 2 3 0 A

NIPPON PRECISION CIRCUITS--3

SPECIFICATIONS

Absolute Maximum Ratings

V

SS

= 0 V

Recommended Operating Conditions

V

SS

= 0 V

DC Characteristics

V

DD

= 2.6 to 3.3V, V

SS

= 0 V, T

a

=

-

20 to 70

�

C

P arameter

S y m b o l

Rating

Unit

Supply voltage range

V

DD

-

0.3 to 7.0

V

Input voltage range

V

IN

V

SS

-

0.3 to V

DD

+ 0.3

V

Output voltage range

V

OUT

V

SS

-

0.3 to V

DD

+ 0.3

V

Storage temperature range

T

stg

-

55 to 125

�

C

Power dissipation

P

D

250

mW

Soldering temperature

T

sld

255

�

C

Soldering time

t

sld

10

s

P arameter

S y m b o l

Condition

Rating

Unit

m i n

typ

m a x

Supply voltage range

V

DD

2.6

3.0

3.3

V

Operating temperature

T

opr

-

20

25

70

�

C

P arameter

S y m b o l

Condition

Rating

Unit

m i n

typ

m a x

Operating current consumption

I

DD

V

DD

= 3.0 V, T

a

= 25

�

C,

f

CLK

= 480 kHz

�

1.5

3

mA

Standby current consumption

I

ST

V

DD

= 3.3 V, OE = LOW

�

�

1

�A

Input voltage (all inputs)

V

IH

HIGH-level input

1.1

�

V

DD

V

V

IL

LOW-level input

V

SS

�

0.6

Input leakage current

I

IL

HIGH/LOW-level input

-

1

�

1

�A

BZH/BZL tone output voltage

V

BZO

0 dB output level

0.86V

DD

0.93V

DD

1.0V

DD

Vp-p

BZH/BZL tone output adjustment

step

D

RES

�

1.0

�

dB

BZH/BZL tone output absolute error

D

LIN

V

ZBO

levels

-

1

�

1

dB

BZH/BZL tone output impedance

Z

OUT

100

150

200

S M 8 2 3 0 A

NIPPON PRECISION CIRCUITS--4

AC Characteristics

V

DD

= 2.6 to 3.3V, V

SS

= 0 V, T

a

=

-

20 to 70

�

C

System clock input timing

Serial data transfer timing

P arameter

S y m b o l

Condition

Rating

Unit

m i n

typ

m a x

Tone output frequency error

f

f

CLK

= 3.84 MHz,

no deviation

�

�

0.37

%

Tone distortion

1

1. T

a

= -10 to 70

�

C, THD + N (10 Hz to 500 kHz), no load

DIS

BZH/BZL

�

5

10

%

CLK cycle time

t

CLK

CLK input waveform

250

�

�

ns

CLK LOW-level pulsewidth

t

CLKL

100

�

�

ns

CLK HIGH-level pulsewidth

t

CLKH

100

�

�

ns

OE setup time

t

SUOE

Between OE and SCL

100

�

�

ns

OE hold time

t

HDOE

100

�

�

ns

SCL cycle time

t

SCL

SCL input waveform

1

�

�

�s

SCL LOW-level pulsewidth

t

SCLL

400

�

�

ns

SCL HIGH-level pulsewidth

t

SCLH

400

�

�

ns

Input data setup time

t

SUD

Between SD and SCL

100

�

�

ns

Input data hold time

t

HDD

100

�

�

ns

CLK

t

CLKL

t

CLKH

t

CLK

D A T A ( b 0 )

OE

SCL

SD

t

HDOE

t

SCLL

t

SCLH

t

SUD

t

HDD

t

SCL

t

SUOE

D A T A ( b 1 5 )

D A T A ( b 1 4 )

1

2

16

S M 8 2 3 0 A

NIPPON PRECISION CIRCUITS--5

FUNCTIONAL DESCRIPTION

Serial Interface

Data is transferred in 16-bit units by writing com-

mands over a 3-line serial interface comprising OE

(output enable), SCL (serial clock) and SD (serial

data input). Note that data transfer is unidirectional;

no data is output from the SM8230A. The operating

sequence is described below.

Command transfer

Data can be transferred when OE goes LOW. Data is

transferred in 16-bit units in sync with the rising

edge of the SCL clock.

Note that when OE is LOW and both SD and SCL

are tied LOW, the current consumption is less than 1

�A (standby mode).

The internal states are undefined when power is first

applied.

DTMF analog signal output

Data transfer stops and DTMF analog signal output

starts when OE goes HIGH, as shown in figure 2.

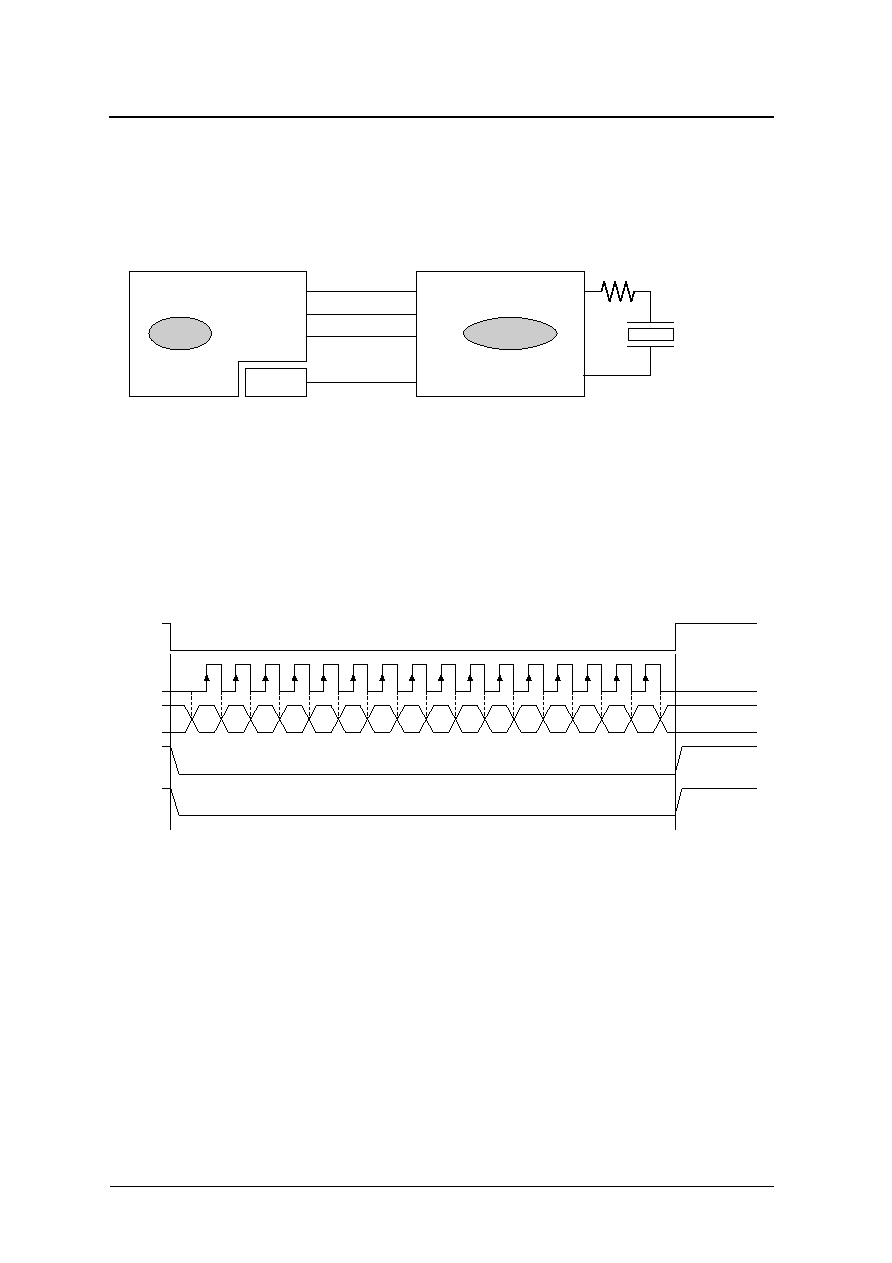

Figure 1. Serial interface connection example

(Clock)

Port

Serial Clock

Serial Data

CPU

CLK

OE

SCL

SD

BZH

BZL

R

Piezo Buzzer

SM8230

Figure 2. Serial data transfer timing

SCL

SD

BZL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

MSB

LSB

BZH

OE

0

0

CK1 CK0 FH1 FH0 GH3 GH2 GH1 GH0 FL1 FL0 GL3 GL2 GL1 GL0

Piezo buzzer

output

Serial data transmission

Low frequency

group output

High frequency

group output

b15 b14 b13 b12 b11 b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

S M 8 2 3 0 A

NIPPON PRECISION CIRCUITS--6

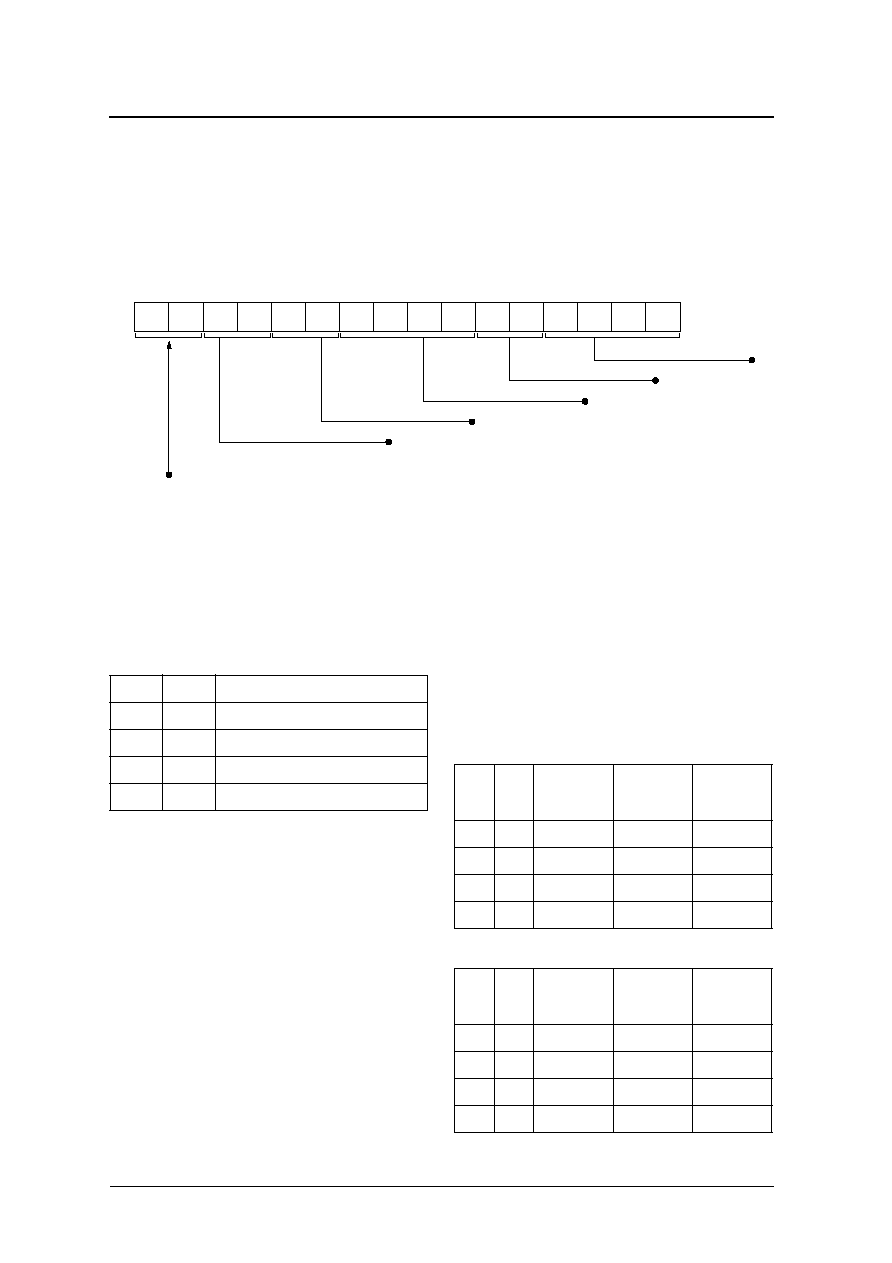

Transfer Command Specifications

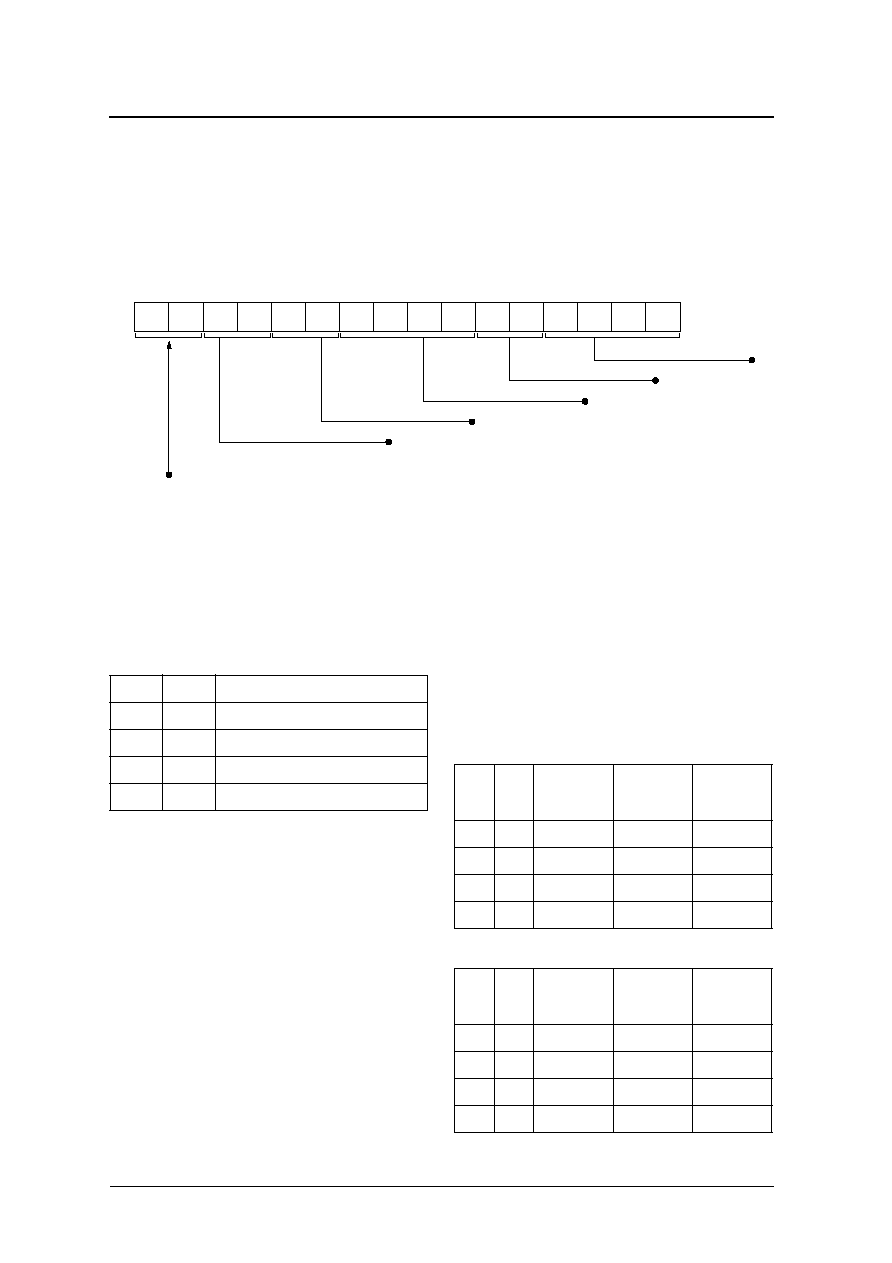

The transfer data code format is shown in figure 3.

Data is transferred with the MSB as the leading bit.

The data sets the input clock, high-frequency group

and low-frequency group frequencies, and the output

levels. The commands are shown in tables 1 to 4.

CK command (CK1, CK0)

These bits set the frequency of the input clock on

CLK. The frequency can be set to 1

�

, 2

�

, 4

�

, and 8

�

multiples of 480 kHz. The input code and the corre-

sponding clock frequency are shown in table 1.

Figure 3. Transfer command format

Table 1. CK command

C K 1

C K 0

CLK input clock frequency

0

0

480 kHz

0

1

960 kHz

1

0

1.92 MHz

1

1

3.84 MHz

0

0

CK1 CK0 FH1 FH0 GH3 GH2 GH1 GH0 FL1 FL0 GL3 GL2 GL1 GL0

Low group output level set.

Low group frequency set.

High group output level set.

High group frequency set.

CLK pin input frequency set.

b15(MSB)

b0(LSB)

Set (b14, b15) = (0, 0)

for normal operation.

FH/FL command (HF1, FH0 / FL1, FL0)

These bits set the DTMF signal high-frequency and

low-frequency group frequencies, respectively.

The input code, the corresponding group frequency

specification, the design value and frequency devia-

tion are shown in tables 2 and 3.

Note that the design value and frequency deviation

are calculated values assuming a deviation-free sys-

tem clock input on CLK.

Table 2. FH command

F H 1

F H 0

D T M F

frequency

(Hz)

Design

value (Hz)

D e viation

(%)

0

0

1209

1212.1

+0.26

0

1

1336

1333.3

-

0.20

1

0

1477

1481.5

+0.30

1

1

1633

1632.7

-

0.02

Table 3. FL command

F H 1

F H 0

D T M F

frequency

(Hz)

Design

value (Hz)

D e viation

(%)

0

0

697

697.7

+0.10

0

1

770

769.2

-

0.10

1

0

852

851.1

-

0.11

1

1

941

937.5

-

0.37

S M 8 2 3 0 A

NIPPON PRECISION CIRCUITS--7

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to

improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for

the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits

are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision

Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or

malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter,

including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or

indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

NIPPON PRECISION CIRCUITS INC.

4-3, 2-chome Fukuzumi

Koutou-ku, Tokyo 135-8430, Japan

Telephone: 03-3642-6661

Facsimile: 03-3642-6698

NC9614BE

1997.01

NIPPON PRECISION CIRCUITS INC.

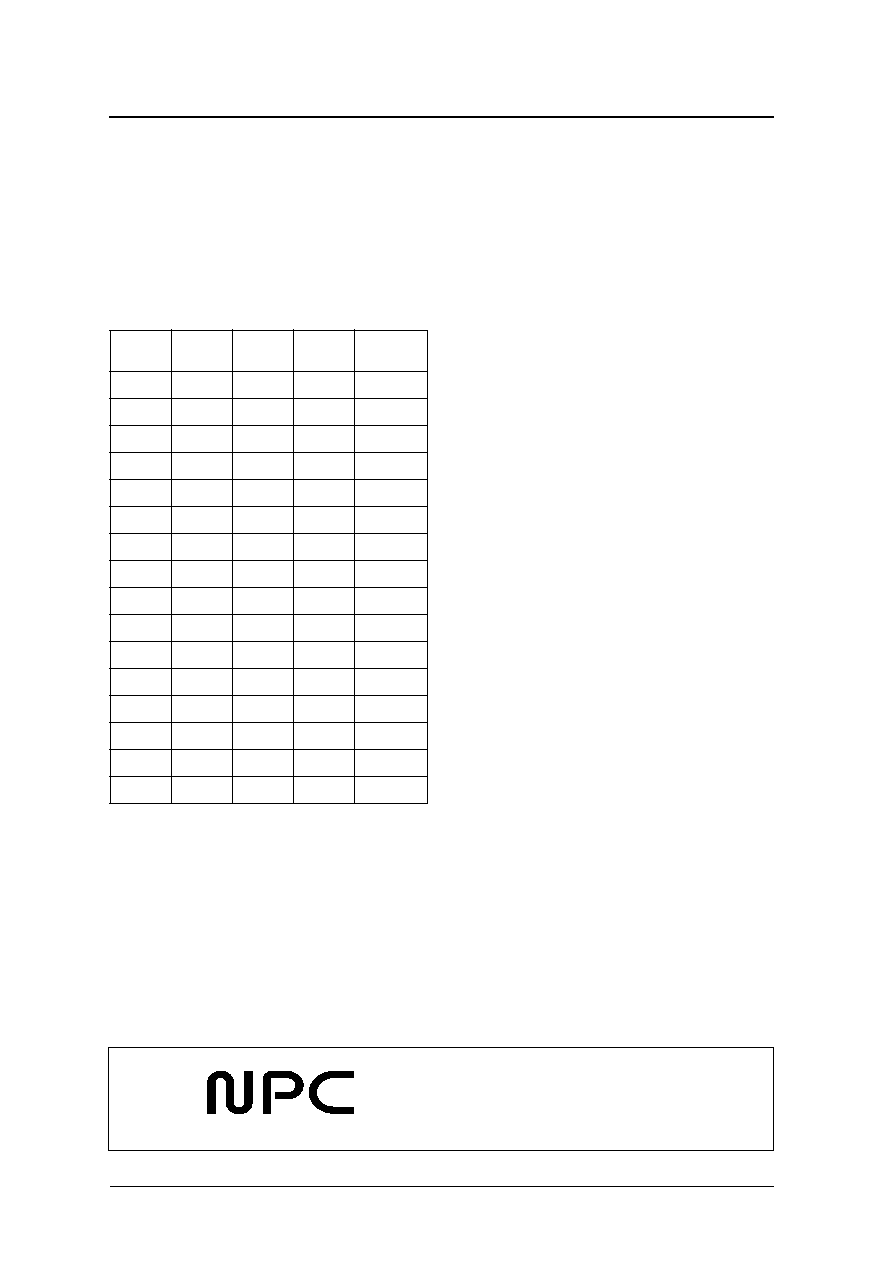

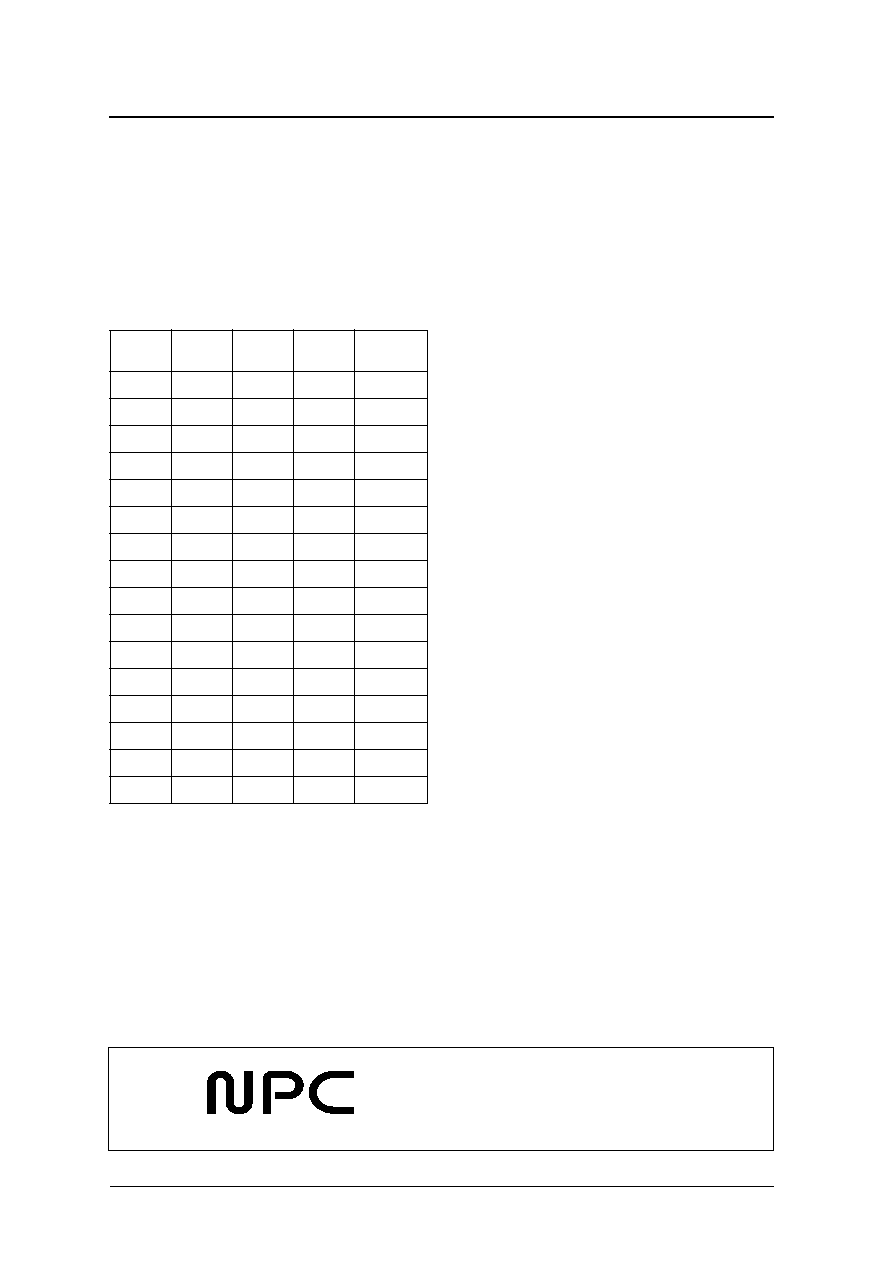

GH/GL command (GH3 to GH0, GL3 to GL0)

These bits set the output levels of the high-frequency

group and low-frequency group outputs, respec-

tively. The input code and the corresponding output

level are shown in table 4. Note that the 0 dB point is

typically 93% of the supply voltage. Any value

above 0 dB results in amplitude clipping of the out-

put waveform.

Table 4. GH/GL command

G H 3 / G L

3

G H 2 / G L

2

G H 1 / G L

1

G H 0 / G L

0

Output

level

0

0

0

0

-

9 dB

0

0

0

1

-

8 dB

0

0

1

0

-

7 dB

0

0

1

1

-

6 dB

0

1

0

0

-

5 dB

0

1

0

1

-

4 dB

0

1

1

0

-

3 dB

0

1

1

1

-

2 dB

1

0

0

0

-

1 dB

1

0

0

1

0 dB

1

0

1

0

1 dB

1

0

1

1

2 dB

1

1

0

0

3 dB

1

1

0

1

4 dB

1

1

1

0

5 dB

1

1

1

1

6 dB