1

Motorola TMOS Power MOSFET Transistor Device Data

Designer's

TM

Data Sheet

Medium Power Surface Mount Products

TMOS Single P-Channel

Field Effect Transistors

MiniMOS

TM

devices are an advanced series of power MOSFETs

which utilize Motorola's High Cell Density HDTMOS process.

These miniature surface mount MOSFETs feature ultra low RDS(on)

and true logic level performance. They are capable of withstanding

high energy in the avalanche and commutation modes and the

drainştoşsource diode has a very low reverse recovery time.

MiniMOS devices are designed for use in low voltage, high speed

switching applications where power efficiency is important. Typical

applications are dcşdc converters, and power management in

portable and battery powered products such as computers,

printers, cellular and cordless phones. They can also be used for

low voltage motor controls in mass storage products such as disk

drives and tape drives. The avalanche energy is specified to

eliminate the guesswork in designs where inductive loads are

switched and offer additional safety margin against unexpected

voltage transients.

Ě

Ultra Low RDS(on) Provides Higher Efficiency and Extends Battery Life

Ě

Logic Level Gate Drive -- Can Be Driven by Logic ICs

Ě

Miniature SOş8 Surface Mount Package -- Saves Board Space

Ě

Diode Is Characterized for Use In Bridge Circuits

Ě

Diode Exhibits High Speed, With Soft Recovery

Ě

IDSS Specified at Elevated Temperature

Ě

Avalanche Energy Specified

Ě

Mounting Information for SOş8 Package Provided

MAXIMUM RATINGS

(TJ = 25

░

C unless otherwise noted)(1)

Rating

Symbol

Value

Unit

DrainştoşSource Voltage

VDSS

20

Vdc

DrainştoşGate Voltage (RGS = 1.0 M

)

VDGR

20

Vdc

GateştoşSource Voltage -- Continuous

VGS

▒

20

Vdc

Drain Current -- Continuous @ TA = 25

░

C

Drain Current

-- Continuous @ TA = 100

░

C

Drain Current

-- Single Pulse (tp

10

Á

s)

ID

ID

IDM

5.6

3.6

30

Adc

Apk

Total Power Dissipation @ TA = 25

░

C (2)

PD

2.5

Watts

Operating and Storage Temperature Range

TJ, Tstg

ş 55 to 150

░

C

Single Pulse DrainştoşSource Avalanche Energy -- Starting TJ = 25

░

C

(VDD = 20 Vdc, VGS = 5.0 Vdc, Peak IL = 9.0 Apk, L = 14

mH, RG = 25

)

EAS

567

mJ

Thermal Resistance -- Junction to Ambient (2)

R

JA

50

░

C/W

Maximum Lead Temperature for Soldering Purposes, 1/8

from case for 10 seconds

TL

260

░

C

DEVICE MARKING

S3P02

(1) Negative sign for PşChannel device omitted for clarity.

(2) Mounted on 2" square FR4 board (1" sq. 2 oz. Cu 0.06" thick single sided), 10 sec. max.

ORDERING INFORMATION

Device

Reel Size

Tape Width

Quantity

MMSF3P02HDR2

13

12 mm embossed tape

2500 units

Designer's Data for "Worst Case" Conditions -- The Designer's Data Sheet permits the design of most circuits entirely from the information presented. SOA Limit

curves -- representing boundaries on device characteristics -- are given to facilitate "worst case" design.

Designer's, HDTMOS and MiniMOS are trademarks of Motorola, Inc. TMOS is a registered trademark of Motorola, Inc.

Thermal Clad is a trademark of the Bergquist Company.

Order this document

by MMSF3P02HD/D

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

ę

Motorola, Inc. 1996

CASE 751ş05, Style 13

SOş8

NşC

1

2

3

4

8

7

6

5

Top View

Source

Source

Gate

Drain

Drain

Drain

Drain

D

S

G

MMSF3P02HD

SINGLE TMOS

POWER MOSFET

3.0 AMPERES

20 VOLTS

RDS(on) = 0.075 OHM

Motorola Preferred Device

TM

Preferred devices are Motorola recommended choices for future use and best overall value.

REV 5

MMSF3P02HD

2

Motorola TMOS Power MOSFET Transistor Device Data

ELECTRICAL CHARACTERISTICS

(TA = 25

░

C unless otherwise noted)(1)

Characteristic

Symbol

Min

Typ

Max

Unit

OFF CHARACTERISTICS

DrainştoşSource Breakdown Voltage

(VGS = 0 Vdc, ID = 250

Á

Adc)

Temperature Coefficient (Positive)

V(BR)DSS

20

--

--

24

--

--

Vdc

mV/

░

C

Zero Gate Voltage Drain Current

(VDS = 20 Vdc, VGS = 0 Vdc)

(VDS = 20 Vdc, VGS = 0 Vdc, TJ = 125

░

C)

IDSS

--

--

--

--

1.0

10

Á

Adc

GateşBody Leakage Current (VGS =

▒

20 Vdc, VDS = 0)

IGSS

--

--

100

nAdc

ON CHARACTERISTICS(2)

Gate Threshold Voltage

(VDS = VGS, ID = 250

Á

Adc)

Temperature Coefficient (Negative)

VGS(th)

1.0

--

1.5

4.0

2.0

--

Vdc

mV/

░

C

Static DrainşSource OnşResistance

(VGS = 10 Vdc, ID = 3.0 Adc)

(VGS = 4.5 Vdc, ID = 1.5 Adc)

RDS(on)

--

--

0.06

0.08

0.075

0.095

Ohm

Forward Transconductance (VDS = 3.0 Vdc, ID = 1.5 Adc)

gFS

3.0

7.2

--

mhos

DYNAMIC CHARACTERISTICS

Input Capacitance

(VDS = 16 Vdc, VGS = 0 Vdc,

f = 1.0 MHz)

Ciss

--

1010

1400

pF

Output Capacitance

(VDS = 16 Vdc, VGS = 0 Vdc,

f = 1.0 MHz)

Coss

--

740

920

Transfer Capacitance

f = 1.0 MHz)

Crss

--

260

490

SWITCHING CHARACTERISTICS(3)

TurnşOn Delay Time

(VDD = 10 Vdc, ID = 3.0 Adc,

VGS = 4.5 Vdc,

RG = 6.0

)

td(on)

--

25

50

ns

Rise Time

(VDD = 10 Vdc, ID = 3.0 Adc,

VGS = 4.5 Vdc,

RG = 6.0

)

tr

--

135

270

TurnşOff Delay Time

VGS = 4.5 Vdc,

RG = 6.0

)

td(off)

--

54

108

Fall Time

G = 6.0

)

tf

--

84

168

TurnşOn Delay Time

(VDD = 10 Vdc, ID = 3.0 Adc,

VGS = 10 Vdc,

RG = 6.0

)

td(on)

--

16

32

Rise Time

(VDD = 10 Vdc, ID = 3.0 Adc,

VGS = 10 Vdc,

RG = 6.0

)

tr

--

40

80

TurnşOff Delay Time

VGS = 10 Vdc,

RG = 6.0

)

td(off)

--

110

220

Fall Time

G = 6.0

)

tf

--

97

194

Gate Charge

See Figure 8

(VDS = 16 Vdc, ID = 3.0 Adc,

VGS = 10 Vdc)

QT

--

33

46

nC

See Figure 8

(VDS = 16 Vdc, ID = 3.0 Adc,

VGS = 10 Vdc)

Q1

--

3.0

--

(VDS = 16 Vdc, ID = 3.0 Adc,

VGS = 10 Vdc)

Q2

--

11

--

Q3

--

10

--

SOURCEşDRAIN DIODE CHARACTERISTICS

Forward OnşVoltage(2)

(IS = 3.0 Adc, VGS = 0 Vdc)

(IS = 3.0 Adc, VGS = 0 Vdc, TJ = 125

░

C)

VSD

--

--

1.35

0.96

1.75

--

Vdc

Reverse Recovery Time

See Figure 15

(IS = 3.0 Adc, VGS = 0 Vdc,

dIS/dt = 100 A/

Á

s)

trr

--

76

--

ns

See Figure 15

(IS = 3.0 Adc, VGS = 0 Vdc,

dIS/dt = 100 A/

Á

s)

ta

--

32

--

(IS = 3.0 Adc, VGS = 0 Vdc,

dIS/dt = 100 A/

Á

s)

tb

--

44

--

Reverse Recovery Stored Charge

QRR

--

0.133

--

Á

C

(1) Negative sign for PşChannel device omitted for clarity.

(2) Pulse Test: Pulse Width

300

Á

s, Duty Cycle

2%.

(3) Switching characteristics are independent of operating junction temperature.

MMSF3P02HD

3

Motorola TMOS Power MOSFET Transistor Device Data

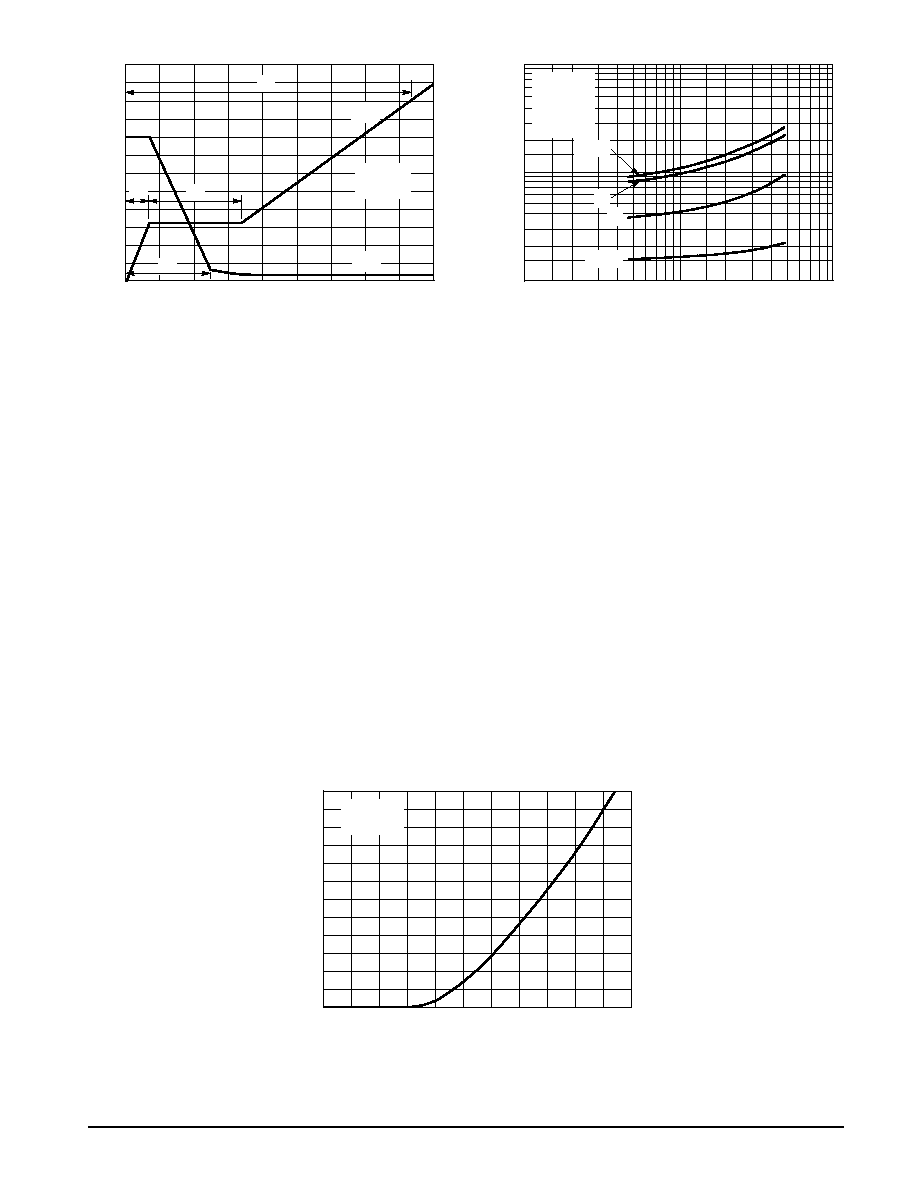

TYPICAL ELECTRICAL CHARACTERISTICS

R

DS(on)

, DRAINşT

OşSOURCE RESIST

ANCE

(NORMALIZED)

R

DS(on)

, DRAIN-T

O-SOURCE RESIST

ANCE (OHMS)

0

3

4

6

1

5

2

0

0.2

0.4

0.6

0.8

2

0

3

4

6

VDS, DRAINşTOşSOURCE VOLTAGE (VOLTS)

Figure 1. OnşRegion Characteristics

I D

, DRAIN CURRENT

(AMPS)

1.6

1.8

2

2.2

2.4

3.4

I D

, DRAIN CURRENT

(AMPS)

VGS, GATEşTOşSOURCE VOLTAGE (VOLTS)

Figure 2. Transfer Characteristics

0

1

2

3

4

10

0.4

0.6

R

DS(on)

, DRAIN-T

O-SOURCE RESIST

ANCE (OHMS)

0

1

2

3

4

6

0.05

0.07

VGS, GATEşTOşSOURCE VOLTAGE (VOLTS)

Figure 3. OnşResistance versus

GateşToşSource Voltage

ID, DRAIN CURRENT (AMPS)

Figure 4. OnşResistance versus Drain Current

and Gate Voltage

0.80

1.20

10

100

1000

TJ, JUNCTION TEMPERATURE (

░

C)

Figure 5. OnşResistance Variation with

Temperature

VDS, DRAINşTOşSOURCE VOLTAGE (VOLTS)

Figure 6. DrainşToşSource Leakage

Current versus Voltage

I DSS

, LEAKAGE (nA)

TJ = 25

░

C

VDS

10 V

TJ = 100

░

C

25

░

C

ş 55

░

C

VGS = 0 V

ID = 1.5 A

TJ = 25

░

C

VGS = 4.5 V

VGS = 10 V

ID = 3.0 A

1

1.2

3.7 V

3.1 V

2.5 V

2.6

1

1.4

1.6

1.8

2.8

3

3.2

0.2

5

6

7

8

9

10 V

ş 50

0

25

50

75

100

125

150

TJ = 125

░

C

5

0.09

0.06

0.90

2

0

5

1.00

1.10

0

4

8

12

16

20

0.08

2.7 V

2.9 V

VGS = 10 V

3.3 V

3.5 V

3.9 V

4.5 V

TJ = 25

░

C

MMSF3P02HD

4

Motorola TMOS Power MOSFET Transistor Device Data

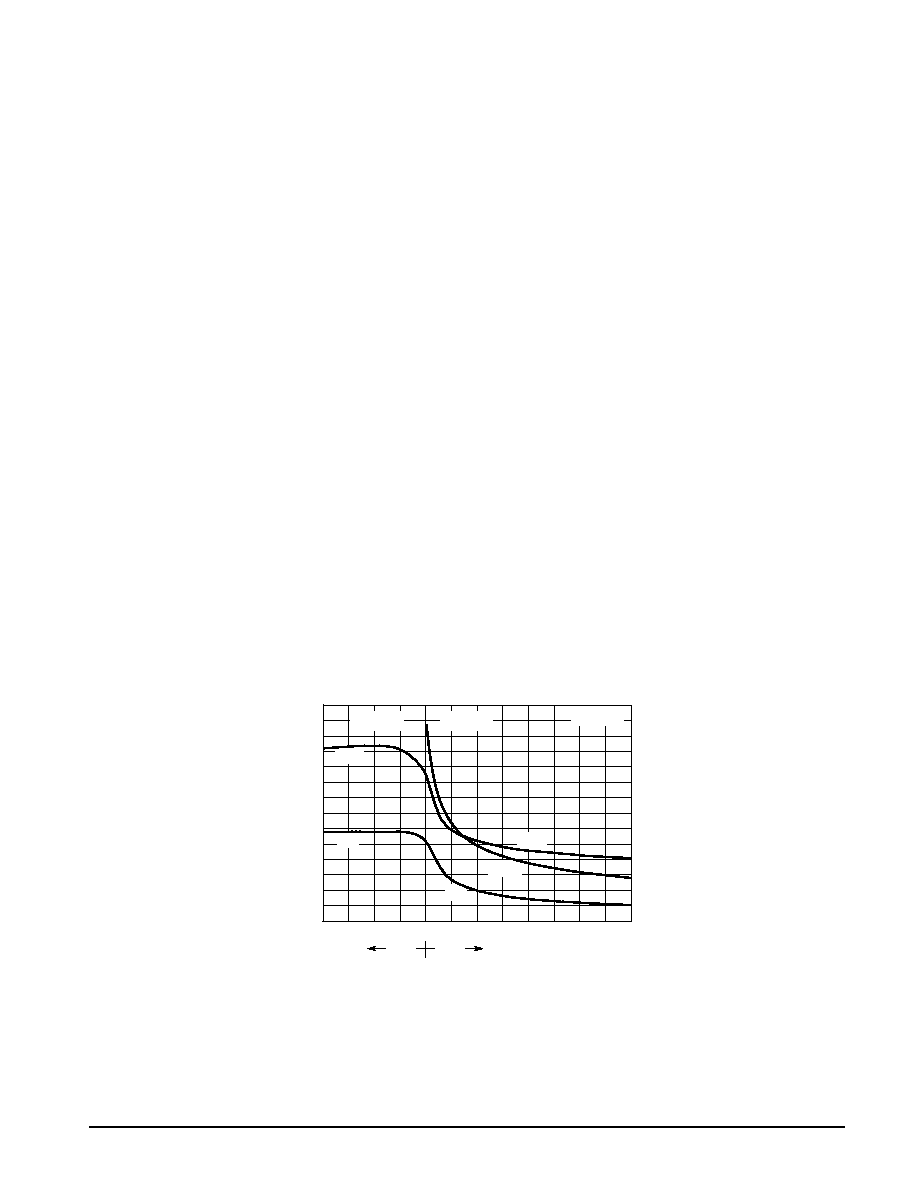

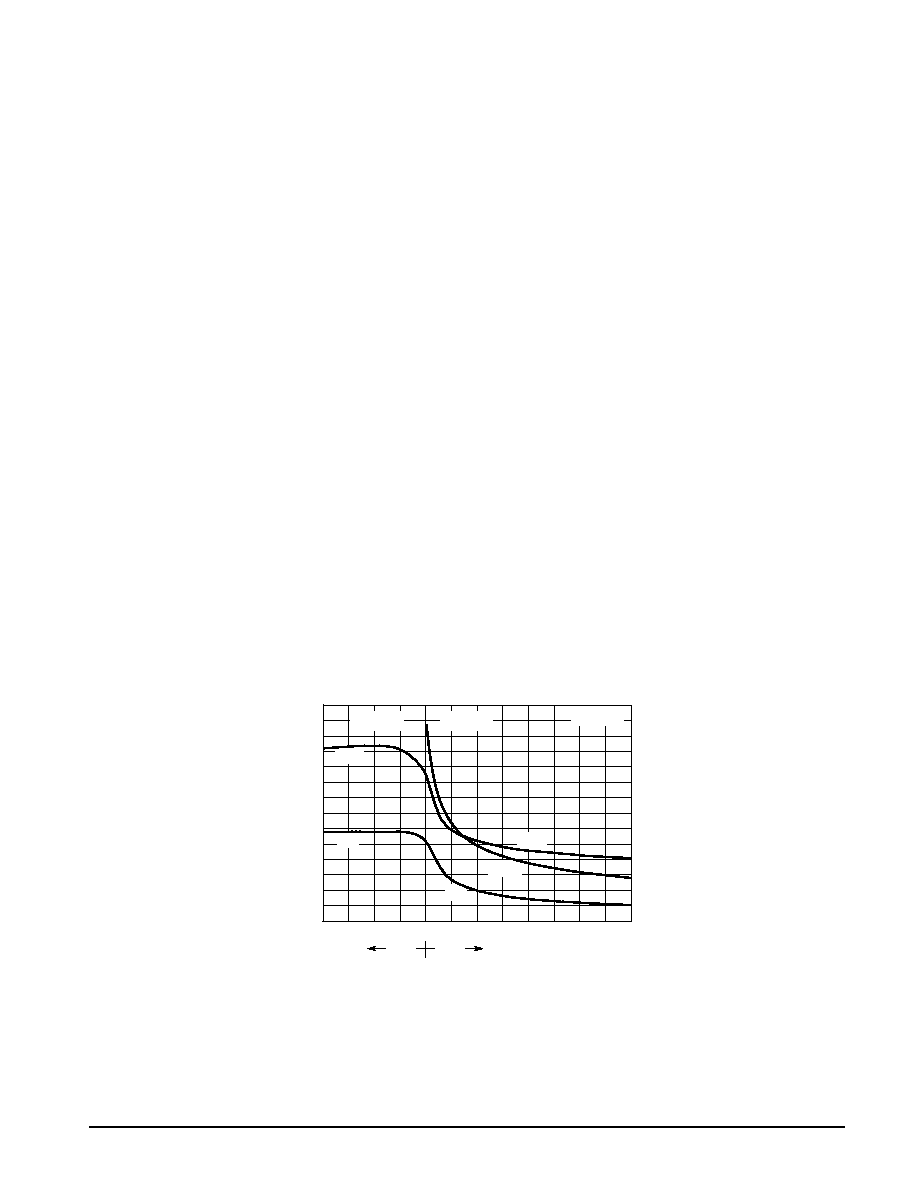

POWER MOSFET SWITCHING

Switching behavior is most easily modeled and predicted

by recognizing that the power MOSFET is charge controlled.

The lengths of various switching intervals (

t) are deter-

mined by how fast the FET input capacitance can be charged

by current from the generator.

The published capacitance data is difficult to use for calculat-

ing rise and fall because drainşgate capacitance varies

greatly with applied voltage. Accordingly, gate charge data is

used. In most cases, a satisfactory estimate of average input

current (IG(AV)) can be made from a rudimentary analysis of

the drive circuit so that

t = Q/IG(AV)

During the rise and fall time interval when switching a resis-

tive load, VGS remains virtually constant at a level known as

the plateau voltage, VSGP. Therefore, rise and fall times may

be approximated by the following:

tr = Q2 x RG/(VGG ş VGSP)

tf = Q2 x RG/VGSP

where

VGG = the gate drive voltage, which varies from zero to VGG

RG = the gate drive resistance

and Q2 and VGSP are read from the gate charge curve.

During the turnşon and turnşoff delay times, gate current is

not constant. The simplest calculation uses appropriate val-

ues from the capacitance curves in a standard equation for

voltage change in an RC network. The equations are:

td(on) = RG Ciss In [VGG/(VGG ş VGSP)]

td(off) = RG Ciss In (VGG/VGSP)

The capacitance (Ciss) is read from the capacitance curve at

a voltage corresponding to the offşstate condition when cal-

culating td(on) and is read at a voltage corresponding to the

onşstate when calculating td(off).

At high switching speeds, parasitic circuit elements com-

plicate the analysis. The inductance of the MOSFET source

lead, inside the package and in the circuit wiring which is

common to both the drain and gate current paths, produces a

voltage at the source which reduces the gate drive current.

The voltage is determined by Ldi/dt, but since di/dt is a func-

tion of drain current, the mathematical solution is complex.

The MOSFET output capacitance also complicates the

mathematics. And finally, MOSFETs have finite internal gate

resistance which effectively adds to the resistance of the

driving source, but the internal resistance is difficult to mea-

sure and, consequently, is not specified.

The resistive switching time variation versus gate resis-

tance (Figure 9) shows how typical switching performance is

affected by the parasitic circuit elements. If the parasitics

were not present, the slope of the curves would maintain a

value of unity regardless of the switching speed. The circuit

used to obtain the data is constructed to minimize common

inductance in the drain and gate circuit loops and is believed

readily achievable with board mounted components. Most

power electronic loads are inductive; the data in the figure is

taken with a resistive load, which approximates an optimally

snubbed inductive load. Power MOSFETs may be safely op-

erated into an inductive load; however, snubbing reduces

switching losses.

GATEşTOşSOURCE OR DRAINşTOşSOURCE VOLTAGE (Volts)

C, CAP

ACIT

ANCE (pF)

1500

2000

2500

3500

Figure 7. Capacitance Variation

3000

10

0

10

15

20

VGS

VDS

5

5

TJ = 25

░

C

Ciss

Coss

Crss

1000

500

VDS = 0 V

VGS = 0 V

Ciss

Crss

0

MMSF3P02HD

5

Motorola TMOS Power MOSFET Transistor Device Data

Figure 8. GateşToşSource and DrainşToşSource

Voltage versus Total Charge

RG, GATE RESISTANCE (OHMS)

1

10

100

1000

100

10

t,

TIME (ns)

VDD = 10 V

ID = 3 A

VGS = 10 V

TJ = 25

░

C

tr

tf

td(off)

td(on)

Figure 9. Resistive Switching Time

Variation versus Gate Resistance

24

V

GS

, GA

TEşT

OşSOURCE VOL

T

AGE (VOL

TS)

20

16

12

8

4

0

0

10

6

2

0

QT, TOTAL CHARGE (nC)

V

DS

, DRAINşT

OşSOURCE VOL

T

AGE (VOL

TS)

12

8

4

4

8

36

ID = 3 A

TJ = 25

░

C

12

VDS

VGS

QT

Q2

Q3

Q1

16

20

24

28

32

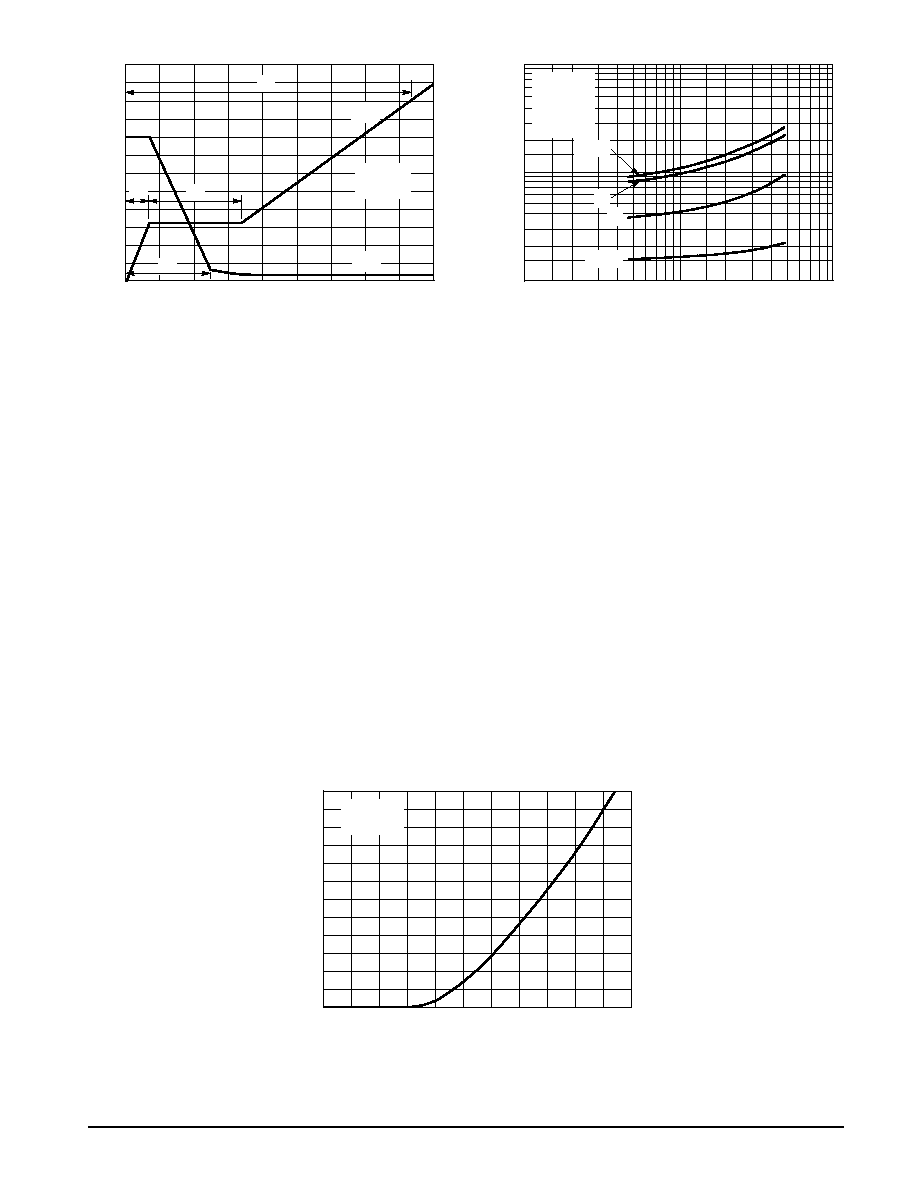

DRAINşTOşSOURCE DIODE CHARACTERISTICS

The switching characteristics of a MOSFET body diode

are very important in systems using it as a freewheeling or

commutating diode. Of particular interest are the reverse re-

covery characteristics which play a major role in determining

switching losses, radiated noise, EMI and RFI.

System switching losses are largely due to the nature of

the body diode itself. The body diode is a minority carrier de-

vice, therefore it has a finite reverse recovery time, trr, due to

the storage of minority carrier charge, QRR, as shown in the

typical reverse recovery wave form of Figure 15. It is this

stored charge that, when cleared from the diode, passes

through a potential and defines an energy loss. Obviously,

repeatedly forcing the diode through reverse recovery further

increases switching losses. Therefore, one would like a

diode with short trr and low QRR specifications to minimize

these losses.

The abruptness of diode reverse recovery effects the

amount of radiated noise, voltage spikes, and current ring-

ing. The mechanisms at work are finite irremovable circuit

parasitic inductances and capacitances acted upon by high

di/dts. The diode's negative di/dt during ta is directly con-

trolled by the device clearing the stored charge. However,

the positive di/dt during tb is an uncontrollable diode charac-

teristic and is usually the culprit that induces current ringing.

Therefore, when comparing diodes, the ratio of tb/ta serves

as a good indicator of recovery abruptness and thus gives a

comparative estimate of probable noise generated. A ratio of

1 is considered ideal and values less than 0.5 are considered

snappy.

Compared to Motorola standard cell density low voltage

MOSFETs, high cell density MOSFET diodes are faster

(shorter trr), have less stored charge and a softer reverse re-

covery characteristic. The softness advantage of the high

cell density diode means they can be forced through reverse

recovery at a higher di/dt than a standard cell MOSFET

diode without increasing the current ringing or the noise gen-

erated. In addition, power dissipation incurred from switching

the diode will be less due to the shorter recovery time and

lower switching losses.

0.3

0.4

0.5

0.6

0.7

1.4

0

1

2

2.5

3

VSD, SOURCEşTOşDRAIN VOLTAGE (VOLTS)

Figure 10. Diode Forward Voltage versus Current

I S

, SOURCE CURRENT

(AMPS)

VGS = 0 V

TJ = 25

░

C

1.5

0.8

0.9

0.5

1

1.1

1.2

1.3