MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

31

REV 1

©

Motorola, Inc. 1997

3/97

Quad 2-Input Exclusive

NOR Gate

HighPerformance SiliconGate CMOS

The MC74HC7266A is identical in pinout to the LS266 and the HC266.

The HC7266 has standard CMOS outputs instead of opendrain outputs.

The device inputs are compatible with standard CMOS outputs; with

pullup resistors, they are compatible with LSTTL outputs.

·

Output Drive Capability: 10 LSTTL Loads

·

Outputs Directly Interface to CMOS, NMOS, and TTL

·

Operating Voltage Range: 2 to 6 V

·

Low Input Current: 1

µ

A

·

High Noise Immunity Characteristic of CMOS Devices

·

In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

·

Chip Complexity: 56 FETs or 14 Equivalent Gates

LOGIC DIAGRAM

A1

B1

1

2

3

Y1

A2

B2

5

6

4

Y2

A3

B3

8

9

10

Y3

A4

B4

12

13

11

Y4

Y = A

B

Y

=

AB + A B

PIN 14 = VCC

PIN 7 = GND

MC74HC7266A

FUNCTION TABLE

PIN ASSIGNMENT

Y2

Y1

B1

A1

GND

B2

A2

11

12

13

14

8

9

10

5

4

3

2

1

7

6

Y3

Y4

A4

B4

VCC

A3

B3

Inputs

Output

A

B

Y

L

L

H

L

H

L

H

L

L

H

H

H

D SUFFIX

SOIC PACKAGE

CASE 751A03

N SUFFIX

PLASTIC PACKAGE

CASE 64606

1

14

1

14

ORDERING INFORMATION

MC74HCXXXXAN

MC74HCXXXXAD

MC74HCXXXXADT

Plastic

SOIC

TSSOP

1

14

DT SUFFIX

TSSOP PACKAGE

CASE 948G01

MC74HC7266A

MOTOROLA

HighSpeed CMOS Logic Data

DL129 -- Rev 6

32

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

MAXIMUM RATINGS*

ÎÎÎ

ÎÎÎ

Symbol

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

Value

ÎÎÎ

ÎÎÎ

Unit

ÎÎÎ

ÎÎÎ

VCC

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Supply Voltage (Referenced to GND)

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

0.5 to + 7.0

ÎÎÎ

ÎÎÎ

V

ÎÎÎ

ÎÎÎ

Vin

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Input Voltage (Referenced to GND)

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

0.5 to VCC + 0.5

ÎÎÎ

ÎÎÎ

V

ÎÎÎ

ÎÎÎ

Vout

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Output Voltage (Referenced to GND)

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

0.5 to VCC + 0.5

ÎÎÎ

ÎÎÎ

V

ÎÎÎ

ÎÎÎ

Iin

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Input Current, per Pin

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

±

20

ÎÎÎ

ÎÎÎ

mA

ÎÎÎ

ÎÎÎ

Iout

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Output Current, per Pin

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

±

25

ÎÎÎ

ÎÎÎ

mA

ÎÎÎ

ÎÎÎ

ICC

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Supply Current, VCC and GND Pins

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

±

50

ÎÎÎ

ÎÎÎ

mA

ÎÎÎ

Î

Î

Î

Î

Î

Î

PD

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Power Dissipation in Still Air

Plastic DIP

SOIC Package

TSSOP Package

ÎÎÎÎÎÎ

Î

ÎÎÎÎ

Î

Î

ÎÎÎÎ

Î

750

500

450

ÎÎÎ

Î

Î

Î

Î

Î

Î

mW

ÎÎÎ

Î

Î

Î

Tstg

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Storage Temperature

ÎÎÎÎÎÎ

Î

ÎÎÎÎ

Î

65 to + 150

ÎÎÎ

Î

Î

Î

_

C

ÎÎÎ

Î

Î

Î

ÎÎÎ

TL

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Lead Temperature, 1 mm from Case for 10 Seconds

(Plastic DIP, SOIC or TSSOP Package)

ÎÎÎÎÎÎ

Î

ÎÎÎÎ

Î

ÎÎÎÎÎÎ

260

ÎÎÎ

Î

Î

Î

ÎÎÎ

_

C

* Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

Derating -- Plastic DIP: 10 mW/

_

C from 65

_

to 125

_

C

SOIC Package: 7 mW/

_

C from 65

_

to 125

_

C

TSSOP Package: 6.1 mW/

_

C from 65

_

to 125

_

C

For high frequency or heavy load considerations, see Chapter 2 of the Motorola HighSpeed CMOS Data Book (DL129/D).

RECOMMENDED OPERATING CONDITIONS

ÎÎÎÎ

ÎÎÎÎ

Symbol

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎ

ÎÎÎ

Min

ÎÎÎ

ÎÎÎ

Max

ÎÎÎ

ÎÎÎ

Unit

ÎÎÎÎ

ÎÎÎÎ

VCC

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Supply Voltage (Referenced to GND)

ÎÎÎ

ÎÎÎ

2.0

ÎÎÎ

ÎÎÎ

6.0

ÎÎÎ

ÎÎÎ

V

ÎÎÎÎ

ÎÎÎÎ

Vin, Vout

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

DC Input Voltage, Output Voltage (Referenced to GND)

ÎÎÎ

ÎÎÎ

0

ÎÎÎ

ÎÎÎ

VCC

ÎÎÎ

ÎÎÎ

V

ÎÎÎÎ

ÎÎÎÎ

TA

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Operating Temperature, All Package Types

ÎÎÎ

ÎÎÎ

55

ÎÎÎ

ÎÎÎ

+ 125

ÎÎÎ

ÎÎÎ

_

C

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

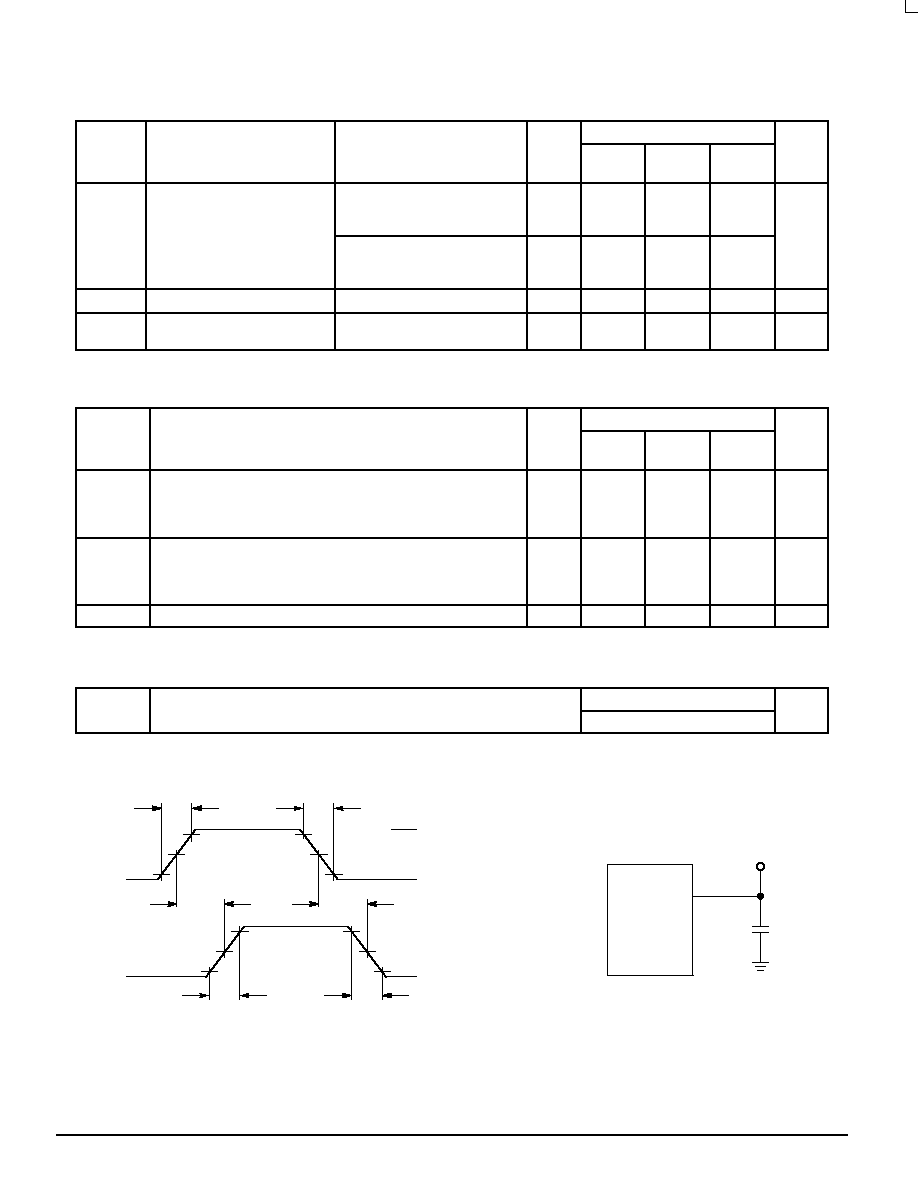

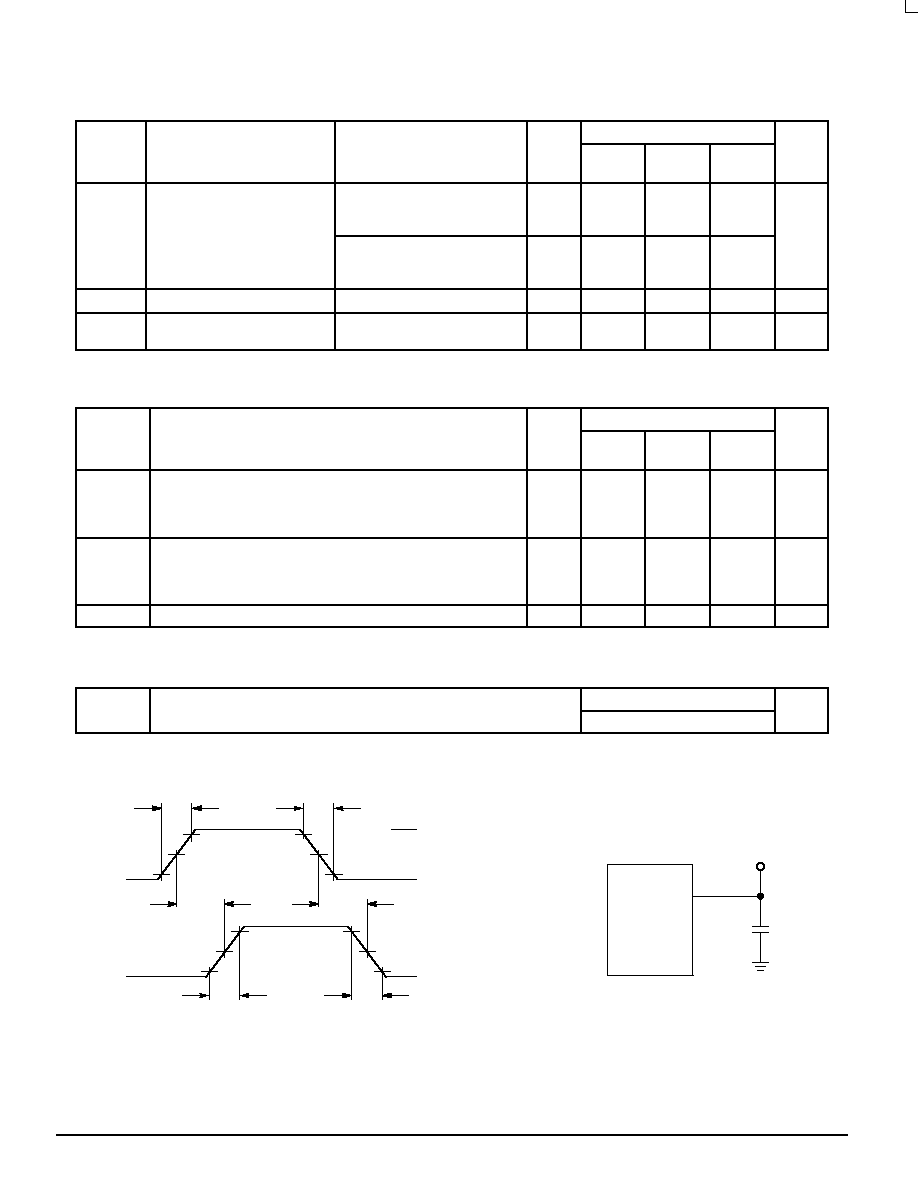

tr, tf

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Input Rise and Fall Time

VCC = 2.0 V

(Figure 1)

VCC = 4.5 V

VCC = 6.0 V

ÎÎÎ

Î

Î

Î

ÎÎÎ

0

0

0

ÎÎÎ

Î

Î

Î

ÎÎÎ

1000

500

400

ÎÎÎ

Î

Î

Î

ÎÎÎ

ns

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND)

ÎÎÎÎ

ÎÎÎÎ

S

b l

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

P

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

T

C

di i

ÎÎÎÎ

ÎÎÎÎ

V

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Guaranteed Limit

ÎÎÎ

ÎÎÎ

U i

ÎÎÎÎ

Î

ÎÎ

Î

Symbol

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Parameter

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Test Conditions

ÎÎÎÎ

Î

ÎÎ

Î

VCC

V

ÎÎÎ

Î

ÎÎ

55 to

25

_

C

ÎÎÎÎ

Î

ÎÎ

Î

v

85

_

C

ÎÎÎÎ

Î

ÎÎ

Î

v

125

_

C

ÎÎÎ

Î

Î

Î

Unit

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

VIH

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Minimum HighLevel Input

Voltage

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Vout = 0.1 V or VCC 0.1 V

|Iout|

v

20

µ

A

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

Î

ÎÎ

ÎÎÎ

1.5

2.1

3.15

4.2

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

1.5

2.1

3.15

4.2

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

1.5

2.1

3.15

4.2

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

V

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

VIL

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Maximum LowLevel Input

Voltage

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Vout = 0.1 V or VCC 0.1 V

|Iout|

v

20

µ

A

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

Î

ÎÎ

ÎÎÎ

0.5

0.9

1.35

1.8

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

0.5

0.9

1.35

1.8

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

0.5

0.9

1.35

1.8

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

V

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

VOH

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Minimum HighLevel Output

Voltage

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Vin = VIH or VIL

|Iout|

v

20

µ

A

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

2.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

Î

ÎÎ

ÎÎÎ

1.9

4.4

5.9

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

1.9

4.4

5.9

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

1.9

4.4

5.9

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

V

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Vin = VIH or VIL |Iout|

v

2.4 mA

|Iout|

v

4.0 mA

|Iout|

v

5.2 mA

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

3.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

ÎÎÎ

2.48

3.98

5.48

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

2.34

3.84

5.34

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

2.20

3.70

5.20

ÎÎÎ

Î

Î

Î

ÎÎÎ

This device contains protection

circuitry to guard against damage

due to high static voltages or electric

fields. However, precautions must

be taken to avoid applications of any

voltage higher than maximum rated

voltages to this highimpedance cir-

cuit. For proper operation, Vin and

Vout should be constrained to the

range GND

v

(Vin or Vout)

v

VCC.

Unused inputs must always be

tied to an appropriate logic voltage

level (e.g., either GND or VCC).

Unused outputs must be left open.

MC74HC7266A

HighSpeed CMOS Logic Data

DL129 -- Rev 6

33

MOTOROLA

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND)

ÎÎÎ

ÎÎÎ

Unit

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Guaranteed Limit

ÎÎÎÎ

ÎÎÎÎ

VCC

V

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Test Conditions

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎÎ

ÎÎÎÎ

Symbol

ÎÎÎ

ÎÎÎ

ÎÎÎ

Unit

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

v

125

_

C

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

v

85

_

C

ÎÎÎ

ÎÎÎ

ÎÎÎ

55 to

25

_

C

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

VCC

V

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Test Conditions

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎÎ

ÎÎÎÎ

ÎÎÎÎ

Symbol

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

VOL

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Maximum LowLevel Output

Voltage

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Vin = VIH or VIL

|Iout|

v

20

µ

A

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

2.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

ÎÎÎ

0.1

0.1

0.1

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

0.1

0.1

0.1

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

0.1

0.1

0.1

ÎÎÎ

Î

Î

Î

ÎÎÎ

V

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎ

Î

Vin = VIH or VIL |Iout|

v

2.4 mA

|Iout|

v

4.0 mA

|Iout|

v

5.2 mA

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

3.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

Î

ÎÎ

0.26

0.26

0.26

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

0.33

0.33

0.33

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

0.40

0.40

0.40

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎÎ

Î

ÎÎ

Î

Iin

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Maximum Input Leakage Current

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

Vin = VCC or GND

ÎÎÎÎ

Î

ÎÎ

Î

6.0

ÎÎÎ

Î

ÎÎ

±

0.1

ÎÎÎÎ

Î

ÎÎ

Î

±

1.0

ÎÎÎÎ

Î

ÎÎ

Î

±

1.0

ÎÎÎ

Î

Î

Î

µ

A

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

ICC

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Maximum Quiescent Supply

Current (per Package)

ÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎ

Vin = VCC or GND

Iout = 0

µ

A

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

6.0

ÎÎÎ

Î

ÎÎ

ÎÎÎ

1

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

10

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

40

ÎÎÎ

Î

Î

Î

ÎÎÎ

µ

A

NOTE: Information on typical parametric values can be found in Chapter 2 of the Motorola HighSpeed CMOS Data Book (DL129/D).

AC ELECTRICAL CHARACTERISTICS

( CL = 50 pF, Input tr = tf = 6 ns)

ÎÎÎÎ

ÎÎÎÎ

S

b l

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

P

ÎÎÎÎ

ÎÎÎÎ

V

ÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎ

Guaranteed Limit

ÎÎÎ

ÎÎÎ

U i

ÎÎÎÎ

ÎÎÎÎ

Symbol

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎÎ

ÎÎÎÎ

VCC

V

ÎÎÎ

ÎÎÎ

55 to

25

_

C

ÎÎÎÎ

ÎÎÎÎ

v

85

_

C

ÎÎÎÎ

ÎÎÎÎ

v

125

_

C

ÎÎÎ

ÎÎÎ

Unit

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

tPLH,

tPHL

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Propagation Delay, Input A or B to Output Y

(Figures 1 and 2)

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

Î

ÎÎ

ÎÎÎ

100

80

20

17

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

125

90

25

21

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

150

110

25

19

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

tTLH,

tTHL

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Output Transition Time, Any Output

(Figures 1 and 2)

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎ

Î

ÎÎ

Î

ÎÎ

ÎÎÎ

75

30

15

13

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

95

40

19

16

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

110

55

22

19

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

ÎÎÎÎ

Cin

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Input Capacitance

ÎÎÎÎ

ÎÎÎÎ

--

ÎÎÎ

ÎÎÎ

10

ÎÎÎÎ

ÎÎÎÎ

10

ÎÎÎÎ

ÎÎÎÎ

10

ÎÎÎ

ÎÎÎ

pF

NOTES:

1. For propagation delays with loads other than 50 pF, see Chapter 2 of the Motorola HighSpeed CMOS Data Book (DL129/D).

2. Information on typical parametric values can be found in Chapter 2 of the Motorola HighSpeed CMOS Data Book (DL129/D).

C

P

Di

i

i

C

i

(P

G

)*

Typical @ 25

°

C, VCC = 5.0 V

F

CPD

Power Dissipation Capacitance (Per Gate)*

33

pF

* Used to determine the noload dynamic power consumption: PD = CPD VCC2f + ICC VCC. For load considerations, see Chapter 2 of the

Motorola HighSpeed CMOS Data Book (DL129/D).

* Includes all probe and jig capacitance

CL*

TEST POINT

DEVICE

UNDER

TEST

OUTPUT

Figure 1. Switching Waveforms

Figure 2. Test Circuit

OUTPUT Y

INPUT

A OR B

90%

50%

10%

tTLH

tTHL

tPLH

tPHL

tr

tf

GND

VCC

90%

50%

10%

MC74HC7266A

MOTOROLA

HighSpeed CMOS Logic Data

DL129 -- Rev 6

34

LOGIC DETAIL

(1/4 of Device)

A

B

Y

APPLICATION INFORMATION

Bi

L is defined as biphaselevel code. Also known as

Manchester Code, this technique utilizes binary phase shift

keying (PSK). The Bi

L output shown in Figure 3 carries

both data and synchronization information; therefore, sepa-

rate data and clock lines are not required to transfer informa-

tion. A positivegoing transition in the middle of the bit

interval indicates a logic zero; a negativegoing transition in-

dicates a logic one (see Figure 4).

NRZL shown in Figure 3 is nonreturntozero level

code. This is simply serial data out of a shift register, such as

the HC597.

The Bi

L signal must be phase coherent (i.e., no

glitches). Therefore, NRZL and clock transitions must be

coincident.

Figure 3. BiphaseLevel Encoder (Manchester Encoder)

NRZL

BI

L

CLOCK

1/4

HC7266A

POSITIVE

LOGIC DATA

1

0

1

1

0

0

BIT

INTERVAL

NRZL

CLOCK

BI

L

Figure 4. Timing Diagram

MC74HC7266A

HighSpeed CMOS Logic Data

DL129 -- Rev 6

35

MOTOROLA

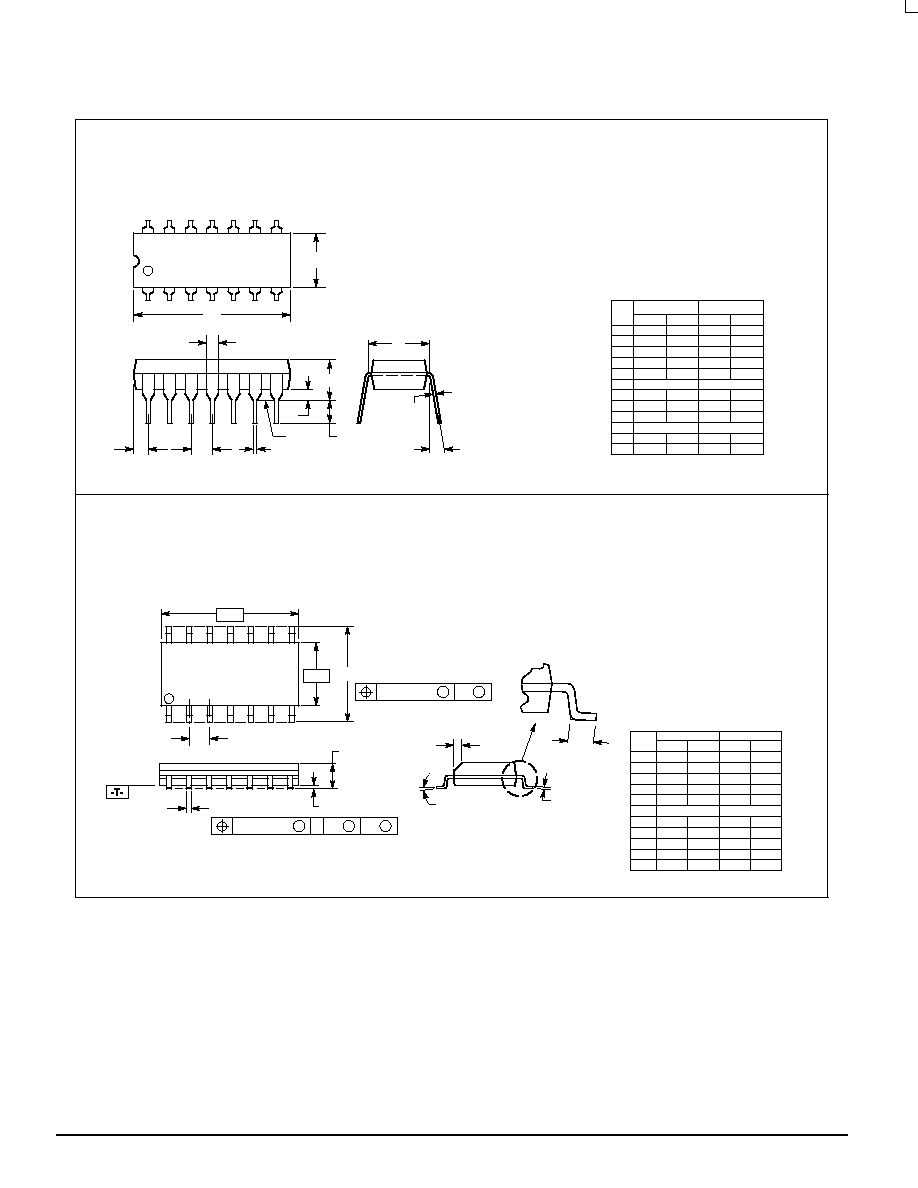

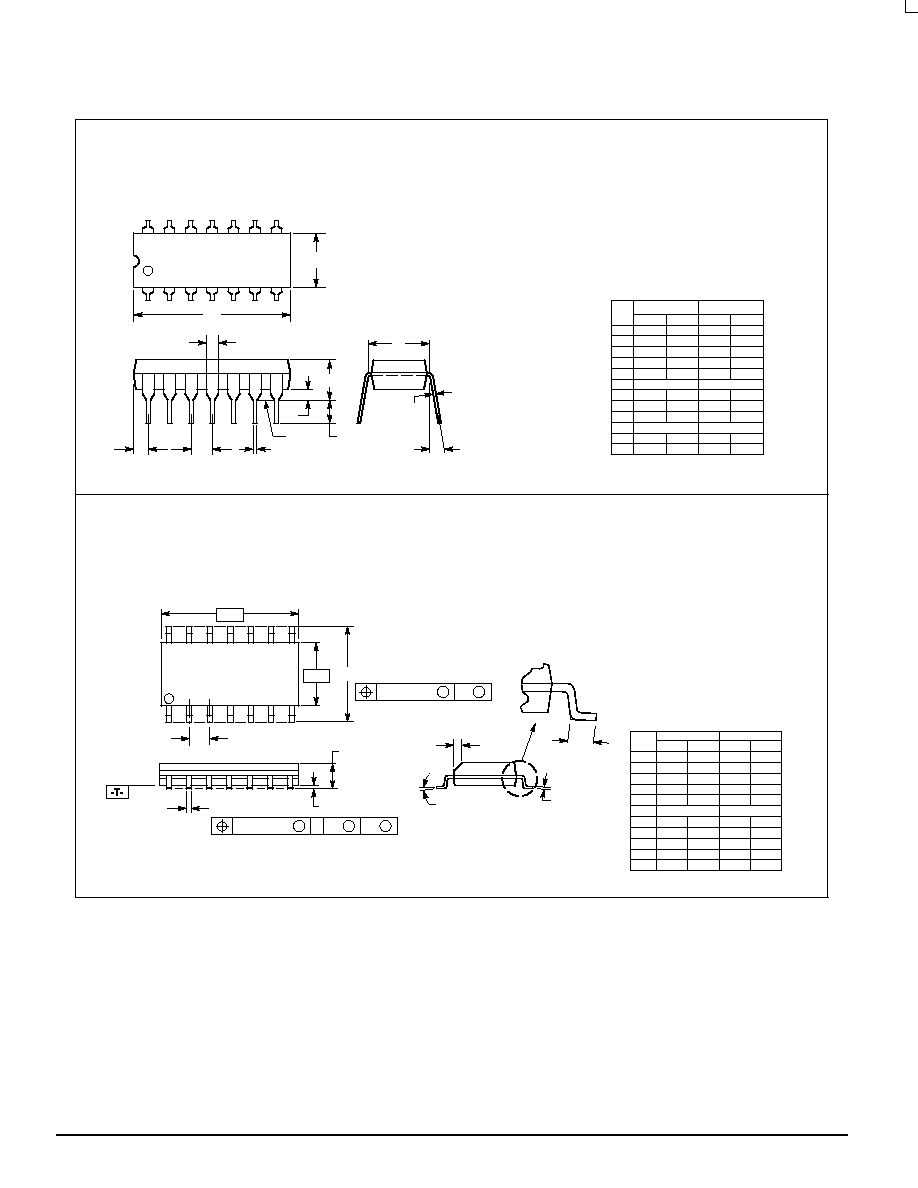

OUTLINE DIMENSIONS

N SUFFIX

PLASTIC DIP PACKAGE

CASE 64606

ISSUE L

NOTES:

1. LEADS WITHIN 0.13 (0.005) RADIUS OF TRUE

POSITION AT SEATING PLANE AT MAXIMUM

MATERIAL CONDITION.

2. DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

3. DIMENSION B DOES NOT INCLUDE MOLD

FLASH.

4. ROUNDED CORNERS OPTIONAL.

1

7

14

8

B

A

F

H

G

D

K

C

N

L

J

M

SEATING

PLANE

DIM

MIN

MAX

MIN

MAX

MILLIMETERS

INCHES

A

0.715

0.770

18.16

19.56

B

0.240

0.260

6.10

6.60

C

0.145

0.185

3.69

4.69

D

0.015

0.021

0.38

0.53

F

0.040

0.070

1.02

1.78

G

0.100 BSC

2.54 BSC

H

0.052

0.095

1.32

2.41

J

0.008

0.015

0.20

0.38

K

0.115

0.135

2.92

3.43

L

0.300 BSC

7.62 BSC

M

0

10 0 10

N

0.015

0.039

0.39

1.01

_

_

_

_

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751A03

ISSUE F

MIN

MIN

MAX

MAX

MILLIMETERS

INCHES

DIM

A

B

C

D

F

G

J

K

M

P

R

8.55

3.80

1.35

0.35

0.40

0.19

0.10

0

°

5.80

0.25

8.75

4.00

1.75

0.49

1.25

0.25

0.25

7

°

6.20

0.50

0.337

0.150

0.054

0.014

0.016

0.008

0.004

0

°

0.228

0.010

0.344

0.157

0.068

0.019

0.049

0.009

0.009

7

°

0.244

0.019

1.27 BSC

0.050 BSC

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

A

B

P

7 PL

G

C

K

SEATING

PLANE

D

14 PL

M

J

R

X 45

°

1

7

8

14

0.25 (0.010)

T

B

A

M

S

S

B

0.25 (0.010)

M

M

F