FEATURES

s

Low skew

s

Differential PECL inputs

s

Differential cut-off PECL outputs capable of driving

25

load for driving data bus

s

Tri-state TTL output

s

TTL select and enable input

s

Internal 75K

PECL input pull-down resistors

s

PECL I/O fully compatible with industry standard

s

Available in 28-pin PLCC package

The SY100S863 is a PECL 8:1 multiplexer designed for

use in new, high-performance PECL systems. It has

differential PECL outputs and a standard TTL output. The

TTL select inputs (SEL

0

, SEL

1

, SEL

2

) determine which one

of the eight differential PECL data inputs (D

0

D

7

) is

propagated to the outputs. The enable pin, EN, is provided

for expansion. When EN is at a TTL logic one level, both

PECL and TTL outputs are enabled. When the enable pin

is set to TTL logic zero level, both PECL outputs of the

differential pair are in cut-off and the TTL output is in a

three-state condition.

DESCRIPTION

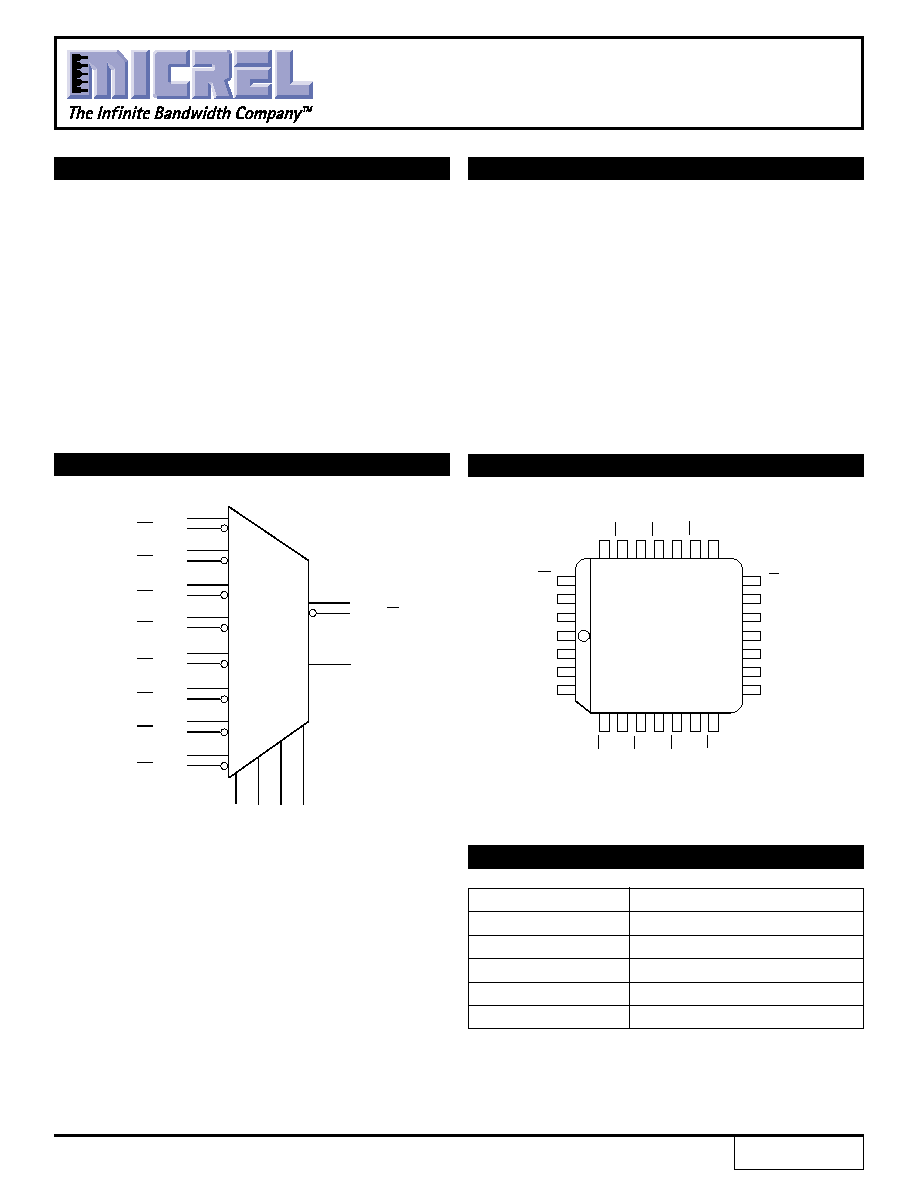

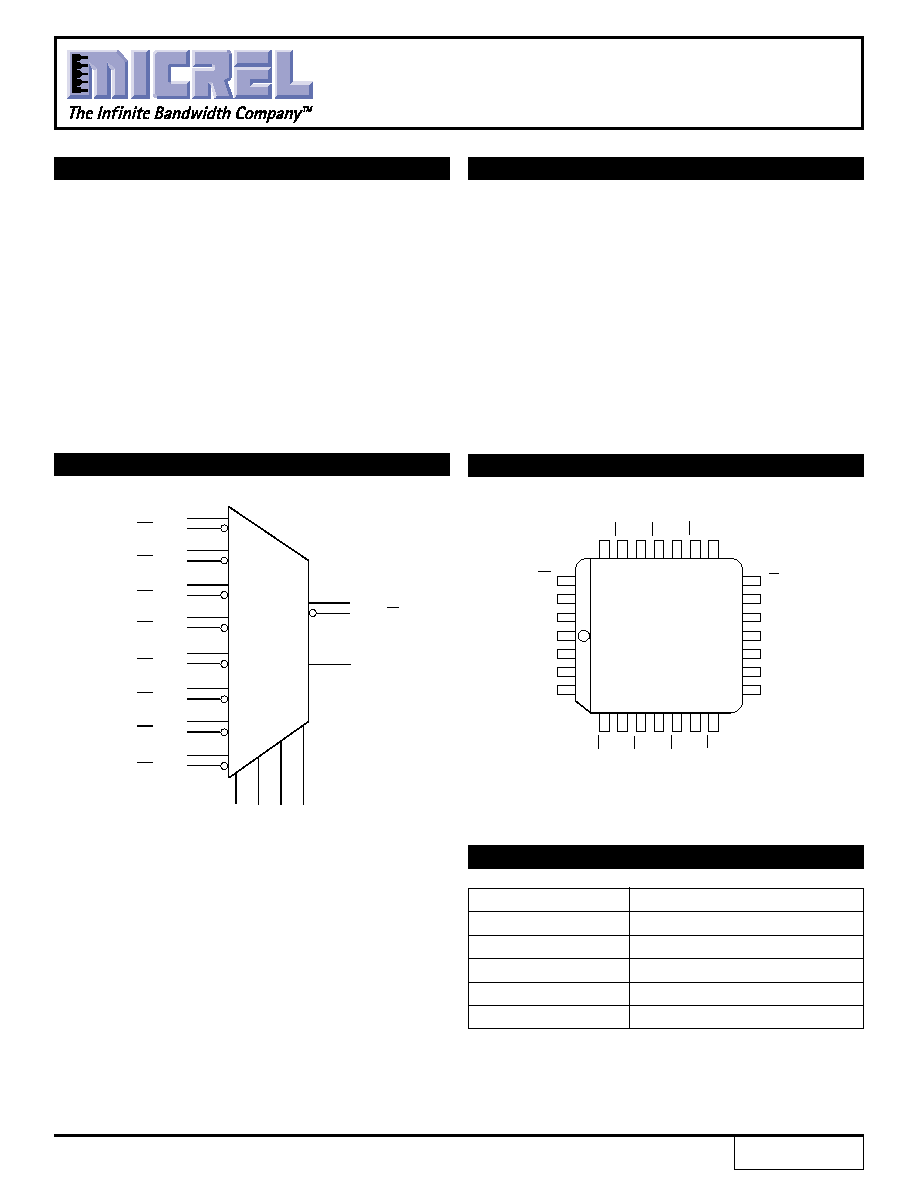

BLOCK DIAGRAM

8:1

MUX

8 DIFFERENTIAL

PECL INPUTS

D

0

D

0

D

1

D

1

D

2

D

2

D

3

D

3

D

4

D

4

D

5

D

5

D

6

D

6

D

7

D

7

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(27)

(26)

(25)

(24)

(23)

(22)

(21)

(20)

(17)

(18)

Q

Q

(13) Q

TTL

(15)

(28)

(2)

(3)

EN

SEL

0

SEL

1

SEL

2

TTL INPUTS

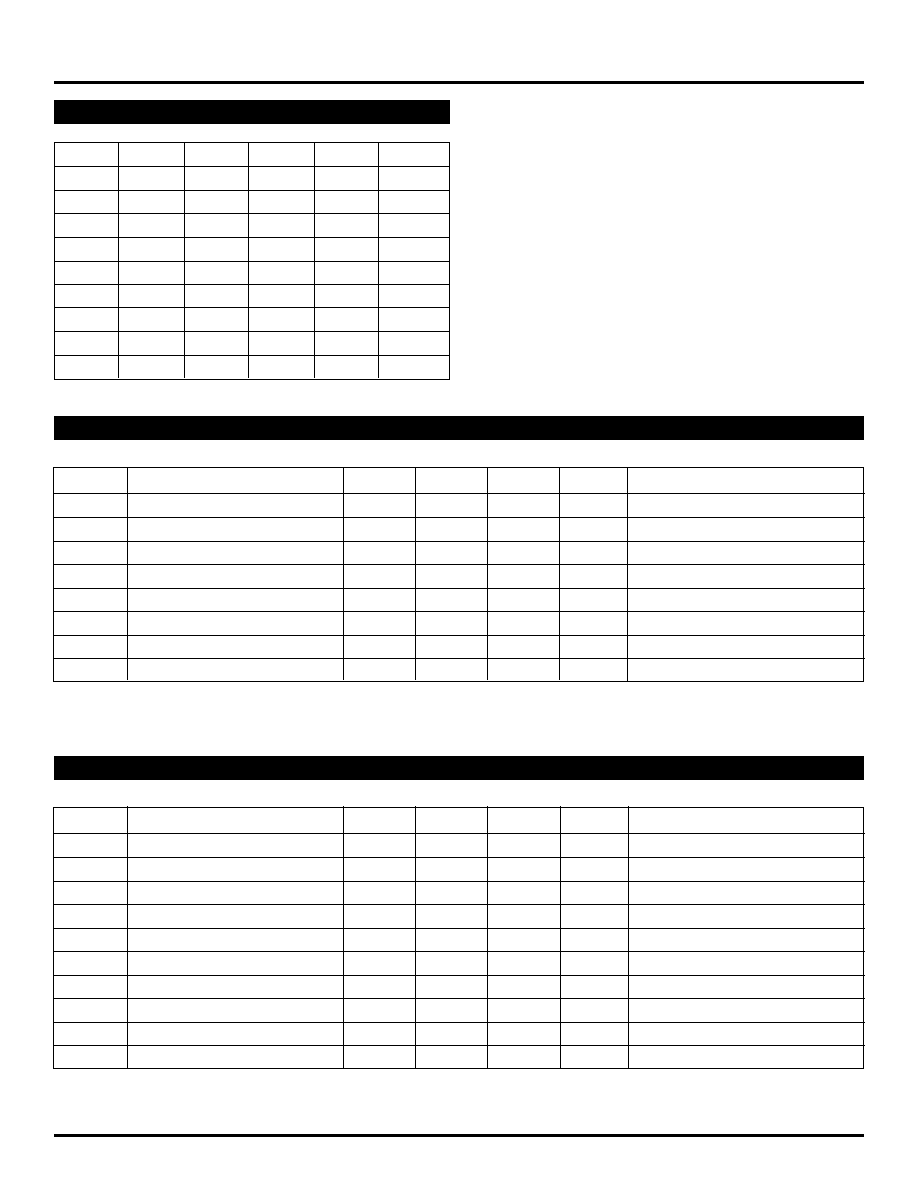

PIN CONFIGURATION

Pin

Function

D

0

, /D

0

D

7

, /D

7

Differential PECL Input Pairs

Q, /Q

Differential PECL Outputs

Q

TTL

TTL Output

EN

Enable Input

SEL

0,1,2

Select Inputs

PIN NAMES

SY100S863

8-INPUT PECL

DIFFERENTIAL MUX

WITH TTL SELECTS

TOP VIEW

PLCC

J28-1

26

27

28

1

2

3

4

18

17

16

15

14

13

12

Q

V

CC

EN

Q

TTL

Q

V

CCT

V

GT

25 24 23 22 21 20 19

5

6

7

8

9

10 11

V

EE

D

4

SEL

0

SEL

2

D

0

D

4

SEL

1

D

2

D

2

D

3

D

1

D

0

D

1

D

3

D

5

D

6

D

6

D

7

D

5

D

7

V

CCO

1

Rev.: E

Amendment: /0

Issue Date:

May 2000

2

SY100S863

Micrel

EN

SEL

2

SEL

1

SEL

0

Q

Q

TTL

H

L

L

L

D

0

D

0

H

L

L

H

D

1

D

1

H

L

H

L

D

2

D

2

H

L

H

H

D

3

D

3

H

H

L

L

D

4

D

4

H

H

L

H

D

5

D

5

H

H

H

L

D

6

D

6

H

H

H

H

D

7

D

7

L

X

X

X

Z

Z

Symbol

Parameter

Min.

Typ.

Max.

Unit

Condition

V

OH

Output HIGH Voltage

2.4

2.9

--

V

I

OH

= 3mA

V

OL

Output LOW Voltage

--

0.3

0.5

V

I

OL

= 24mA

V

IH

Input HIGH Voltage

2.0

--

V

CC

V

V

IL

Input LOW Voltage

0

--

0.8

V

I

IH

Input HIGH Current

--

--

1.0

mA

V

IN

= 2.7V

I

IL

Input LOW Current

0.7

--

--

mA

V

IN

= 0.5V

V

IK

Input Clamp Voltage

1.2

--

--

V

I

IN

= 18mA

I

OS

Output Short Circuit Current

200

--

60

mA

V

OUT

= 0V, V

CCT

= 5.5V

I

OZHT

Tri-state Current Output HIGH

--

--

70

µ

A

V

OUT

= 2.7V

I

OZLT

Tri-state Current Output LOW

700

--

--

µ

A

V

OUT

= 0.5V

Symbol

Parameter

Min.

Typ.

Max.

Unit

Condition

V

OH

Output HIGH Voltage

(1)

3.975

4.045

4.13

V

Loading with 25

to 3V (V

CC

-2V)

V

OL

Output LOW Voltage

(1)

3.17

3.295

3.38

V

Loading with 25

to 3V (V

CC

-2V)

V

OZ

Cutoff Voltage

(1)

--

3

3.10

V

Loading with 25

to 3V (V

CC

-2V)

V

IH

Input HIGH Voltage

3.835

--

4.13

V

V

IL

Input LOW Voltage

3.17

--

3.525

V

I

IH

Input HIGH Current

--

--

350

µ

A

V

IN

= V

IH

(Max.)

I

IL

Input LOW Current

0.50

--

--

µ

A

V

IN

= V

IL

(Min.)

I

CC

V

CC

Supply Current

--

73

88

mA

PECL DC ELECTRICAL CHARACTERISTICS

TTL DC ELECTRICAL CHARACTERISTICS

V

CC

= V

CCO

= V

CCT

= 5.0V

±

5%; V

EE

= V

GT

= GND

V

CC

= V

CCO

= V

CCT

= 5.0V

±

5%; V

EE

= V

GT

= GND

NOTE:

1. Levels shown are for V

CCO

= 5.0V and will vary 1:1 with powers.

TRUTH TABLE

3

SY100S863

Micrel

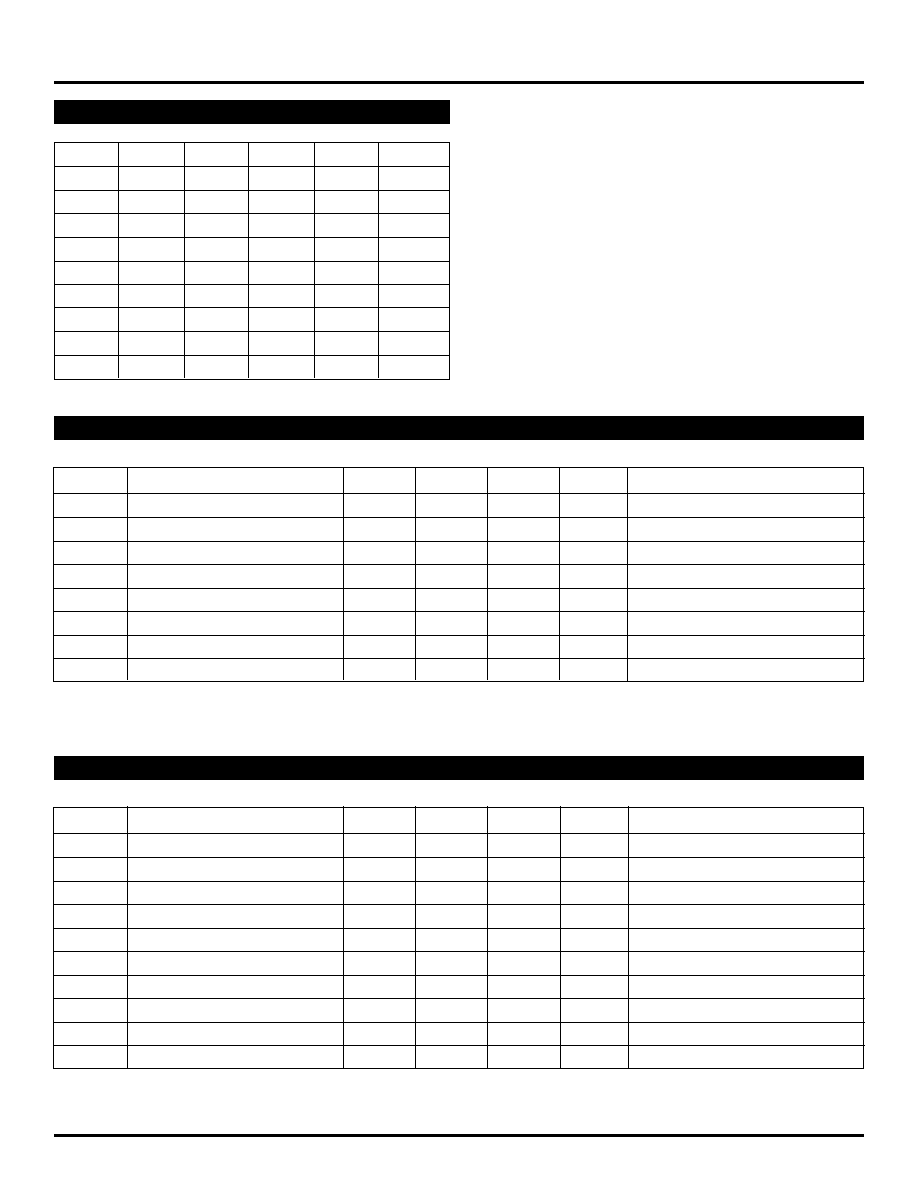

PECL AC ELECTRICAL CHARACTERISTICS

NOTES:

1. Part-to-part skew is defined as Max. Min. value at the given temperature.

2. R

L

= 50

3. Figures 1 and 2

V

CC

= V

CCO

= +5.0V

±

5%; V

EE

= V

GT

= GND

T

A

= 0

°

C

T

A

= +25

°

C

T

A

= +85

°

C

Symbol

Parameter

Min.

Typ.

Max.

Min.

Typ.

Max.

Min.

Typ.

Max.

Unit

Condition

t

PLH

Propagation Delay

(1),(2)

ps

t

PHL

D to Q

500

--

900

500

--

900

500

--

900

SEL

0

to Q

300

--

2000

300

--

2000

300

--

2000

SEL

1

to Q

300

--

1750

300

--

1750

300

--

1750

SEL

2

to Q

300

--

1500

300

--

1500

300

--

1500

t

PZH

EN to Q

(3)

300

--

1750

300

--

1750

300

--

1750

ps

(Cutoff to HIGH)

t

PHZ

EN to Q

(3)

300

--

1300

300

--

1300

300

--

1300

(HIGH to Cutoff)

t

r

Output Rise/Fall Times

(2)

300

400

600

300

400

600

300

400

600

ps

t

f

20% to 80%

TTL AC ELECTRICAL CHARACTERISTICS

V

CC

= V

CCO

= 5V

±

5%; V

EE

= V

GT

= GND

T

A

= 0

°

C

T

A

= +25

°

C

T

A

= +85

°

C

Symbol

Parameter

Min.

Typ.

Max.

Min.

Typ.

Max.

Min.

Typ.

Max.

Unit

Condition

t

PLH

Propagation Delay

(1)(2)

ns

t

PHL

D to Q

TTL

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

SEL

0

to Q

TTL

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

SEL

1

to Q

TTL

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

SEL

2

to Q

TTL

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

t

PZH

EN to TTL Output

(2)

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

ns

t

PZL

(Enable Time)

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

t

PHZ

EN to TTL Output

(2)

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

ns

t

PLZ

(Disable Time)

2.5

--

5.0

2.5

--

5.0

2.5

--

5.0

t

r

Output Rise/Fall Time

(3)

ns

t

f

0.8V to 2.4V

0.3

--

1.6

0.3

--

1.6

0.3

--

1.6

0.8Vto 2.0V

NOTES:

1. Part-to-part skew is defined as Max. Min. value at the given temperature.

2. Figures 3 and 4

3. C

L

= 25p

F

4

SY100S863

Micrel

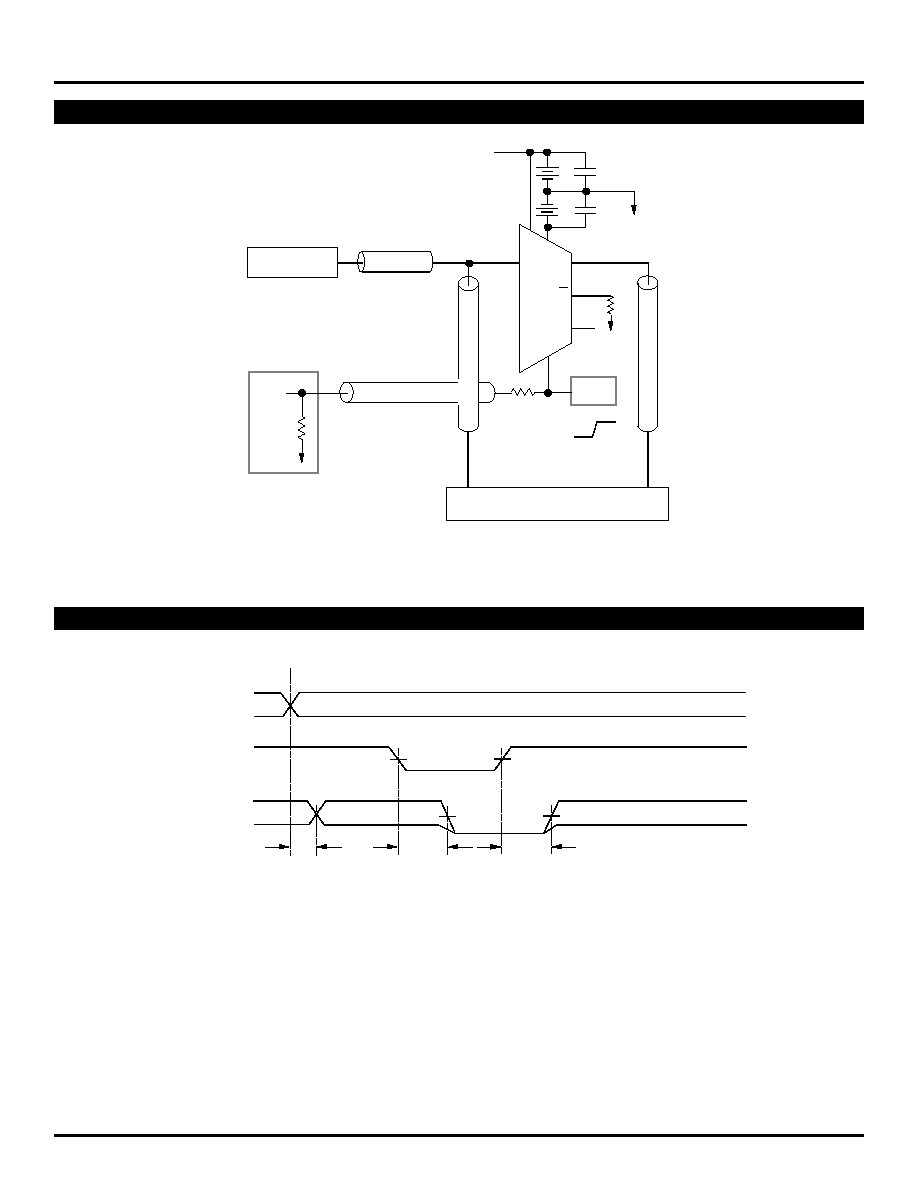

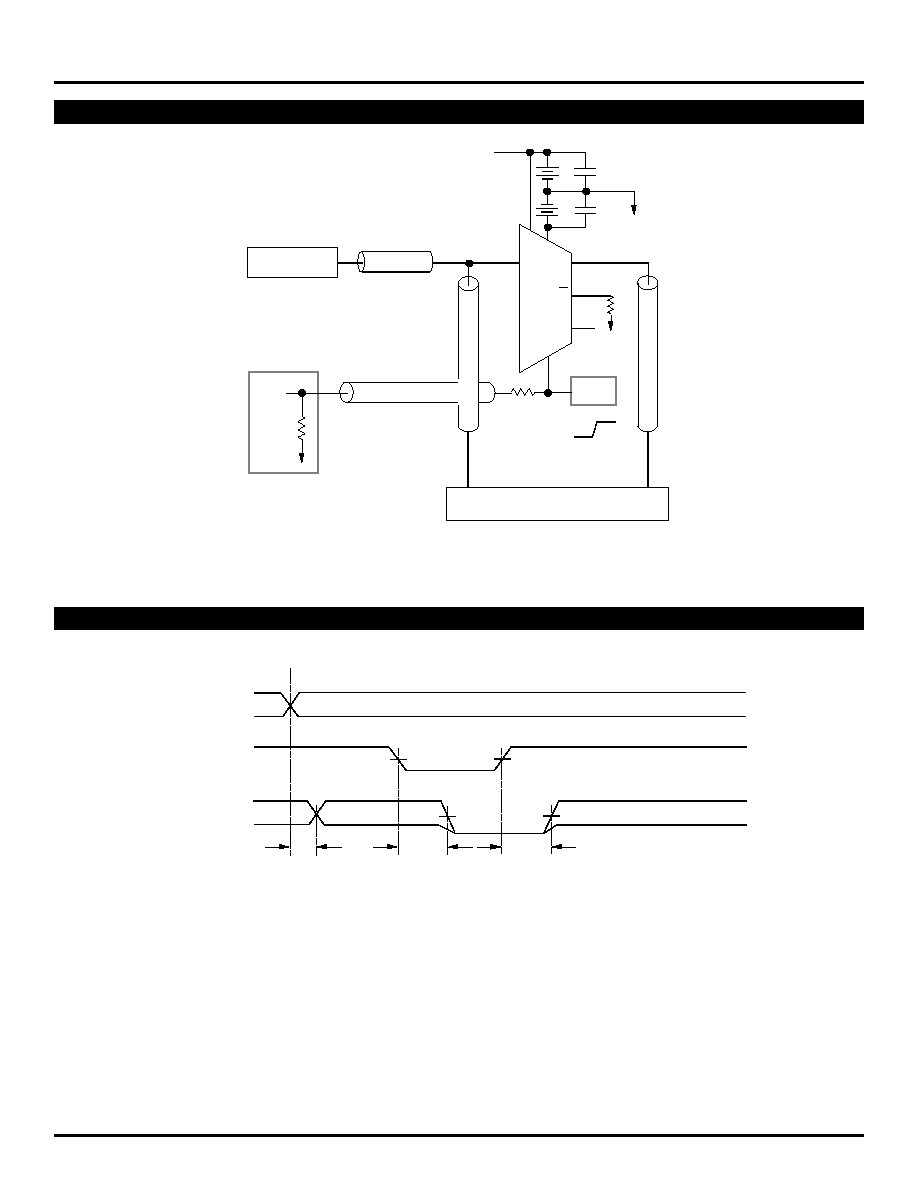

PECL-TO-PECL SWITCHING WAVEFORMS

Figure 2. PECL-to-PECL Transition -- Propagation Delay and Transition Times

PULSE

GENERATOR

D

Q

Q

Q

TTL

EN

DUT

450

F

TTL

-3V

0V

S

TTL

CH C

R

T

50

CH A

CH B

OSCILLOSCOPE

V

CC

, V

CCT

& V

CCO

V

EE

, V

GT

0.1

µ

0.1

µ

2V

3V

USE OSCILLOSCOPE

INTERNAL 50

LOAD

FOR TERMINATION.

50

Figure 1. PECL-to-PECL AC Test Circuit

t

PD

PECL DATA

ENABLE

PECL OUTPUT

V

OH

= 4.1V

V

OL

= 3.3V

V

OZ

= 3V

t

PHZ

t

PZH

PECL-TO-PECL TEST CIRCUITRY

5

SY100S863

Micrel

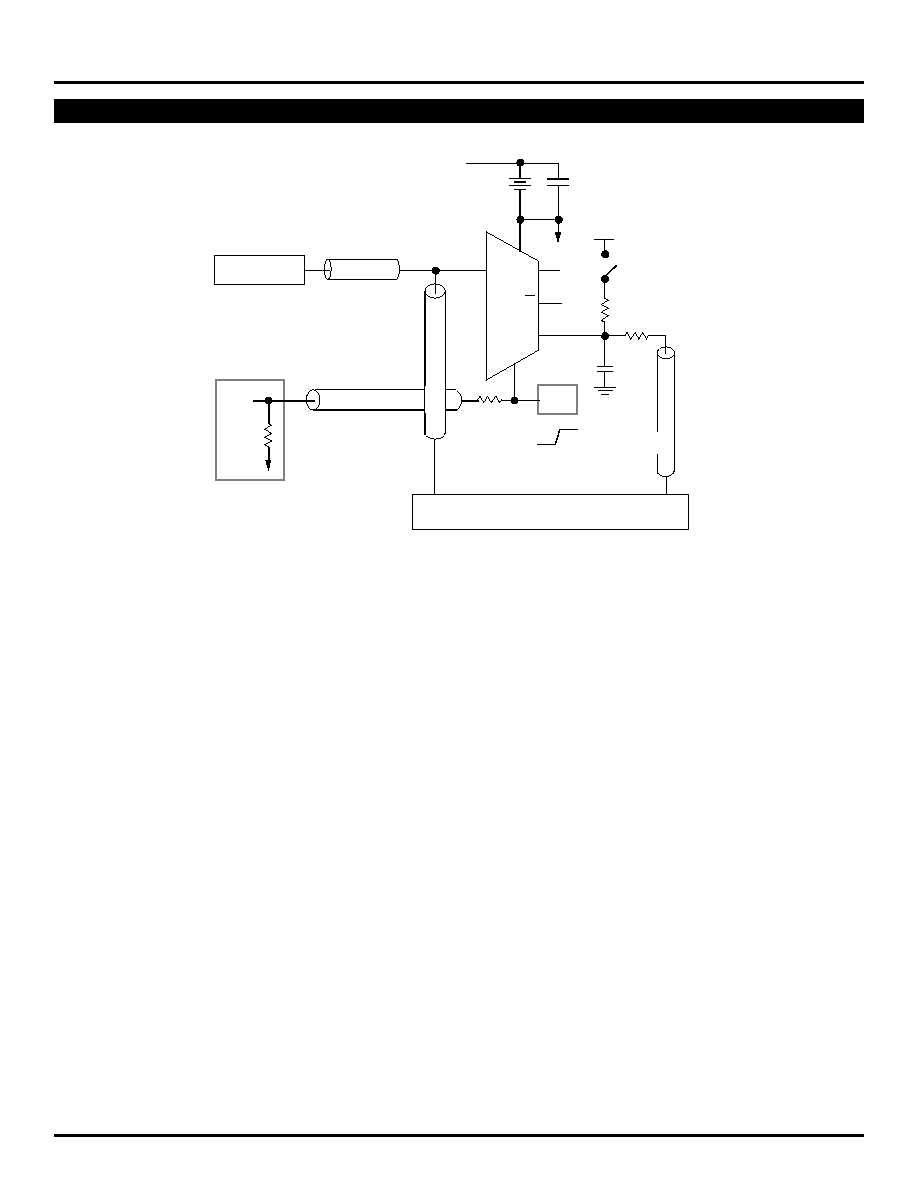

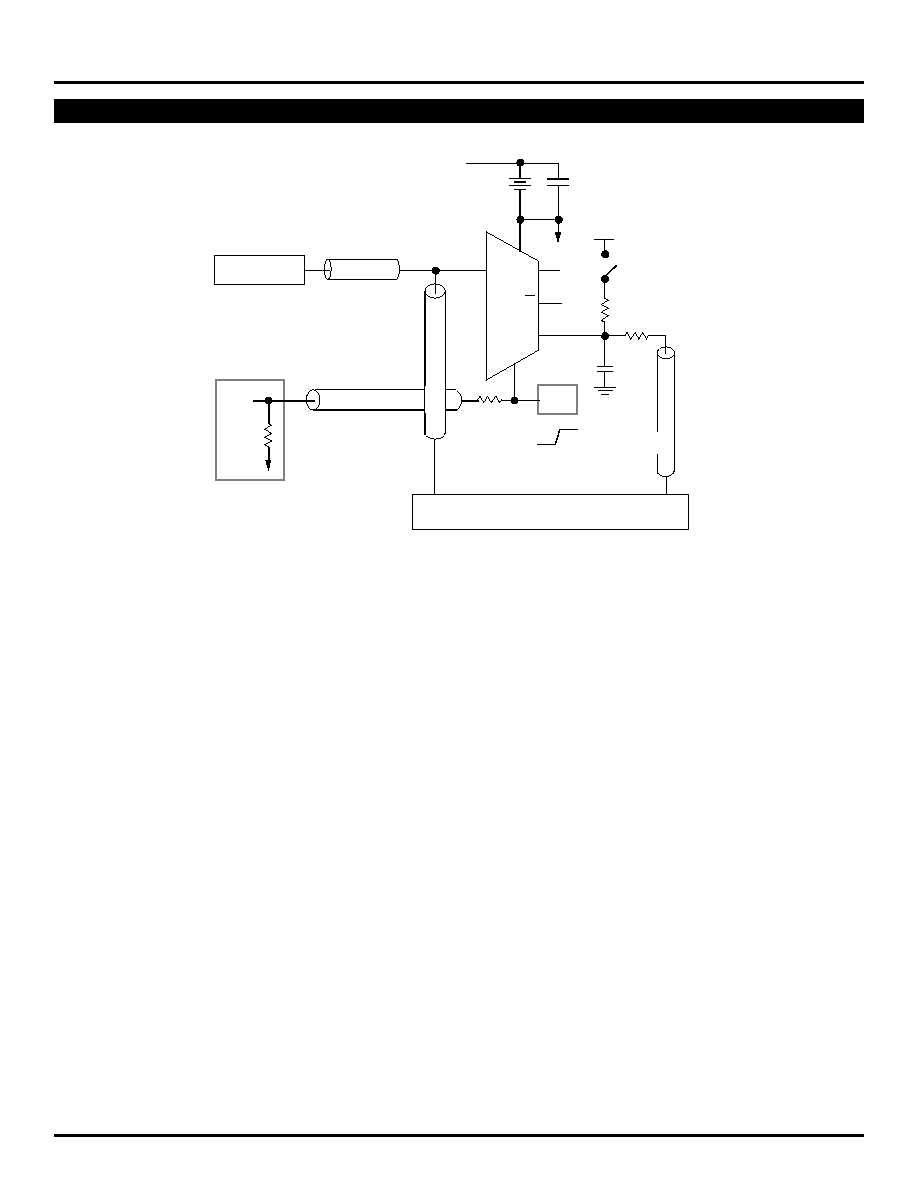

PECL-TO-TTL TEST CIRCUITRY

PULSE

GENERATOR

D

Q

Q

Q

TTL

EN

DUT

450

F

TTL

-3V

0V

S

TTL

CH C

R

T

50

CH A

CH B

OSCILLOSCOPE

USE OSCILLOSCOPE

INTERNAL 50

LOAD

FOR TERMINATION.

450

V

CC

, V

CCT

& V

CCO

V

EE

, V

GT

0.1

µ

5V

7V

50pF

LZ/ZL

Three-State

Pull-up

500

Figure 3. PECL-to-TTL AC Test Circuit