General Description

The MAX1492/MAX1494 low-power, 3.5- and 4.5-digit,

analog-to-digital converters (ADCs) with integrated liquid

crystal display (LCD) drivers operate from a single 2.7V

to 5.25V power supply. They include an internal refer-

ence, a high-accuracy on-chip oscillator, and a triplexed

LCD driver. An internal charge pump generates the neg-

ative supply needed to power the integrated input buffer

for single-supply operation. The ADC is configurable for

either a ±2V or ±200mV input range and outputs its con-

version results to an LCD and/or to a microcontroller

(µC). µC communication is facilitated through an

SPITM-/QSPITM-/MICROWIRETM-compatible serial inter-

face. The MAX1492 is a 3.5-digit (±1999 count) device,

and the MAX1494 is a 4.5-digit (±19,999 count) device.

The MAX1492/MAX1494 do not require external-preci-

sion integrating capacitors, autozero capacitors, crystal

oscillators, charge pumps, or other circuitry required

with dual-slope ADCs (commonly used in panel meter

circuits).

These devices also feature on-chip buffers for the dif-

ferential signal and reference inputs, allowing direct

interface with high-impedance signal sources. In addi-

tion, they use continuous internal-offset calibration and

offer >100dB simultaneous rejection of 50Hz and 60Hz

line noise. Other features include data hold and peak

hold, overrange and underrange detection, and a low-

battery monitor.

The MAX1494 comes in a 32-pin, 7mm x 7mm TQFP

package, and the MAX1492 comes in 28-pin SSOP and

28-pin PDIP packages. All devices in this family operate

over the 0°C to +70°C commercial temperature range.

Applications

Digital Panel Meters

Hand-Held Meters

Digital Voltmeters

Digital Multimeters

Features

o High Resolution

MAX1494: 4.5 Digits (±19,999 Count)

MAX1492: 3.5 Digits (±1999 Count)

o Sigma-Delta ADC Architecture

No Integrating Capacitors Required

No Autozeroing Capacitors Required

>100dB of Simultaneous 50Hz and 60Hz

Rejection

o Operate from a Single 2.7V or 5.25V Supply

o Selectable Input Range of ±200mV or ±2V

o Selectable Voltage Reference: Internal 2.048V

or External

o Internal High-Accuracy Oscillator Needs No

External Components

o Automatic Offset Calibration

o Low Power

Maximum 960µA Operating Current

Maximum 400µA Shutdown Current

o Small 32-Pin 7mm x 7mm TQFP Package

(4.5 Digits), 28-Pin SSOP Package (3.5 Digits)

o Triplexed LCD Driver

o SPI-/QSPI-/MICROWIRE-Compatible Serial

Interface

o Evaluation Kit Available (Order MAX1494EVKIT)

MAX1492/MAX1494

3.5- and 4.5-Digit, Single-Chip ADCs

with LCD Drivers

________________________________________________________________ Maxim Integrated Products

1

Ordering Information

19-2959; Rev 3; 5/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

EVALUATION KIT

AVAILABLE

PART

TEMP

RANGE

PIN-

PACKAGE

RESOLUTION

(DIGITS)

MAX1492CAI

0

°C to +70°C 28 SSOP

3.5

MAX1492CNI

0

°C to +70°C 28 PDIP

3.5

MAX1494CCJ

0

°C to +70°C 32 TQFP

4.5

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

Pin Configurations appear at end of data sheet.

MAX1492/MAX1494

3.5- and 4.5-Digit, Single-Chip ADCs

with LCD Drivers

2

_______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

AV

DD

to GND............................................................-0.3V to +6V

DV

DD

to GND ...........................................................-0.3V to +6V

AIN+, AIN- to GND ................................V

NEG

to +(AV

DD

+ 0.3V)

REF+, REF- to GND...............................V

NEG

to +(AV

DD

+ 0.3V)

LOWBATT to GND ...................................-0.3V to (AV

DD

+ 0.3V)

CLK, EOC, CS, DIN, SCLK, DOUT to

GND .....................................................-0.3V to (DV

DD

+ 0.3V)

SEG_ and BP_ to GND ............................-0.3V to (DV

DD

+ 0.3V)

V

NEG

to GND ...........................................-2.6V to (AV

DD

+ 0.3V)

V

DISP

to GND ...........................................-0.3V to (DV

DD

+ 0.3V)

Maximum Current into Any Pin ...........................................50mA

Continuous Power Dissipation (T

A

= +70°C)

28-Pin SSOP (derate 9.5mW/°C above +70°C) ...........762mW

28-Pin PDIP (derate 14.3mW/°C above +70°C)......1142.9mW

32-Pin TQFP (derate 20.7mW/°C above +70°C).....1652.9mW

Operating Temperature Range...............................0°C to +70°C

Junction Temperature ......................................................+150°C

Storage Temperature Range .............................-60°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

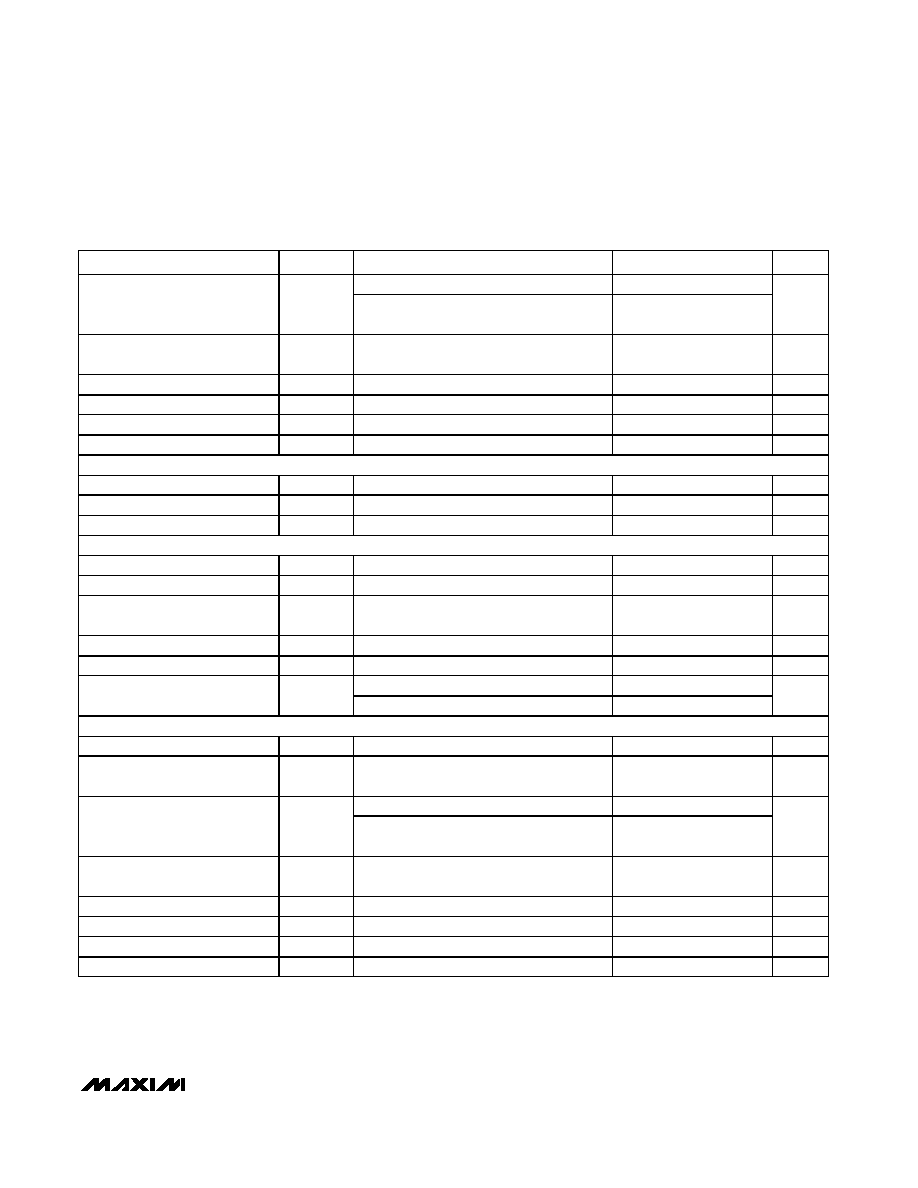

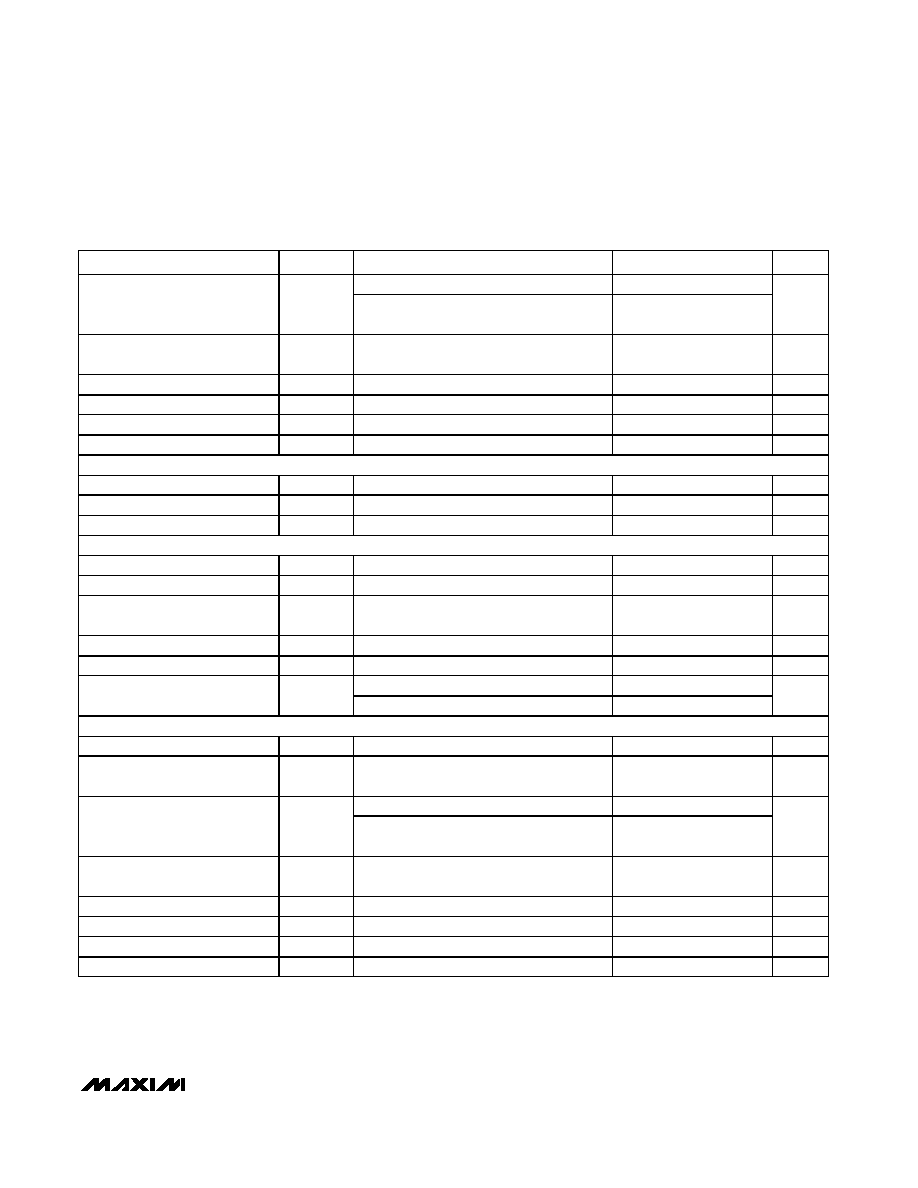

ELECTRICAL CHARACTERISTICS

(AV

DD

= DV

DD

= +2.7V to +5.25V, GND = 0, V

REF+

- V

REF-

= 2.048V (external reference). Internal clock mode, unless otherwise noted.

All specifications are at T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DC ACCURACY

MAX1494

-19,999

+19,999

Noise-Free Resolution

MAX1492

-1999

+1999

Count

2.000V range

±1

Integral Nonlinearity (Note 1)

INL

200mV range

±1

Count

Range Change Accuracy

(V

AIN+

- V

AIN-

= 0.100V) on 200mV range /

(V

AIN+

- V

AIN-

= 0.100V) on 2.0V range

10:1

Ratio

Rollover Error (See the Definitions

Section)

V

AIN+

- V

AIN-

= full scale,

V

AIN-

- V

AIN+

= full scale

±1

Count

Output Noise

10

µV

P-P

Offset Error (Zero Input Reading)

Offset

V

IN

= 0 (Note 2)

-0

0

Reading

Gain Error

(Note 3)

-0.5

+0.5

%FSR

Offset Drift (Zero-Reading Drift)

V

IN

= 0 (Note 4)

0.1

µV/

°C

Gain Drift

±1

ppm/

°C

INPUT CONVERSION RATE

External Clock Frequency

4.915

MHz

External-Clock Duty Cycle

40

60

%

Internal clock

5

Conversion Rate

External clock, f

CLK

= 4.915MHz

5

Hz

ANALOG INPUTS (AIN+, AIN-, bypass to GND with 0.1µF or greater capacitors)

RANGE bit = 0, ±2V

-2.0

+2.0

AIN Input-Voltage Range

(Note 5)

RANGE bit = 1, ±200mV

-0.2

+0.2

V

AIN Absolute Input Voltage to

GND

-2.2

+2.2

V

MAX1492/MAX1494

3.5- and 4.5-Digit, Single-Chip ADCs

with LCD Drivers

_______________________________________________________________________________________

3

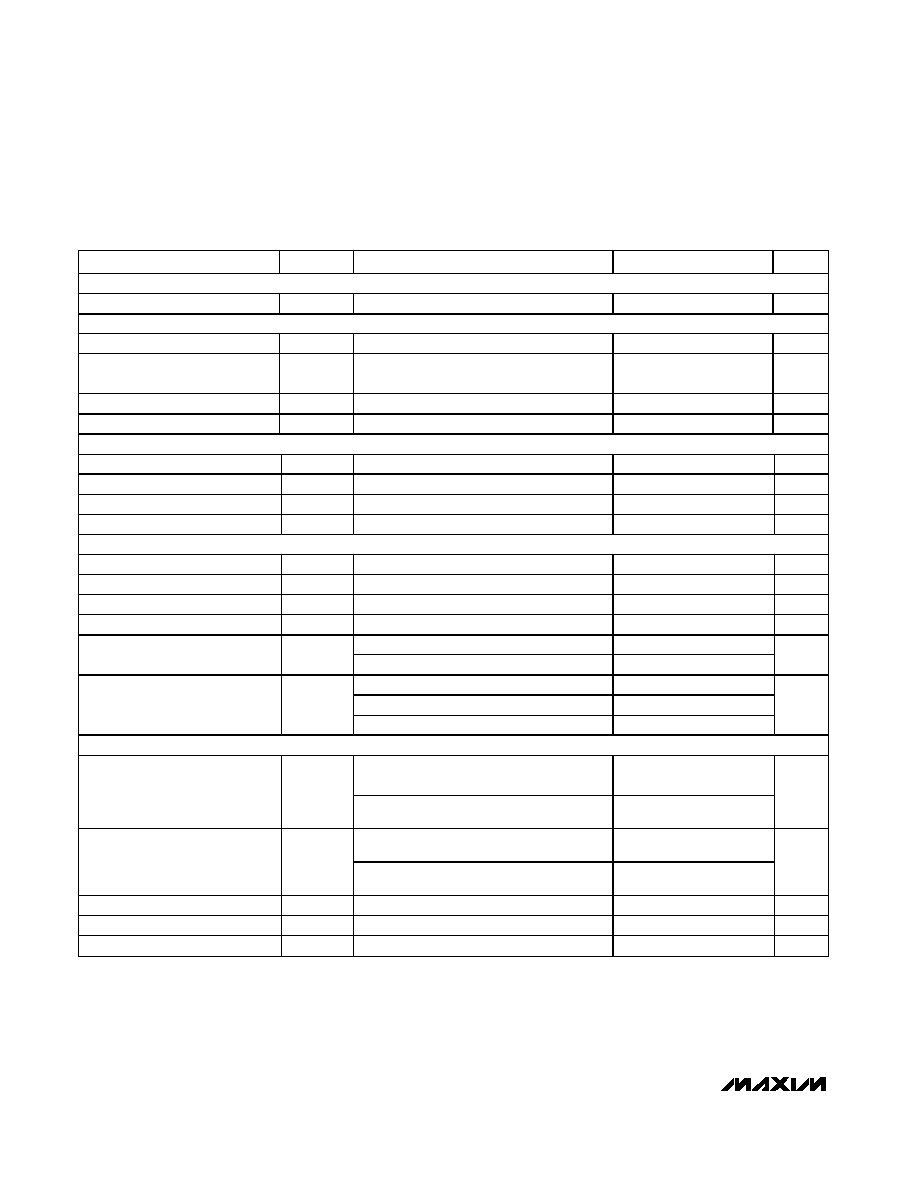

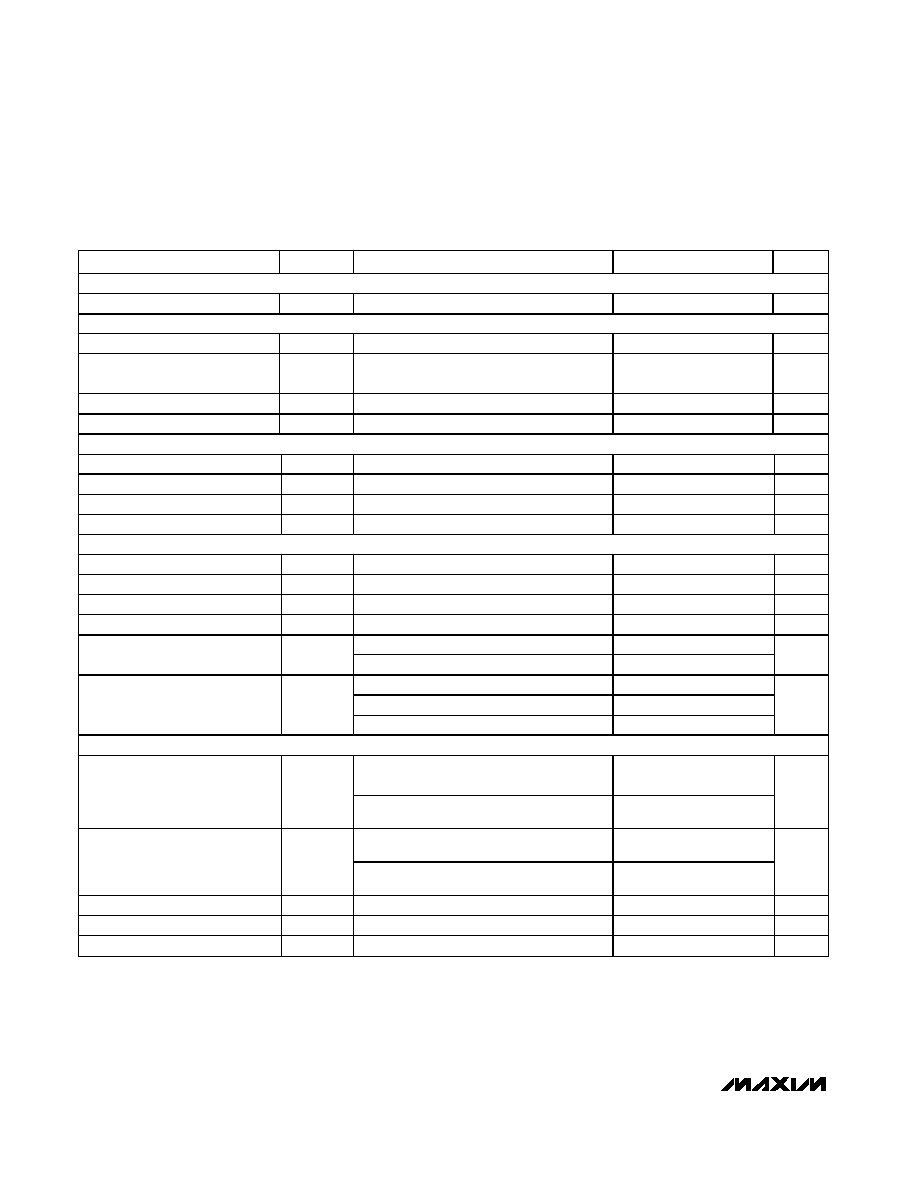

ELECTRICAL CHARACTERISTICS (continued)

(AV

DD

= DV

DD

= +2.7V to +5.25V, GND = 0, V

REF+

- V

REF-

= 2.048V (external reference). Internal clock mode, unless otherwise noted.

All specifications are at T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Internal clock mode, 50Hz and 60Hz ±2%

100

Normal-Mode 50Hz and 60Hz

Rejection (Simultaneously)

External clock mode, 50Hz and 60Hz ±2%,

f

CLK

= 4.915MHz

120

dB

Common-Mode 50Hz and 60Hz

Rejection (Simultaneously)

CMR

For 50Hz and 60Hz ±2%, R

SOURCE

< 10k

150

dB

Common-Mode Rejection

CMR

At DC

100

dB

Input Leakage Current

10

nA

Input Capacitance

10

pF

Dynamic Input Current

(Note 6)

-20

+20

nA

LOW-BATTERY VOLTAGE MONITOR (LOWBATT)

LOWBATT TripThreshold

2.048

V

LOWBATT Leakage Current

10

pA

Hysteresis

20

mV

INTERNAL REFERENCE (INTREF BIT = 1, REF- = GND, bypass REF+ to GND with a 4.7µF capacitor)

REF Output Voltage

V

REF

AV

DD

= 5V, T

A

= +25

°C

2.007

2.048

2.089

V

REF Output Short-Circuit Current

1

mA

REF Output Temperature

Coefficient

TC

VREF

AV

DD

= 5V

40

ppm/

°C

Load Regulation

I

SOURCE

= 0 to 300µA, I

SINK

= 0 to 30µA

6

mV/µA

Line Regulation

50

µV/V

0.1Hz to 10Hz

25

Noise Voltage

10Hz to 10kHz

400

µV

P-P

EXTERNAL REFERENCE (INTREF BIT = 0, bypass REF+ and REF- to GND with 0.1µF or larger capacitors)

REF Input Voltage

Differential (V

REF+

- V

REF-

)

2.048

V

Absolute REF Input Voltage to

GND

-2.2

+2.2

V

Internal clock mode, 50Hz and 60Hz ±2%

100

Normal-Mode 50Hz and 60Hz

Rejection (Simultaneously)

External clock mode, 50Hz and 60Hz ±2%,

f

CLK

= 4.915MHz

120

dB

Common-Mode 50Hz and 60Hz

Rejection (Simultaneously)

CMR

For 50Hz and 60Hz ±2%, R

SOURCE

< 10k

150

dB

Common-Mode Rejection

CMR

At DC

100

dB

Input Leakage Current

10

nA

Input Capacitance

10

pF

Dynamic Input Current

(Note 6)

-20

+20

nA

MAX1492/MAX1494

3.5- and 4.5-Digit, Single-Chip ADCs

with LCD Drivers

4

_______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

(AV

DD

= DV

DD

= +2.7V to +5.25V, GND = 0, V

REF+

- V

REF-

= 2.048V (external reference). Internal clock mode, unless otherwise noted.

All specifications are at T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CHARGE PUMP (C

NEG

= 0.1µF)

Output Voltage

V

NEG

-2.60

-2.42

-2.30

V

DIGITAL INPUTS (SCLK, DIN,

CS, CLK)

Input Current

I

IN

V

IN

= 0 or DV

DD

-10

+10

µA

Input Low Voltage

V

INL

0.3 x

DV

DD

V

Input High Voltage

V

INH

0.7 x DV

DD

V

Input Hysteresis

V

HYST

DV

DD

= 3.0V

200

mV

DIGITAL OUTPUTS (DOUT,

EOC)

Output Low Voltage

V

OL

I

SINK

= 1mA

0.4

V

Output High Voltage

V

OH

I

SOURCE

= 200µA

0.8 x DV

DD

V

Tri-State Leakage Current

I

L

D

OUT

only

-10

+10

µA

Tri-State Output Capacitance

C

OUT

D

OUT

only

15

pF

POWER SUPPLY

AV

DD

Voltage

AV

DD

2.70

5.25

V

DV

DD

Voltage

DV

DD

2.70

5.25

V

Power-Supply Rejection AV

DD

PSRR

A

(Note 7)

80

dB

Power-Supply Rejection DV

DD

PSRR

D

(Note 7)

100

dB

AV

DD

= 5V

580

660

AV

DD

Current (Notes 8, 9)

I

AVDD

Standby

240

380

µA

DV

DD

= 5V

260

320

DV

DD

= 3.3V

130

180

DV

DD

Current (Notes 8, 9)

I

DVDD

Standby

10

20

µA

LCD DRIVER

MAX1492

1.92 x

DV

DD

RMS Segment On Voltage

MAX1494

1.92 x

(DV

DD

- V

DISP

)

V

MAX1492

1/3 x

DV

DD

RMS Segment Off Voltage

MAX1494

1/3 x

(DV

DD

- V

DISP

)

V

Display Voltage Setup Resistor

R

DISP

MAX1494 only

157.5

k

Display Multiplex Rate

107

Hz

LCD Data-Update Rate

2.5

Hz

MAX1492/MAX1494

3.5- and 4.5-Digit, Single-Chip ADCs

with LCD Drivers

_______________________________________________________________________________________

5

TIMING CHARACTERISTICS (Notes 10, 11 and Figure 13)

(AV

DD

= DV

DD

= 2.7V to +5.25V, GND = 0, T

A

= T

MIN

to T

MAX

, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SCLK Operating Frequency

f

SCLK

0

4.2

MHz

SCLK Pulse-Width High

t

CH

100

ns

SCLK Pulse-Width Low

t

CL

100

ns

DIN to SCLK Setup

t

DS

50

ns

DIN to SCLK Hold

t

DH

0

ns

CS Fall to SCLK Rise Setup

t

CSS

50

ns

SCLK Rise to CS Rise Hold

t

CSH

0

ns

SCLK Fall to DOUT Valid

t

DO

C

LOAD

= 50pF (Figures 18, 19)

120

ns

CS Rise to DOUT Disable

t

TR

C

LOAD

= 50pF (Figures 18, 19)

120

ns

CS Fall to DOUT Enable

t

DV

C

LOAD

= 50pF (Figures 18, 19)

120

ns

Note 1:

Integral nonlinearity is the deviation of the analog value at any code from its theoretical value after nulling the gain error

and offset error.

Note 2:

Offset calibrated. See the OFFSET_CAL1 and OFFSET_CAL2 sections in the On-Chip Registers section.

Note 3:

Offset nulled.

Note 4:

Drift error is eliminated by recalibration at the new temperature.

Note 5:

The input voltage range for the analog inputs is given with respect to the voltage on the negative input of the differential pair.

Note 6:

V

AIN+

or V

AIN-

= -2.2V to +2.2V. V

REF+

or V

REF-

= -2.2V to +2.2V. All input structures are identical. Production tested on

AIN+ and REF+ only.

Note 7:

Measured at DC by changing the power-supply voltage from 2.7V to 5.25V and measuring the effect on the conversion

error with external reference. PSRR at 50Hz and 60Hz exceeds 120dB with filter notches at 50Hz and 60Hz (Figure 2).

Note 8:

CLK and SCLK are idle.

Note 9:

Power-supply currents are measured with all digital inputs at either GND or DV

DD

and with the device in internal clock mode.

Note 10: All input signals are specified with t

RISE

= t

FALL

= 5ns (10% to 90% of DV

DD

) and are timed from a voltage level of 50% of

DV

DD

, unless otherwise noted.

Note 11: See the serial-interface timing diagrams.