ICM108B 1.3 million pixel CMOS sensor

Data Sheet V 1.1 November, 2002

®2000, 2001, 2002 IC Media Corporation & IC Media Technology Corp.

11/22/2002

page 1

COMPANY CONFIDENTIAL

ICM108B 1.3 million pixel

Color CMOS image sensor

Data Sheet

V1.1

November, 2002

IC Media Corporation

545 East Brokaw Road

San Jose, CA 95112, U.S.A.

Phone: (408) 451-8838

Fax: (408) 451-8839

Email: Sales@IC-Media.Com

Web Site:

www.ic-media.com

IC Media Technology Corporation

6F, No. 61, ChowTze Street., NeiHu District

Taipei, Taiwan, R.O.C.

Phone: 886-2-2657-7898

Fax: 886-2-2657-8751

Email: Ap.Sales@IC-Media.Com.tw

Web Site: www.ic-media.com.tw

Important notice: This document contains information of a new product. IC

Media Corp. reserves the right to make any changes without further notice to

any product herein to improve design, function or quality and reliability. No

responsibility is assumed by IC Media Corp. for its use, nor for any

infringements of patents of third parties that may result from its use.

ICM108B 1.3 million pixel CMOS sensor

Data Sheet V 1.1 November, 2002

®2000, 2001, 2002 IC Media Corporation & IC Media Technology Corp.

11/22/2002

page 2

COMPANY CONFIDENTIAL

Features

Ę 1.3 mega pixels (1280x1024) format

Ę Support sub-sampling at quarter (1/4), and quarter-quarter (1/16) mega pixel resolutions for higher

video frame rate

Ę Progressive readout

Ę Output data format: 10-bit raw data

Ę Input interface: SIF

Ę Electronic exposure control

Ę On-chip 11-bit ADC

Ę On-chip PLL

Ę Correlated double sampling

Ę Video mode and DSC mode

Ę Dead pixel removal

Ę Flash control

Ę Power down mode

Ę Automatic optical black compensation

Ę Horizontal and vertical images

Ę Single 3.3V power supply

General Description

ICM-108B is a single-chip digital color-imaging device. It incorporates a 1280x1024 sensor array capable

of operating at up to 30 frames per second and sub-sampled quarter (1/4) and quarter-quarter (1/16) mega

pixel resolutions, operating at higher frame rate in progressive manner. Each pixel is covered by a color

filter, which formed a so-called Bayer pattern. Correlated double sampling is performed by the internal

ADC and timing circuitry. The gains for raw data can be adjusted separately for the 4 Bayer pattern pixels.

The output format is 10-bit raw data that can be fed to other DSP, color processing, or compression chips.

Applications

Ę Digital camcorder

Ę Digital still camera

Ę Video phone

Ę Video conferencing

Ę Video mail

Ę Video cellular phone

Ę PC camera

Ę Security system

Ę Visual toy

Ę Industrial image capture/analysis

Ę Environment monitor system

ICM108B 1.3 million pixel CMOS sensor

Data Sheet V 1.1 November, 2002

®2000, 2001, 2002 IC Media Corporation & IC Media Technology Corp.

11/22/2002

page 3

COMPANY CONFIDENTIAL

Key Parameters

Ę Number of pixels: 1280x1024

Ę Number of physical pixels: 1,333,860, (1290x1034)

Ę Frame rate: 30/15/10/5/4/3/2/1 fps

Ę Sub-sampling quarter (1/4) and quarter-quarter (1/16) mega pixel resolutions for higher frame rate

Ę Pixel size: 6 Ąm x 6 Ąm

Ę Sensor area: 7.68 mm x 6.144 mm

Ę Input clock: 6 MHz crystal, or external clock source of 6, 12, 24, 48, or 96 MHz through PLL or

bypass PLL

Ę Main clock frequency: 48 MHz; on-chip 11 bit ADC clock: 96MHz (2x of main clock frequency),

for 30 fps operation.

Ę Mode exposure time: 31.25 Ąs (@ 30 fps, 1 line). Maximum exposure time ~ 60 s @ X1 mode

(1 fps), 65535 lines

Ę RGB gain: 1/256 to 64 for individual Bayer pattern pixels depending on register setting.

Ę Sensitivity: 1.0 V/lux-sec (5200 K light source, 650 nm IR cutoff filter)

Ę Quantum Efficiency: 38 % (555 nm)

Ę Dynamic Range: 55 dB (relative to noise floor = temporal noise + quantization noise); 45 dB

(relative to total noise)

Ę Fill Factor: 36%

Ę S/N Ratio (temporal noise): 45 dB @ 75% full signal level

Ę S/N Ratio (total noise): 40 dB @ 75% full signal level

Ę Sensitive to infrared illumination source

Ę Power supply: 3.3V

Ę Power requirement: <100mA (@30fps) and <60mA (@15fps)

Ę Standby mode power: < 50uA

Ę Package: Plastic LCC48

ICM108B 1.3 million pixel CMOS sensor

Data Sheet V 1.1 November, 2002

®2000, 2001, 2002 IC Media Corporation & IC Media Technology Corp.

11/22/2002

page 4

COMPANY CONFIDENTIAL

1. Preliminary Pin Assignment

Pin #

Name

Class*

Function

14

CLKSEL

D, I, N

Clock source selection

0: clocks pass PLL, use XIN (pin 12)

1: bypass PLL, use CLKIN (pin 11)

11

CLKIN

D, I, N

External clock source; bypass PLL

12

XIN

A, I

Crystal oscillator in, or external clock in; if external

clocks used, leave Xout (pin 13) unconnected

13

XOUT

A, O

Crystal oscillator out

33

PCLK

D, O

Pixel clock output

35

OEN

D, I, N

Output enable. 0: enable, 1: disable

31

SIF ID

D, I, N

LSB of SIF slave address

32

MSSEL

D, I, U

SIF master/slave selection. 0: slave, 1: master

2

SCL

D, I/O

SIF clock

1

SDA

D, I/O

SIF data

10

POWERDN

D, I, N

Power down control, 0: power down, 1: active

17

RSET

A, I

Resistor to ground = 25 K

@ 48 MHz main clock,

(or 50K

@ 24 MHz main clock)

8

RSTN

D, I, U

Chip reset, active low

48

DOUT[10]

D, I/O

Data output bit 10

47

DOUT[9]

D, I/O

Data output bit 9

46

DOUT[8]

D, I/O

Data output bit 8

45

DOUT[7]

D, O

Data output bit 7

44

DOUT[6]

D, I/O

Data output bit 6; if pulled up/down, the initial value

of TIMING_CONTROL_LOW[2] (VSYNC polarity)

is 1/0

43

DOUT[5]

D, I/O

Data output bit 5; if pulled up/down, the initial value

of TIMING_CONTROL_LOW[1] (HSYNC polarity)

is 1/0

40

DOUT[4]

D, I/O

Data output bit 4; if pulled up/down, the initial value

of AD_IDL[3] (Sub ID) is 1/0

39

DOUT[3]

D, I/O

Data output bit 3; if pulled up/down, the initial value

of AD_IDL[2] (Sub ID) is 1/0

38

DOUT[2]

D, I/O

Data output bit 2; if pulled up/down, the initial value

of AD_IDL[1] (Sub ID) is 1/0

37

DOUT[1]

D, I/O

Data output bit 1; if pulled up/down, the initial value

of AD_IDL[0] (Sub ID) is 1/0

36

DOUT[0]

D, I/O

Data output bit 0; if pulled up/down, the synchron-

ization mode is in master/slave mode which requires

HSYNC and VSYNC operating in output/input mode

3

HSYNC

D, I/O

Horizontal sync signal

5

VSYNC

D, I/O

Vertical sync signal

34

FLASH

D, O

Flash light control

15

RAMP

A, O

Analog ramp output

30,7

VDDA

P

Sensor analog power

29,9

GNDA

P

Sensor analog ground

19

VDDD

P

Sensor digital power

18

GNDD

P

Sensor digital ground

41,4

VDDK

P

Digital power

42,6

GNDK

P

Digital ground

ICM108B 1.3 million pixel CMOS sensor

Data Sheet V 1.1 November, 2002

®2000, 2001, 2002 IC Media Corporation & IC Media Technology Corp.

11/22/2002

page 5

COMPANY CONFIDENTIAL

Class Code: A Ł Analog signal, D Ł Digital signal, I Ł Input, O Ł Output, P Ł Power or ground, U Ł Internal

pull-up, N Ł Internal pull-down

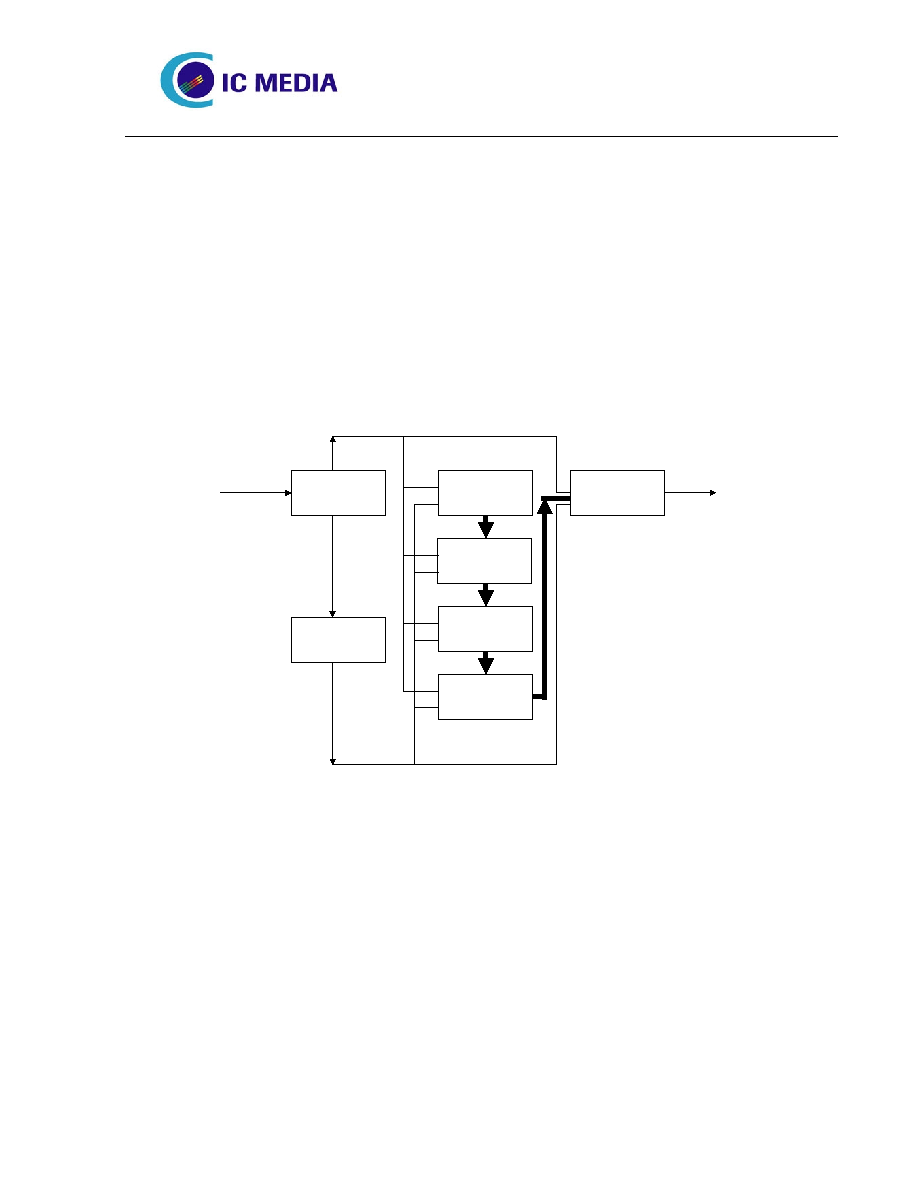

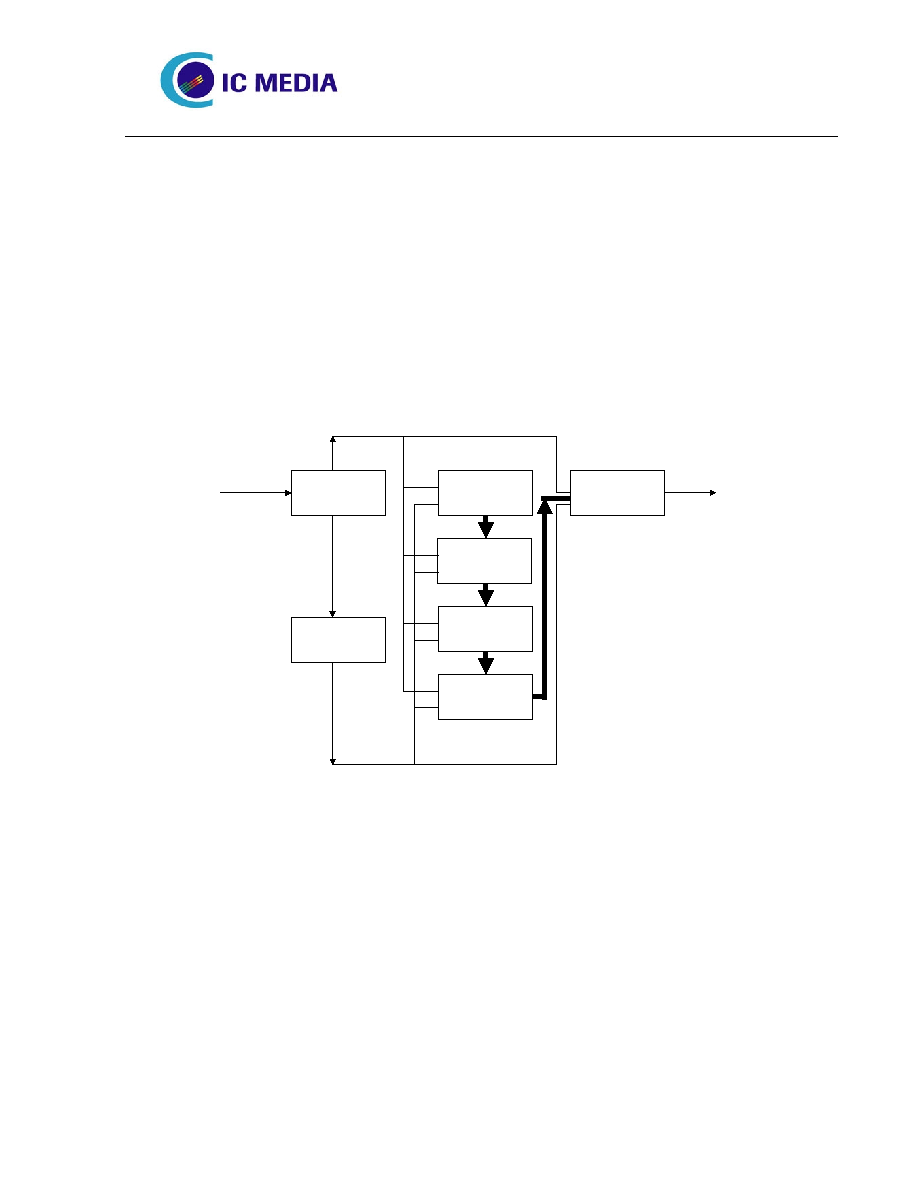

2. Functional Description

ICM-108B is a single-chip digital color imaging device. It includes a 1280x1024 sensor array, 1280

column-level ADC, and correlated double sampling circuitry. All the programmable parameters are set by

writing into the SIF interface which can address the register file consisting of 8-bit registers. The output

format is 10-bit raw data, together with horizontal and vertical sync signals.

SIF

Interface

Sensor Array

1280 x 1024

Column-Level

ADC

Timing & Function

Control

Correlated

Double

Sampling

Individual

RGB gain control

RGB Bayer Pattern

Output Control

Figure 1. Block diagram

2.1 Image Array

The image array consists of 1280x1024 pixels. Each pixel has a light sensitive photo diode and a set of

control transistors. At the beginning of the cycle, a row of pixels is pre-charged to its maximum value.

Then the row is exposed to light for several lines worth of time and sampled by the ADC. A "Correlated

Double Sampling (CDS)" process is performed with subtracting the reset value (sampled right before

sampling the signal) from the signal value. The purpose of CDS is to eliminate the point-wise fixed pattern

noise (FPN). The output of CDS is approximately proportional to the amount of received light, ranging

from 0 to 1023.