ii

This document contains proprietary information of LSI Logic Corporation. The

information contained herein is not to be used by or disclosed to third parties

without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices,

or systems. Use of any LSI Logic product in such applications without written

consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000125-02, Fourth Edition (June 2002)

This document describes the LSI Logic LSI53C040 Enclosure Services

Processor and will remain the official reference source for all revisions/releases

of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein

at any time without notice. LSI Logic does not assume any responsibility or

liability arising out of the application or use of any product described herein,

except as expressly agreed to in writing by LSI Logic; nor does the purchase or

use of a product from LSI Logic convey a license under any patent rights,

copyrights, trademark rights, or any other of the intellectual property rights of

LSI Logic or third parties.

Copyright © 19982002 by LSI Logic Corporation. All rights reserved.

TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, LVDlink, and TolerANT are trademarks or registered

trademarks of LSI Logic Corporation. MCS is a registered trademark of Intel

Corporation. All other brand and product names may be trademarks of their

respective companies.

DB

To receive product literature, visit us at http://www.lsilogic.com.

For a current list of our distributors, sales offices, and design resource

centers, view our web page located at

http://www.lsilogic.com/contacts/na_salesoffices.html

Preface

iii

Preface

This technical manual provides reference information on the LSI53C040

Enclosure Services Processor. It contains a complete functional

description for the product and includes complete physical and electrical

specifications for it.

Audience

This manual assumes some prior knowledge of current and proposed

SCSI, Inter-Integrated Circuit, and SFF-8067 standards, including the

SAF-TE and SES standards for parallel SCSI devices, as well as a

detailed understanding of serial data communication. It is intended for

system designers who are using this device to manage SCSI or Fibre

Channel peripheral device enclosures.

Organization

This document has the following chapters and appendix:

·

Chapter 1, Introduction

, contains general information about the

LSI53C040, including an overview of its features and functions.

·

Chapter 2, Functional Description

, describes the main functions of

the chip in more detail, including the major interfaces.

·

Chapter 3, Signal Descriptions

, contains the pin diagrams and

descriptions of each signal.

·

Chapter 4, SCSI and DMA Registers

·

Chapter 5, SFF-8067 Registers

·

Chapter 6, Two-Wire Serial Registers

·

Chapter 7, Miscellaneous Registers

·

Chapter 8, System Registers

iv

Preface

·

Chapter 9, Electrical Characteristics

, contains the operating

conditions and AC timings for the chip and mechanical drawings.

·

Appendix A, Register Summary

Related Publications

For background information, please contact:

ANSI

11 West 42nd Street

New York, NY 10036

(212) 642-4900

Ask for document number X3.131-199X (SCSI-2)

Global Engineering Documents

15 Inverness Way East

Englewood, CO 80112

(800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740

Ask for document number X3.131-1994 (SCSI-2); X3.253 (SCSI-3

Parallel Interface); or NCITS 305-199x (SCSI-3 Enclosure Services

(SES) Specification working draft)

SCSI Accessed Fault-Tolerant Enclosures (SAF-TE) Specification

This document can be downloaded from www.safte.org

LSI Logic World Wide Web Home Page

www.lsilogic.com

SFF-8067 Specification

ENDL Fax Access

(408) 741-1600 (call from a FAX machine)

Inter-Integrated Circuit Bus Specification

For general information about the Inter-Integrated Circuit bus, contact

Philips Semiconductors at www.semiconductors.philips.com

Conventions Used in This Manual

The first time a word or phrase is defined in this manual, it is italicized.

Preface

v

The word assert means to drive a signal true or active. The word

deassert means to drive a signal false or inactive. Signals that are active

LOW end in a "/."

Hexadecimal numbers are indicated by the prefix "0x" --for example,

0x32CF. Binary numbers are indicated by the prefix "0b" --for example,

0b0011.0010.1100.1111.

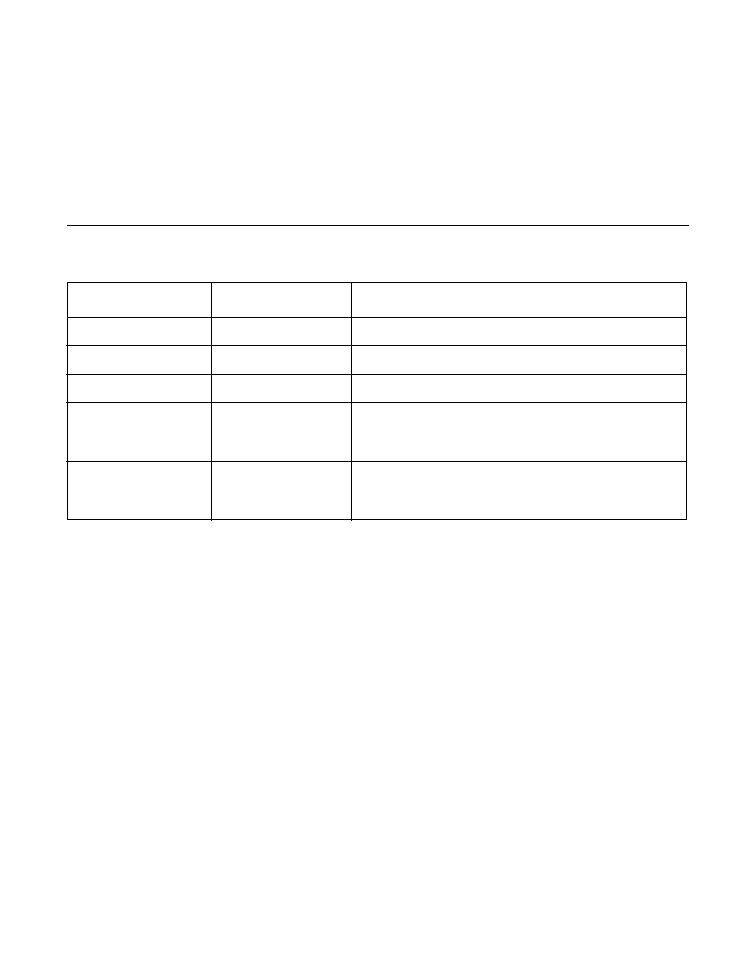

Revision Record

Page No.

Date

Remarks

all

April 1998

Initial Release

all

December 1998

Preliminary, Version 2.0

all

February 2000

Version 2.5

all

April 2001

Version 2.6. All product names changed from SYM to

LSI. Updated DC electrical specifications and test

conditions.

Front Cover, page ii,

pages 9-25 and 9-26

June 2002

Version 2.7. Replaced PZ package mechanical

drawing with P3 package mechanical drawing, pages

9-25 and 9-26.