Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1

LTC1473

Dual PowerPath

TM

Switch Driver

s

Power Path Management for Systems with Multiple

DC Sources

s

All N-Channel Switching to Reduce Power Losses and

System Cost

s

Switches and Isolates Sources Up to 30V

s

Adaptive High Voltage Step-Up Regulator for N-Channel

Gate Drive

s

Capacitor Inrush and Short-Circuit Current Limited

s

User-Programmable Timer to Limit Switch Dissipation

s

Small Footprint: 16-Pin Narrow SSOP

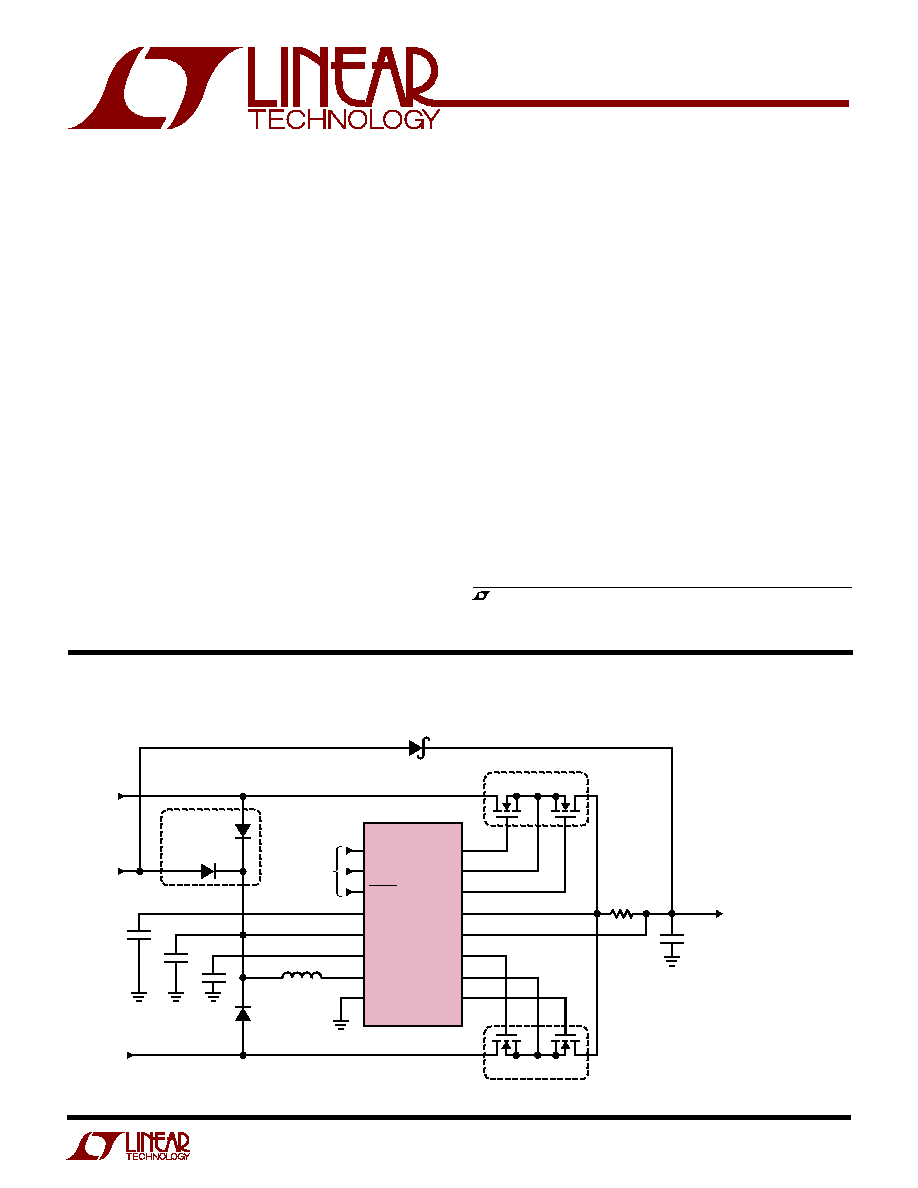

The LTC

®

1473 provides a power management solution for

single and dual battery notebook computers and other

portable equipment. The LTC1473 drives two sets of back-

to-back N-channel MOSFET switches to route power to the

input of the main system switching regulator. An internal

boost regulator provides the voltage to fully enhance the

logic level N-channel MOSFET switches.

The LTC1473 senses current to limit surge currents both

into and out of the batteries and the system supply

capacitor during switch-over transitions or during fault

conditions. A user-programmable timer monitors the time

the MOSFET switches are in current limit and latches them

off when the programmed time is exceeded.

A unique "2-diode mode" logic ensures system start-up

regardless of which input receives power first.

s

Notebook Computers

s

Portable Instruments

s

Handi-Terminals

s

Portable Medical Equipment

s

Portable Industrial Control Equipment

PowerPath is a trademark of Linear Technology Corporation.

, LTC and LT are registered trademarks of Linear Technology Corporation.

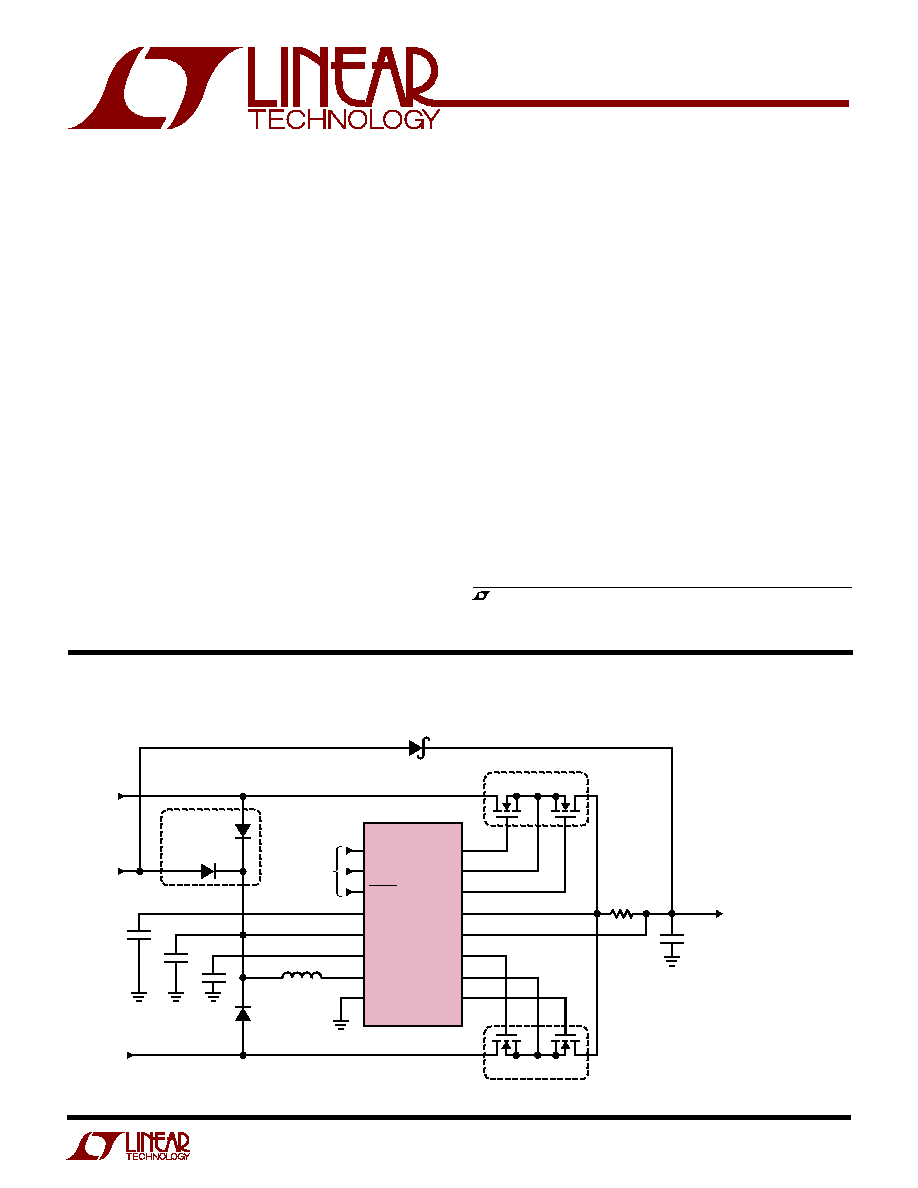

IN1

IN2

DIODE

TIMER

V

+

V

GG

SW

GND

GA1

SAB1

GB1

SENSE

+

SENSE

GA2

SAB2

GB2

LTC1473

C

OUT

R

SENSE

0.04

1

µ

F

1

µ

F

MMBD914LTI

1mH*

Si9926DY

MMBD2838LTI

1473 TA01

BAT1

DCIN

BAT2

INPUT OF SYSTEM

HIGH EFFICIENCY DC/DC

SWITCHING REGULATOR

(LTC1735, ETC)

FROM POWER

MANAGEMENT

µ

P

C

TIMER

4700pF

MBRD340

Si9926DY

*COILCRAFT 1812LS-105XKBC

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

FEATURES

DESCRIPTIO

U

APPLICATIO S

U

TYPICAL APPLICATIO

N

U

2

LTC1473

ABSOLUTE

M

AXI

M

U

M

RATINGS

W

W

W

U

DCIN, BAT1, BAT2 Supply Voltage .............. 0.3 to 32V

SENSE

+

, SENSE

, V

+

.................................. 0.3 to 32V

GA1, GB1, GA2, GB2 ................................... 0.3 to 42V

SAB1, SAB2 ................................................. 0.3 to 32V

SW, V

GG

...................................................... 0.3 to 42V

IN1, IN2, DIODE ........................................ 0.3V to 7.5V

Junction Temperature (Note 2) ............................. 125

°

C

Operating Temperature Range

Commercial ............................................. 0

°

C to 70

°

C

Industrial ........................................... 40

°

C to 85

°

C

Storage Temperature Range ................. 65

°

C to 150

°

C

Lead Temperature (Soldering, 10 sec).................. 300

°

C

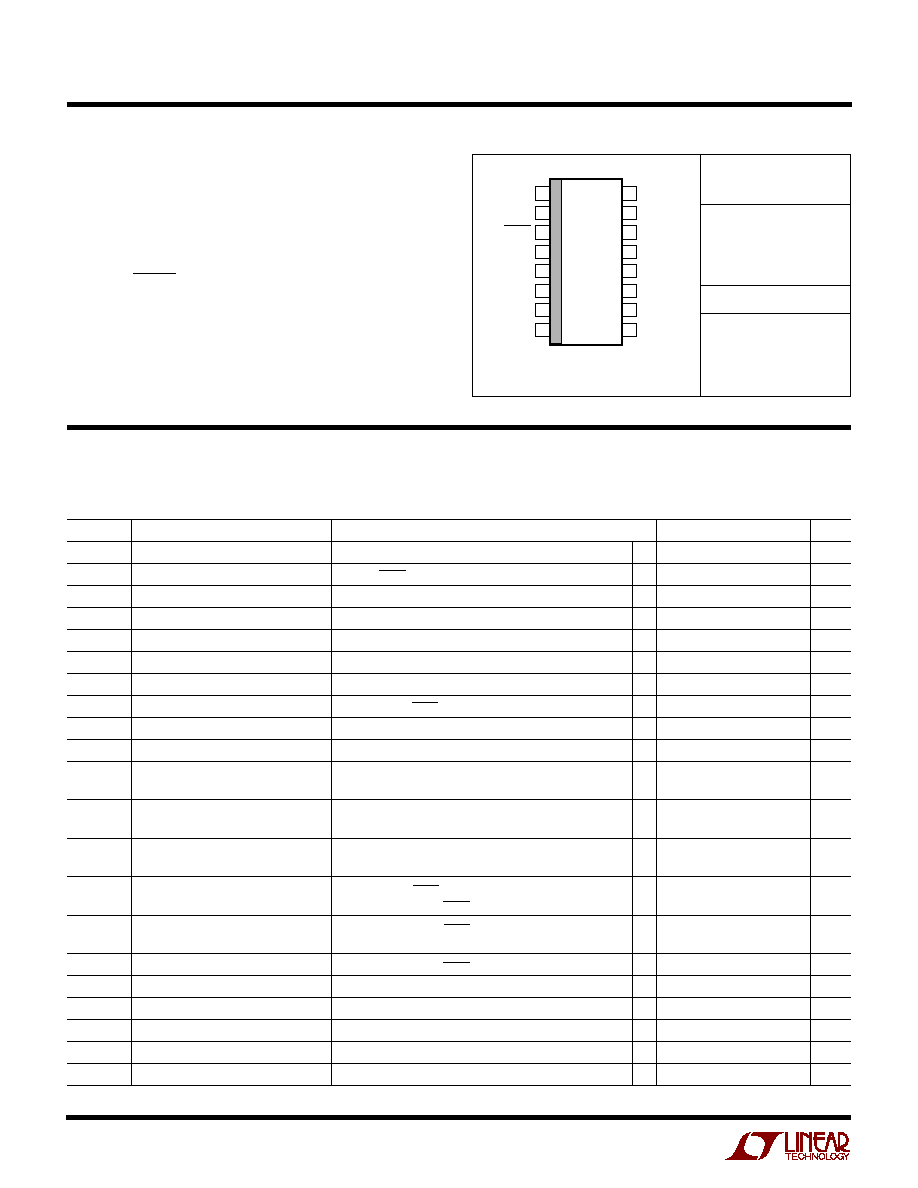

ORDER PART

NUMBER

PACKAGE/ORDER I

N

FOR

M

ATIO

N

W

U

U

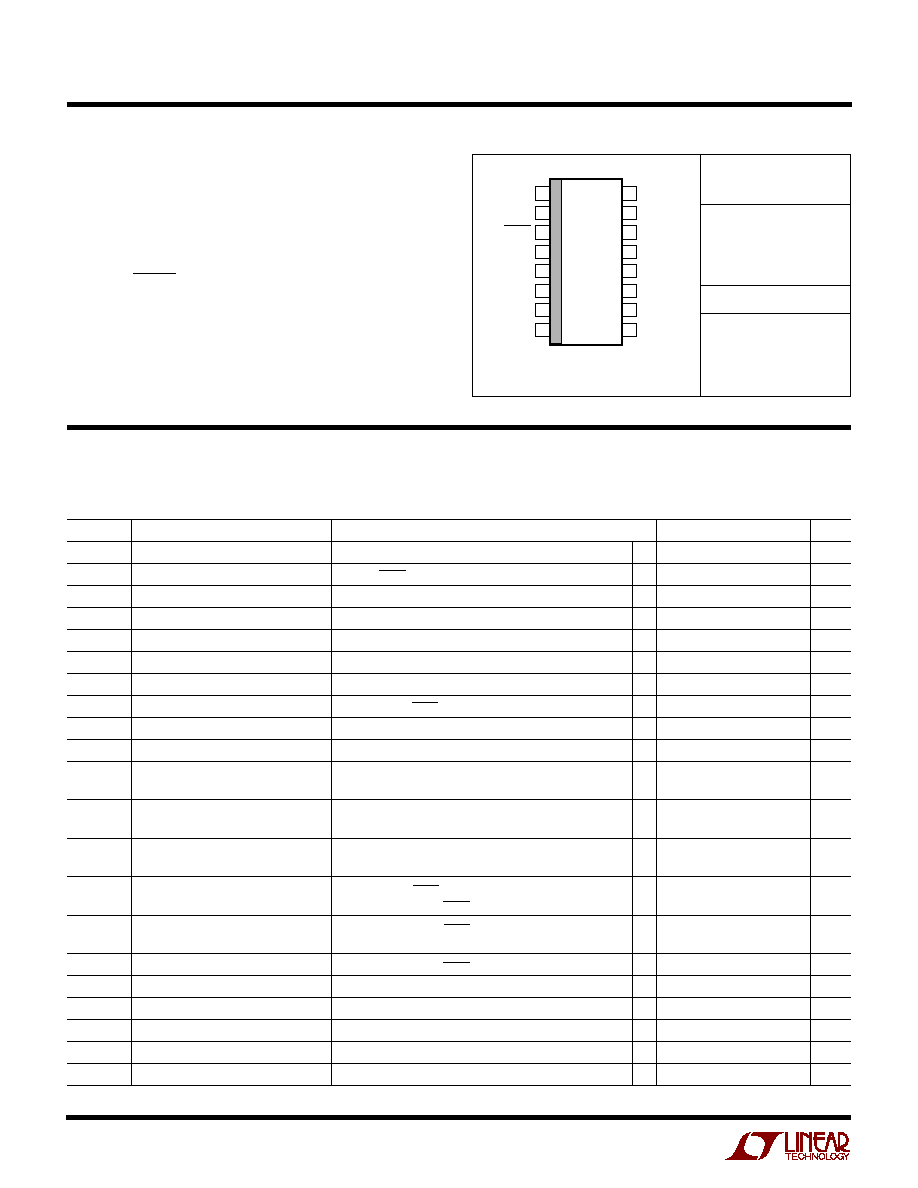

LTC1473CGN

LTC1473IGN

TOP VIEW

GN PACKAGE

16-LEAD NARROW PLASTIC SSOP

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

IN1

IN2

DIODE

TIMER

V

+

V

GG

SW

GND

GA1

SAB1

GB1

SENSE

+

SENSE

GA2

SAB2

GB2

T

JMAX

= 125

°

C,

JA

= 150

°

C/ W

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

+

Supply Operating Range

4.75

30

V

I

S

Supply Current

V

IN1

= V

DIODE

= 5V, V

IN2

= 0V, V

SENSE

+

= V

SENSE

= 20V

q

100

200

µ

A

V

GS

V

GS

Gate Supply Voltage

V

GS

= V

GG

V

+

q

7.5

8.5

9.5

V

V

+

UVLO

V

+

Undervoltage Lockout Threshold

V

+

Ramping Down

2.7

3.1

3.5

V

V

+

UVLOHYS

V

+

Undervoltage Lockout Hysteresis

0.75

1

1.25

V

V

HIDIGIN

Digital Input Logic High

q

2

1.6

V

V

LODIGIN

Digital Input Logic Low

q

1.5

0.8

V

I

IN

Input Current

V

IN1

= V

IN2

= V

DIODE

= 5V

±

1

µ

A

V

GS(ON)

Gate-to-Source ON Voltage

I

GA1

= I

GA2

= I

GB1

= I

GB2

= 1

µ

A, V

SAB1

= V

SAB2

= 20V

q

5.0

5.7

7.0

V

V

GS(OFF)

Gate-to-Source OFF Voltage

I

GA1

= I

GA2

= I

GB1

= I

GB2

= 100

µ

A, V

SAB1

= V

SAB2

= 20V

q

0

0.4

V

I

BSENSE

+

SENSE

+

Input Bias Current

V

SENSE

+

= V

SENSE

= 20V

q

2

4.5

6.5

µ

A

V

SENSE

+

= V

SENSE

= 0V (Note 3)

q

300

160

100

µ

A

I

BSENSE

SENSE

Input Bias Current

V

SENSE

+

= V

SENSE

= 20V

q

2

4.5

6.5

µ

A

V

SENSE

+

= V

SENSE

= 0V (Note 3)

q

300

160

100

µ

A

V

SENSE

Inrush Current Limit Sense Voltage

V

SENSE

= 20V (V

SENSE

+

V

SENSE

)

q

0.15

0.20

0.25

V

V

SENSE

= 0V (V

SENSE

+

V

SENSE

)

0.10

0.20

0.30

V

I

PDSAB

SAB1, SAB2 Pull-Down Current

V

IN1

= V

IN2

= V

DIODE

= 0.8V

5

20

30

µ

A

V

IN1

= V

IN2

= 0.8V, V

DIODE

= 2V

30

200

300

µ

A

I

TIMER

Timer Source Current

V

IN1

= 0.8V, V

IN2

= V

DIODE

= 2V, V

TIMER

= 0V,

q

3

5.5

8

µ

A

V

SENSE

+

V

SENSE

= 300mV

V

TIMER

Timer Latch Threshold Voltage

V

IN1

= 0.8V, V

IN2

= V

DIODE

= 2V

q

1.1

1.2

1.3

V

t

ON

Gate Drive Rise Time

C

GS

= 1000pF, V

SAB1

= V

SAB2

= 0V (Note 4)

33

µ

s

t

OFF

Gate Drive Fall Time

C

GS

= 1000pF, V

SAB1

= V

SAB2

= 20V (Note 4)

2

µ

s

t

D1

Gate Drive Turn-On Delay

C

GS

= 1000pF, V

SAB1

= V

SAB2

= 0V (Note 4)

22

µ

s

t

D2

Gate Drive Turn-Off Delay

C

GS

= 1000pF, V

SAB1

= V

SAB2

= 20V (Note 4)

1

µ

s

f

OVGG

V

GG

Regulator Operating Frequency

30

kHz

ELECTRICAL CHARACTERISTICS

Test circuit, V

+

= 20V, unless otherwise specified.

Consult factory for Military grade parts.

(Note 1)

The

q

denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25

°

C.

GN PART MARKING

1473

1473I

3

LTC1473

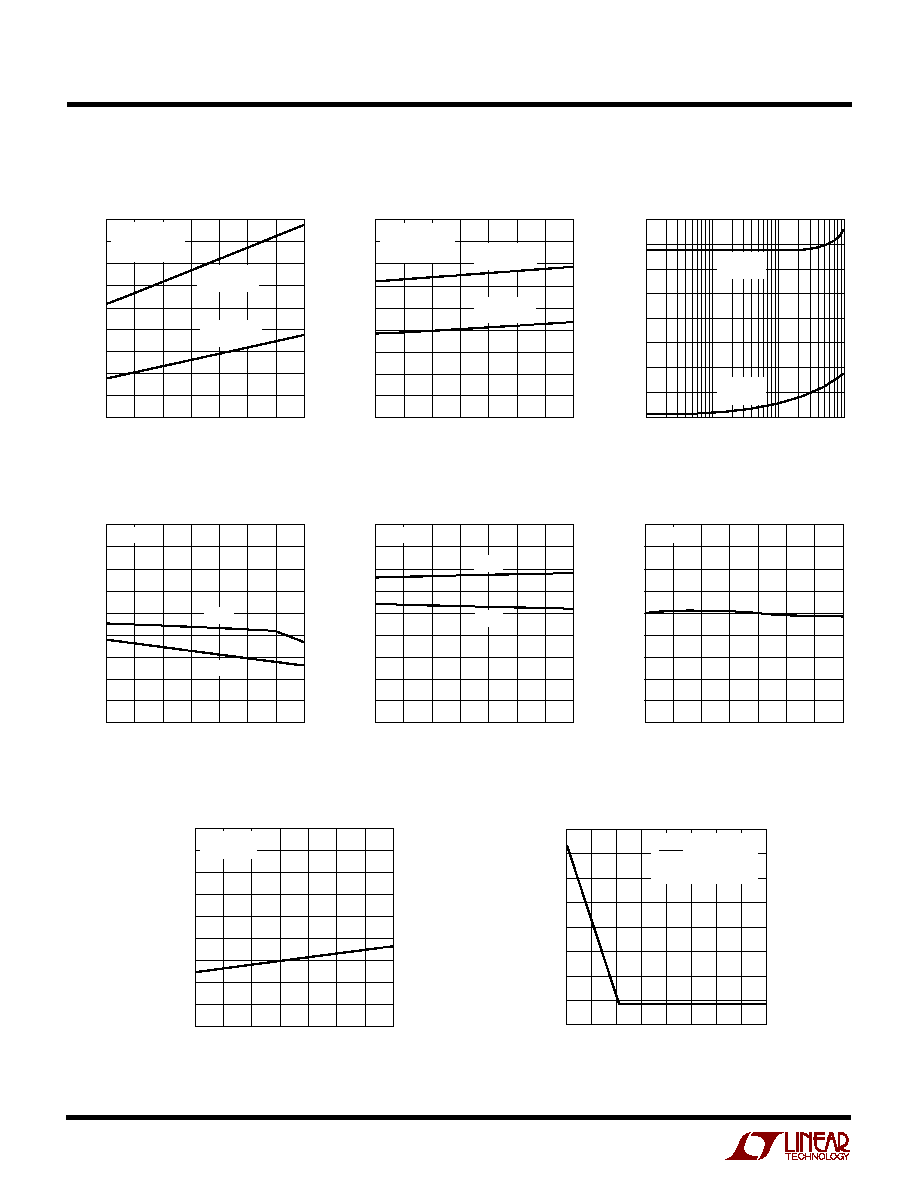

TYPICAL PERFOR

M

A

N

CE CHARACTERISTICS

U

W

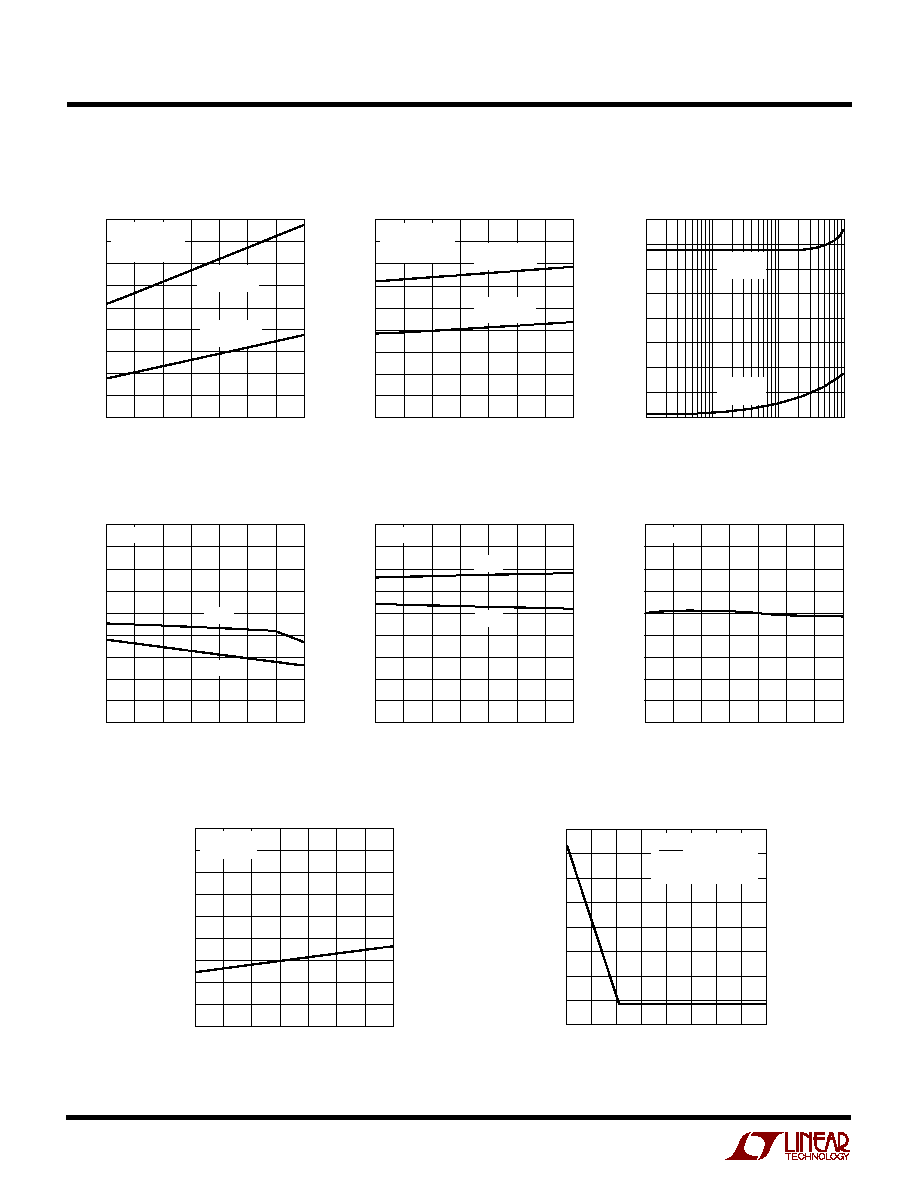

DC Supply Current

vs Supply Voltage

SUPPLY VOLTAGE (V)

0

SUPPLY CURRENT (

µ

A)

80

120

40

1473 G01

40

0

10

20

30

5

15

25

35

160

60

100

20

140

V

DIODE

= V

IN1

= 5V

V

IN2

= 0V

V

DIODE

= 5V

V

IN1

= V

IN2

= 0V

V

SENSE+

= V

SENSE

= V

+

DC Supply Current vs V

SENSE

DC Supply Current

vs Temperature

TEMPERATURE (

°

C)

50

50

SUPPLY CURRENT (

µ

A)

60

80

90

100

0

140

1473 G02

70

25

25

50

75

100

125

110

120

130

V

+

= 20V

V

DIODE

= V

IN1

= 5V

V

IN2

= 0V

V

DIODE

= 5V

V

IN1

= V

IN2

= 0V

V

GS

Gate-to-Source ON Voltage

vs Temperature

TEMPERATURE (

°

C)

50

5.1

V

GS

GATE-TO-SOURCE ON VOLTAGE (V)

5.2

5.4

5.5

5.6

0

6.0

1473 G04

5.3

25

25

50

75

100

125

5.7

5.8

5.9

V

+

= V

SAB

=20V

TEMPERATURE (

°

C)

50

1.0

SUPPLY VOLTAGE (V)

1.5

2.5

3.0

3.5

0

5.5

1473 G05

2.0

25

25

50

75

100

125

4.0

4.5

5.0

START-UP

THRESHOLD

SHUTDOWN

THRESHOLD

Undervoltage Lockout Threshold (V

+

)

vs Temperature

Note 4: Gate turn-on and turn-off times are measured with no inrush

current limiting, i.e., V

SENSE

= 0V. Gate rise times are measured from 1V to

4.5V and fall times are measured from 4.5V to 1V. Delay times are

measured from the input transition to when the gate voltage has risen or

fallen to 3V.

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: T

J

is calculated from the ambient temperature T

A

and power

dissipation P

D

according to the following formula:

T

J

= T

A

+ (P

D

)(150

°

C/W)

Note 3: I

S

increases by the same amount as I

BSENSE

+

+ I

BSENSE

when

their common mode falls below 5V.

ELECTRICAL CHARACTERISTICS

V

GS

Gate Supply Voltage

vs Temperature

TEMPERATURE (

°

C)

50

8.1

V

GS

GATE SUPPLY VOLTAGE (V)

8.2

8.4

8.5

8.6

0

9.0

1473 G03

8.3

25

25

50

75

100

125

8.7

8.8

8.9

V

+

= 20V

V

GS =

V

GG

V

+

|V

SENSE

| COMMON MODE(V)

0

SUPPLY CURRENT (

µ

A)

20

1473 · TPC02.5

5

10

15

2.5

7.5

12.5

17.5

500

450

400

350

300

250

200

150

100

V

+

= 20V

V

DIODE

= V

IN1

= 5V

V

IN2

= 0V

V

SENSE+

V

SENSE

= 0V

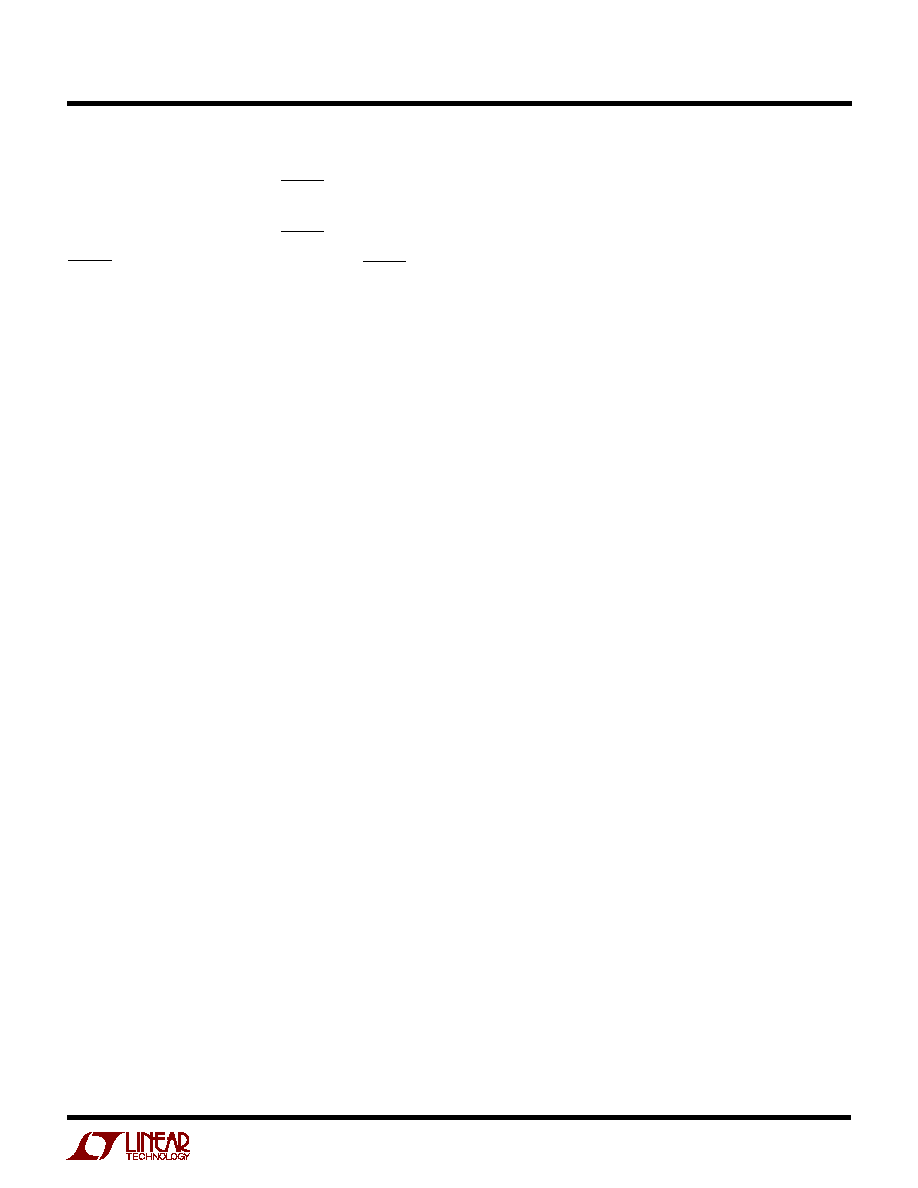

4

LTC1473

TYPICAL PERFOR

M

A

N

CE CHARACTERISTICS

U

W

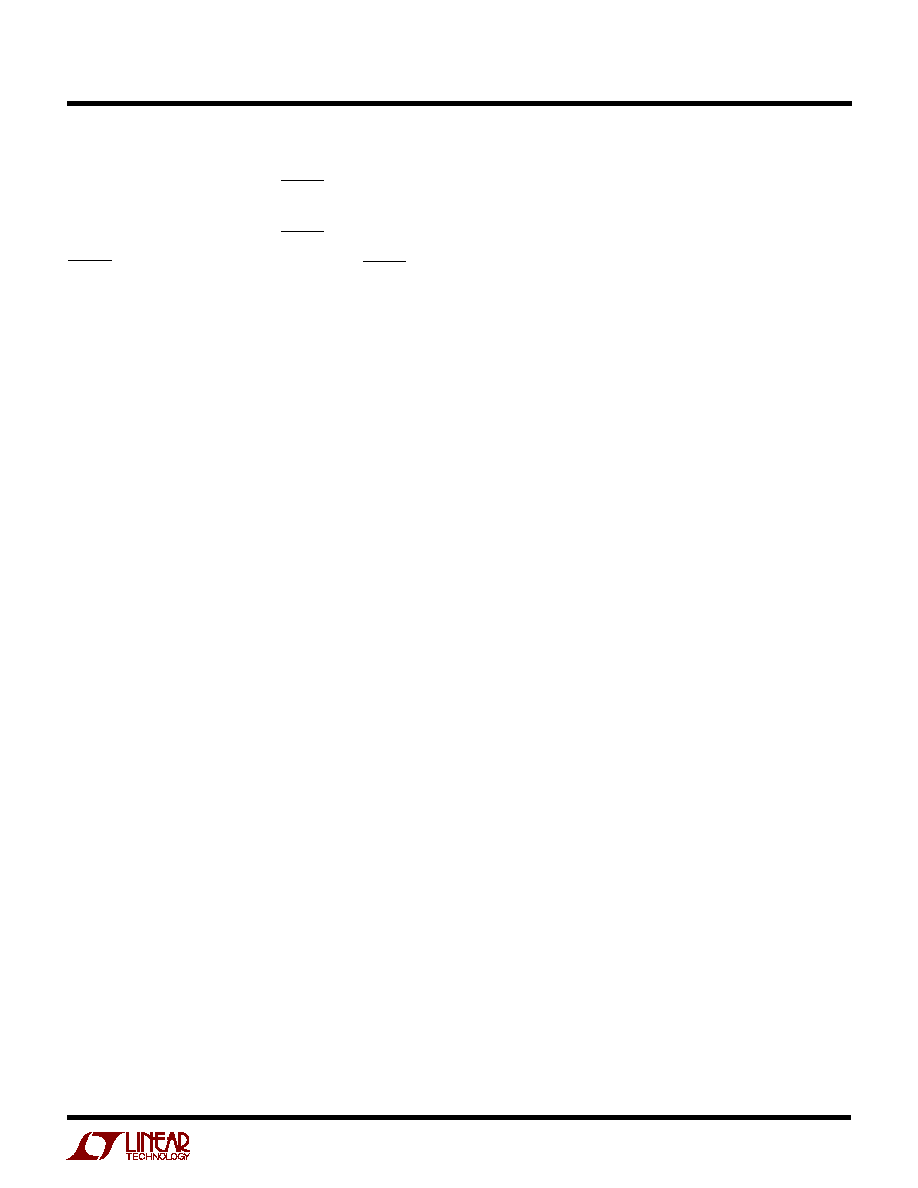

Logic Input Threshold Voltage

vs Temperature

TEMPERATURE (

°

C)

50

1.0

LOGCI INPUT THRESHOLD VOLTAGE (V)

1.1

1.3

1.4

1.5

0

1.9

1473 G11

1.2

25

25

50

75

100

125

1.6

1.7

1.8

V

HIGH

V

LOW

V

+

= 20V

Logic Input Threshold Voltage

vs Temperature

TEMPERATURE (

°

C)

50

1.0

LOGIC INPUT THRESHOLD VOLTAGE (V)

1.1

1.3

1.4

1.5

0

1.9

1473 G10

1.2

25

25

50

75

100

125

1.6

1.7

1.8

V

HIGH

V

LOW

V

+

= 5V

Timer Latch Threshold Voltage

vs Temperature

TEMPERATURE (

°

C)

50

1.10

TIMER LATCH THRESHOLD VOLTAGE (V)

1.12

1.16

1.18

1.20

0

1.28

1473 G12

1.14

25

25

50

75

100

125

1.22

1.24

1.26

V

+

= 20V

Timer Source Current

vs Temperature

TEMPERATURE (

°

C)

50

4.0

TIMER SOURCE CURRENT (

µ

A)

4.5

5.5

6.0

6.5

0

8.5

1473 G13

5.0

25

25

50

75

100

125

7.0

7.5

8.0

V

+

= 20V

TIMER = 0V

Turn-On Delay and Gate Rise Time

vs Temperature

TEMPERATURE (

°

C)

50

0

TURN-ON DELAY AND GATE RISE TIME (

µ

s)

5

15

20

25

0

45

1473 G06

10

25

25

50

75

100

125

30

35

40

GATE RISE

TIME

V

+

= 20V

C

LOAD

= 1000pF

V

SAB

= 0V

TURN-ON

DELAY

Turn-Off Delay and Gate Fall Time

vs Temperature

TEMPERATURE (

°

C)

50

0.4

TURN-OFF DELAY AND GATE FALL TIME (

µ

s)

0.6

1.0

1.2

1.4

0

2.2

1473 G07

0.8

25

25

50

75

100

125

1.6

1.8

2.0

GATE FALL

TIME

V

+

= 20V

C

LOAD

= 1000pF

V

SAB

= 20V

TURN-OFF

DELAY

Rise and Fall Time

vs Gate Capacitive Loading

GATE CAPACITIVE LOADING (pF)

10

20

RISE AND FALL TIME (

µ

s)

30

40

100

1000

10000

1473 G08

10

5

25

35

15

0

RISE TIME

V

SAB

= 0V

FALL TIME

V

SAB

= 20V

Sense Pin Source Current

I

BSENSE

vs V

SENSE

V

SENSE

(V)

0

SENSE PIN CURRENT (

µ

A)

20

1473 · TPC14

5

10

15

2.5

7.5

12.5

17.5

175

150

125

100

75

50

25

0

25

V

+

= 20V

V

DIODE

= V

IN1

= 5V

V

IN2

= 0V

V

SENSE+

V

SENSE

= 0V

5

LTC1473

PI

N

FU

N

CTIO

N

S

U

U

U

IN1 (Pin 1): Logic Input of Gate Drivers GA1 and GB1. IN1

is disabled when IN2 is high or DIODE is low.

IN2 (Pin 2): Logic Input of Gate Drivers GA2 and GB2. IN2

is disabled when IN1 is high or DIODE is low.

DIODE (Pin 3): "2-Diode Mode" Logic Input. DIODE over-

rides IN1 and IN2 by forcing the two back-to-back

external N-channel MOSFET switches to mimic two

diodes.

TIMER (Pin 4): Fault Timer. A capacitor connected from

this pin to GND programs the time the MOSFET switches

are allowed to be in current limit. To disable this function,

Pin 4 can be grounded.

V

+

(Pin 5): Input Supply. Bypass this pin with at least a 1

µ

F

capacitor.

V

GG

(Pin 6): Gate Driver Supply. This high voltage supply

is intended only for driving the internal micropower gate

drive circuitry.

Do not load this pin with any external

circuitry. Bypass this pin with at least 1

µ

F.

SW (Pin 7): Open Drain of an internal N-Channel MOSFET

Switch. This pin drives the bottom of the V

GG

switching

regulator inductor which is connected between this pin

and the V

+

pin.

GND (Pin 8): Ground.

GA2, GB2 (Pins 11, 9): Switch Gate Drivers. GA2 and GB2

drive the gates of the second back-to-back external

N-channel switches.

SAB2 (Pin 10): Source Return. The SAB2 pin is connected

to the sources of SW A2 and SW B2. A small pull-down

current source returns this node to 0V when the switches

are turned off.

SENSE

(Pin 12): Inrush Current Input. This pin should be

connected directly to the bottom (output side) of the low

value current sense resistor in series with the two input

power selector switch pairs, SW A1/B1 and SW A2/B2, for

detecting and controlling the inrush current into and out of

the power supply sources and the output capacitor.

SENSE

+

(Pin 13): Inrush Current Input. This pin should be

connected directly to the top (switch side) of the low value

current sense resistor in series with the two input power

selector switch pairs, SW A1/B1 and SW A2/B2, for

detecting and controlling the inrush current into and out of

the power supply sources and the output capacitor. Cur-

rent limit is invoked when (V

SENSE

+

V

SENSE

) exceeds

±

0.2V.

GA1, GB1 (Pins 16, 14): Switch Gate Drivers. GA1 and

GB1 drive the gates of the first back-to-back external

N-channel switches.

SAB1 (Pin 15): Source Return. The SAB1 pin is connected

to the sources of SW A1 and SW B1. A small pull-down

current source returns this node to 0V when the switches

are turned off.