Linear Integrated Systems

· 4042 Clipper Court · Fremont, CA 94538 · Tel: 510 490-9160 · Fax: 510 353-0261

FEATURES

HIGH SWITCHING SPEED

t

ON

= 2.0ns

LOW ON RESISTANCE

r

DS(ON)

= 5

LOW GATE NODE CAPACITANCE

C = 25pF

LOW GATE LEAKAGE CAPACITANCE

I

G(ON)

= 0.05µA

ABSOLUTE MAXIMUM RATINGS

1

@ 25 °C (unless otherwise stated)

Maximum Temperatures

Storage Temperature

-55 to +150 °C

Operating Junction Temperature

-55 to +125 °C

Maximum Power Dissipation

Continuous Power Dissipation

2

P

D

= 300mW

Maximum Currents

Pulsed Drain Current

3

I

DS

= 1A

Continuous Drain Current

2

I

DS

= 200mA

Maximum Voltages

V

DSO

Drain to Source

+25V

SST823

+22.5V

SST823 +15V

V

SB

Source to Body

SST824

+25V

V

SDO

Source to Drain

SST824 +20V

V

GB

Gate to Body

+30V

SST823 +22.5V

V

GS

Gate to Source

±22.5V

V

DB

Drain to Body

SST824 +30V

V

GD

Gate to Drain

±22.5V

ELECTRICAL CHARACTERISTICS @ 25 °C (unless otherwise stated)

SYMBOL

CHARACTERISTIC

MIN TYP MAX UNITS CONDITIONS

Breakdown Voltage

25

I

D

= 10µA, V

GS

= V

BS

= 0

BV

DS

Drain to Source

15

V

I

D

= 100nA, V

GS

= V

BS

= -5V

Breakdown Voltage

SST823

15

BV

SD

Source to Drain

SST824

20

V I

S

= 100nA, V

GD

= V

BD

= -5V

Breakdown Voltage

SST823

22.5

BV

DB

Drain to Body

SST824

25

V I

D

= 100nA, V

GB

= 0, Source Open

Breakdown Voltage

SST823

22.5

BV

SB

Source to Body

SST824

25

V I

S

= 100nA, V

GB

= 0, Drain Open

V

GS(OFF)

Cutoff Voltage Gate to Source

0.1

2

V

V

DS

= V

GS

, V

SB

= 0V, I

D

= 10µA

7.5

V

GS

= 5.0V, I

D

= 50mA, V

SB

= 0

r

DS(ON)

On Resistance Drain to Source

4

5.0

V

GS

= 10V, I

D

= 500mA, V

SB

= 0

g

fs

Forward

Transconductance

4

100

120

mmho V

DS

= 15V, I

D

= 200mA

I

D(OFF)

Leakage Current Drain Node

100

nA

V

GS

= V

BS

= -5V, V

DS

= 15V

I

S(OFF)

Leakage Current Source Node

100

nA

V

GD

= V

BD

= -5V, V

DS

= 15V

I

G(OFF)

Leakage Current Gate Node (OFF)

100

nA

V

GB

= 0V, V

GS

= V

GD

= -22.5V

I

G(ON)

Leakage Current Gate Node (ON)

10

µA

V

GB

= 30V, V

GS

= V

GD

= 22.5V

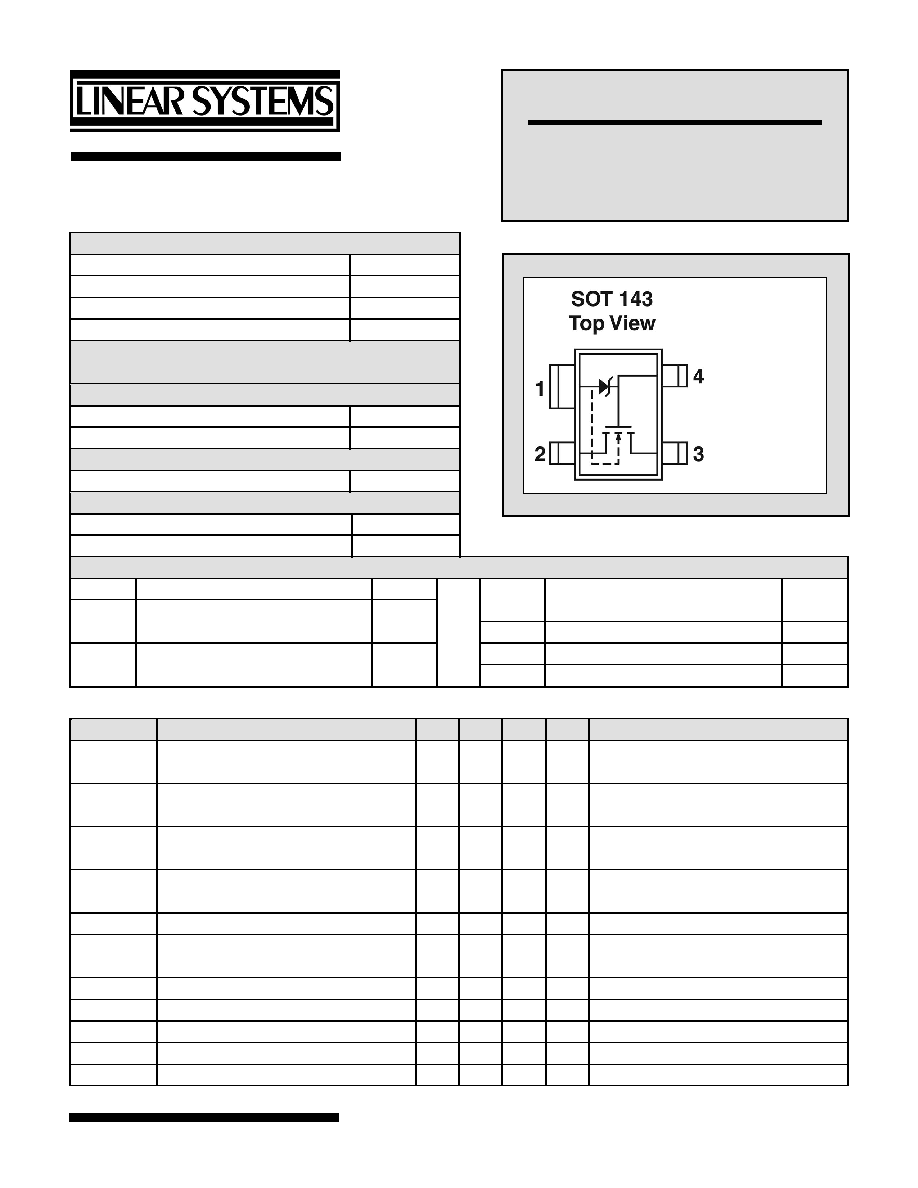

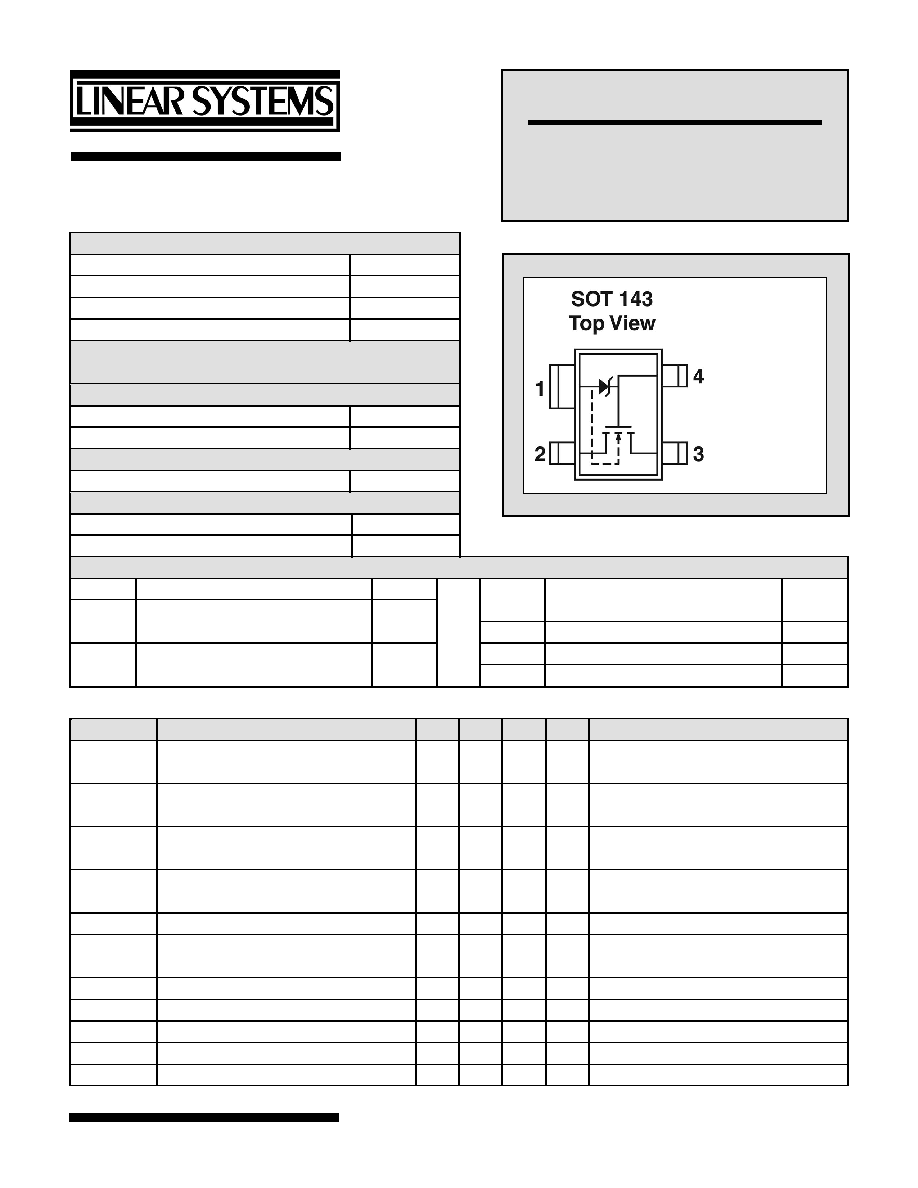

SST823 SST824

HIGH SPEED N-CHANNEL

LATERAL DMOS SWITCH

ZENER PROTECTED

Linear Integrated Systems

1. Body

2. Source

3. Drain

4.

Gate

Linear Integrated Systems

· 4042 Clipper Court · Fremont, CA 94538 · Tel: 510 490-9160 · Fax: 510 353-0261

NOTES

1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

2. For SOT143 package only.

3. Pulsed @ 80 µs, 1% duty cycle.

4. See test conditions in Electrical Characteristics section.

5. See

Switching

Characteristics and Test Circuit for detail.

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any

infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or

patent rights of Linear Integrated Systems.

ELECTRICAL CHARACTERISTICS CONT.

SYMBOL

CHARACTERISTIC

MIN TYP MAX UNITS CONDITIONS

C

(GS+GD+GB)

Capacitance Gate Node

25

30

pF

C

(GD+DB)

Capacitance Drain Node

13

15

pF

C

(GS+SB)

Capacitance Source Node

35

40

pF

C

DG

Capacitance Reverse Transfer

3

5

pF

V

DS

= 10V, V

GS

= V

BS

= -15V, f = 1MHz

t

ON

Turn

On

Time

5

2.0

3.0

ns

V

DD

= 10V, V

G(ON)

= 10V,

t

OFF

Turn

Off

Time

5

3.0

4.0

ns

R

L

= 133, R

G

= 51

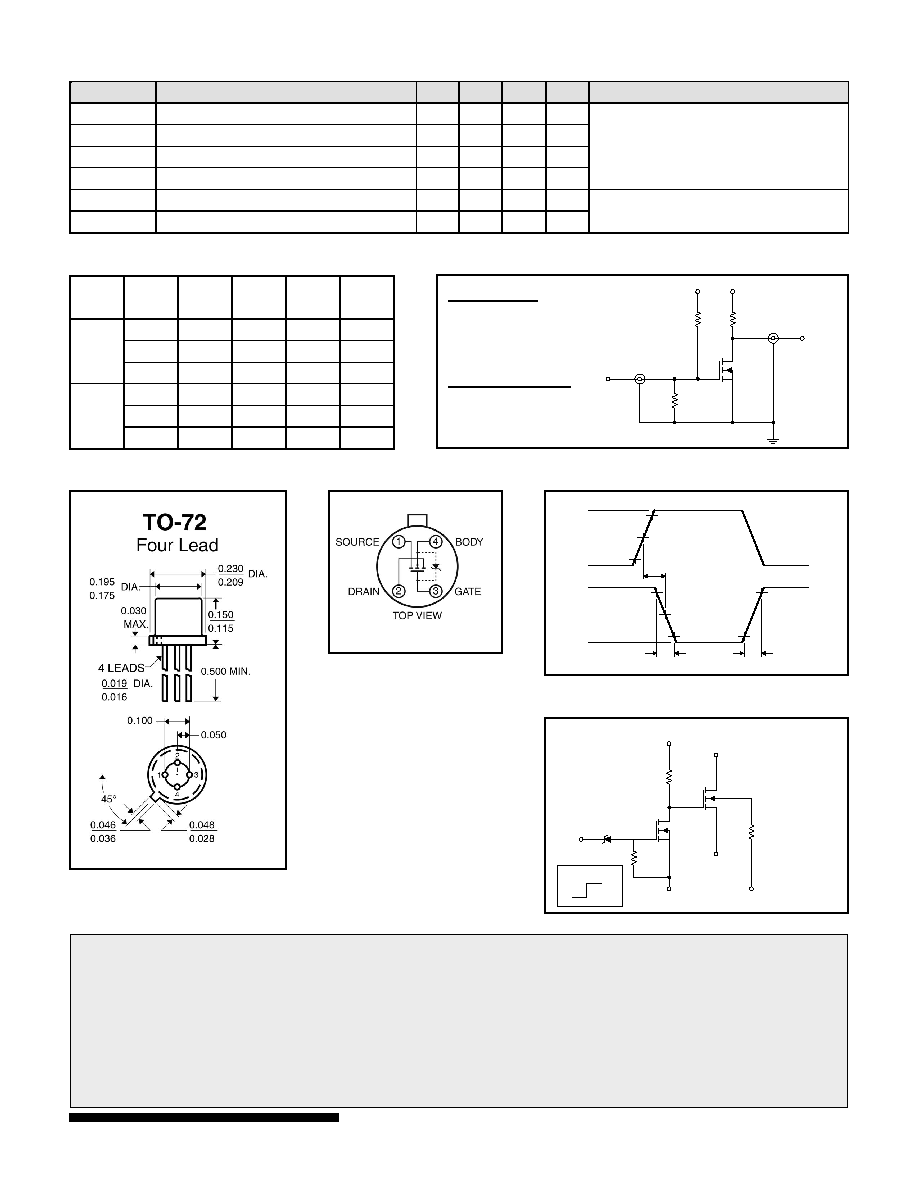

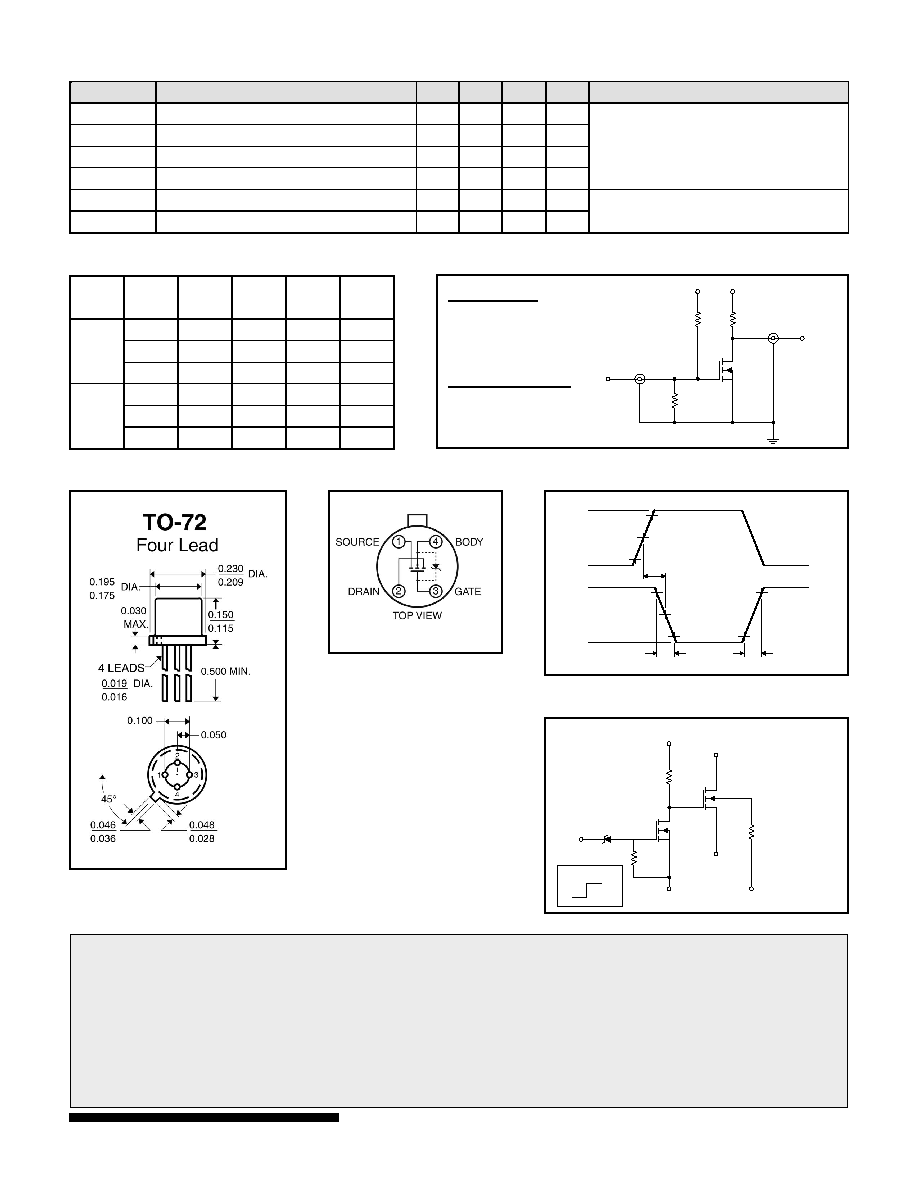

SWITCHING CHARACTERISTICS

t

d(ON)

t

r

t

OFF

V

GG

V

DD

R

L

TYP TYP TYP

5V 100 <1ns 1ns 3ns

10V 200 <1ns 1ns 3ns

5V

20V 300 <1ns 1ns 3ns

5V 67 <1ns 1ns 3ns

10V 133 <1ns 1ns 3ns

10V

20V 270 <1ns 1ns 3ns

INPUT PULSE

td, tr < 1ns

Pulse Width = 10ns

Rep Rate = 1MHz

SAMPLING SCOPE

t

r

< 360 ps

R

IN

= 1M

C

IN

= 2.0pF

51

R

L

510

V

IN

V

OUT

TO

SCOPE

V

GG

V

DD

TO SCOPE

TEST CIRCUIT

t

d(on)

90%

50%

10%

90%

50%

10%

t

r

t

OFF

0V

0 V

+ V

DD

V

GG

V

IN

V

OUT

SWITCHING WAVEFORMS

SST823

SST211

1 k

R

B

*

1 k

-15V

-15V

15V

Analog Output

±7.5V

Analog Input

±7.5V

15V

V

C

R

B

* Optional Current

Limiting Resistor

V

C

0

5V

Driver

Switch

DRIVER / SWITCH APPLICATION

PACKAGE OPTION

TO-72 PIN LAYOUT