Integrated

Circuit

Systems, Inc.

ICS952702

0795D--05/06/05

Pin Configuration

Recommended Application:

SiS746/746FX style chipset

Output Features:

·

1 - Pair of differential open drain CPU outputs

·

1 - Single-ended open drain CPU output

·

8 - PCICLK @ 3.3V including 2 PCI clock free running

·

2 - AGPCLK @ 3.3V

·

3 - REF @ 3.3V

·

2 - ZCLK @ 3.3V

·

2 - IOAPIC @ 2.5V

·

1 - 12_48MHz @ 3.3V

·

1 - 24_48MHz @ 3.3V

Key Specifications:

·

CPU Output Jitter <250ps

·

AGP Output Jitter <250ps

·

ZCLK Output Jitter <250ps

·

PCI Output Jitter <500ps

·

CPU-AGP/PCI/ZCLK skew: 2.5ns~3.5ns

Programmable Timing Control Hub for K7

TM

System

Functionality

Features/Benefits:

·

Selectable synchronous/asynchronous AGP/PCI

frequency

·

Programmable output frequency.

·

Programmable output divider ratios.

·

Programmable output rise/fall time.

·

Programmable output skew.

·

Programmable spread percentage for EMI control.

·

Watchdog timer technology to reset system

if system malfunctions.

·

Programmable watch dog safe frequency.

·

Support I2C Index read/write and block read/write

operations.

·

Uses external 14.318MHz reference or XTAL input.

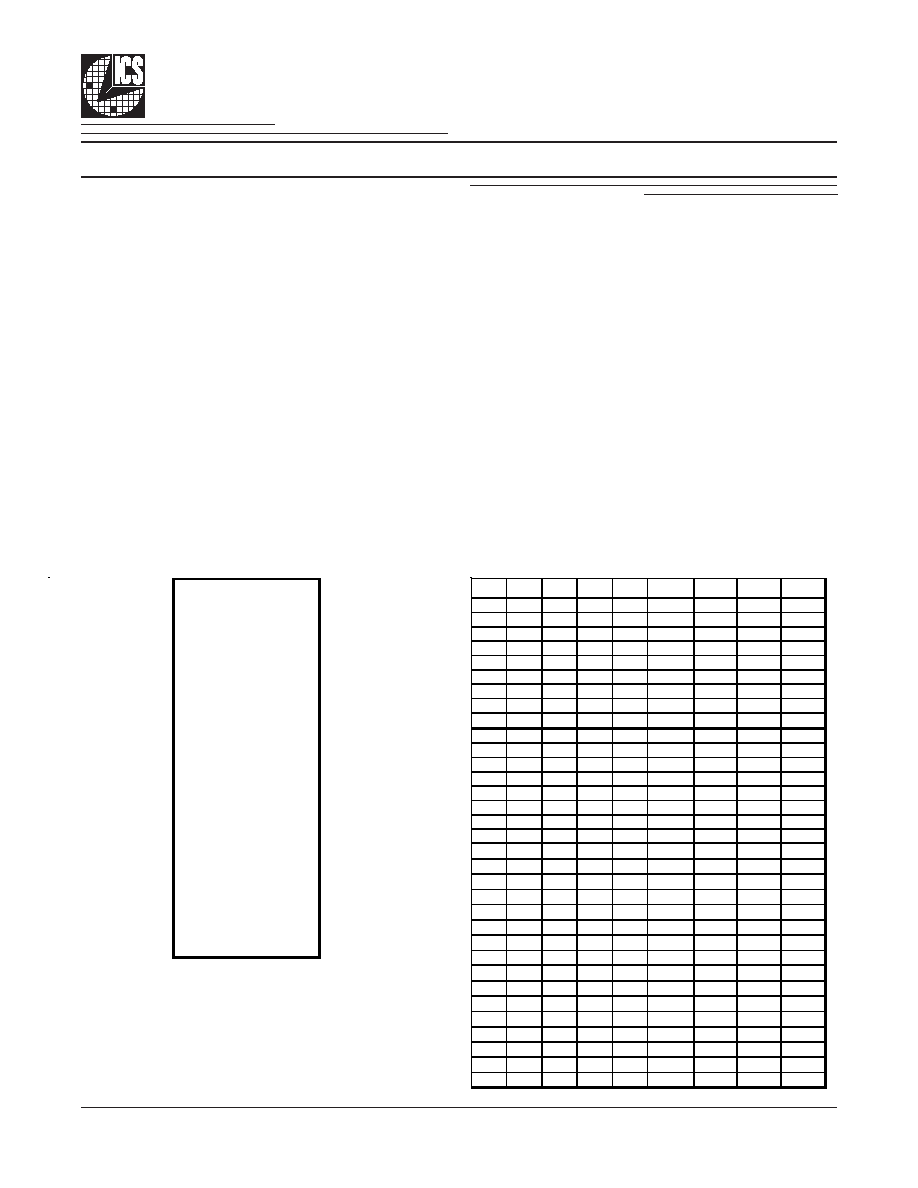

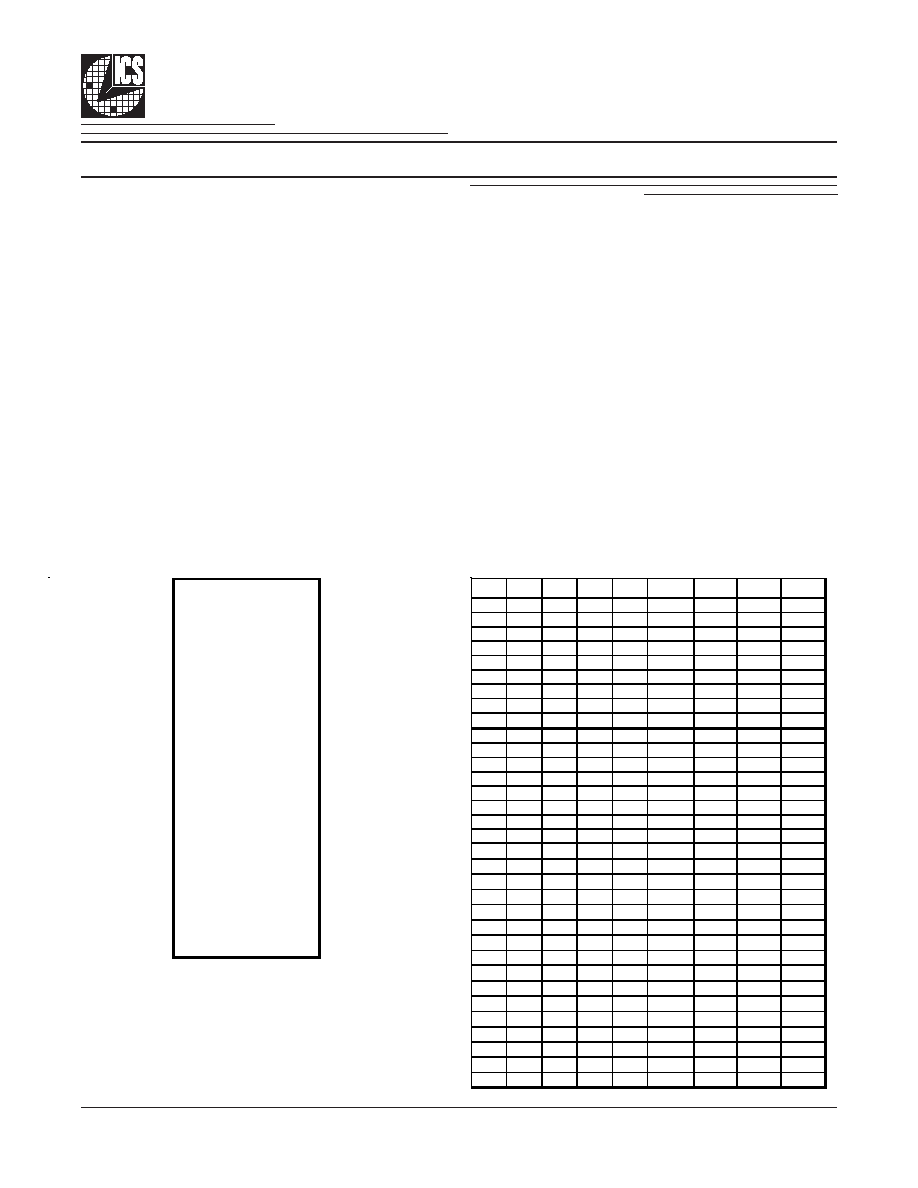

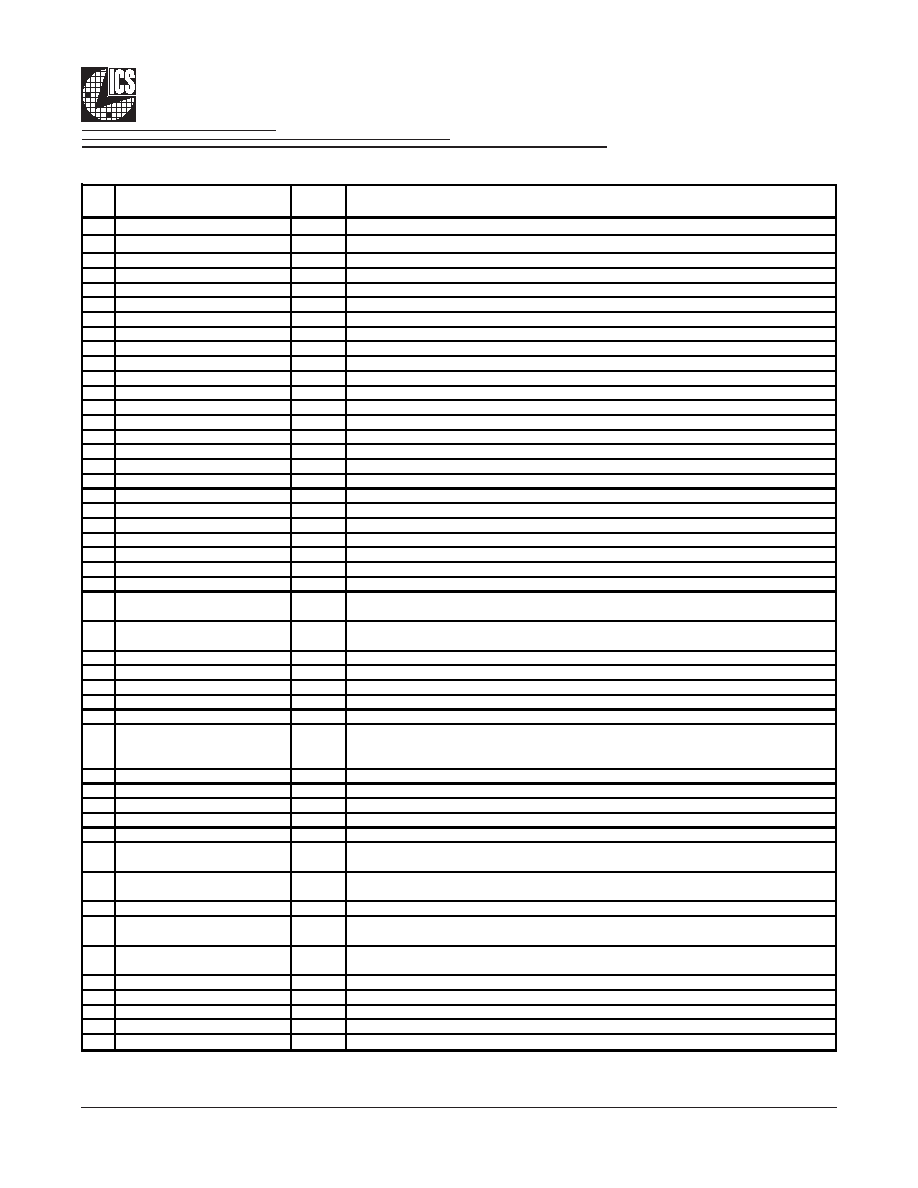

Bit4

Bit3

Bit2

Bit1

Bit0

CPU

ZCLK

AGP

PCI

FS4

FS3

FS2

FS1

FS0

MHz

MHz

MHz

MHz

0

0

0

0

0

200.00

133.33

66.67

33.33

0

0

0

0

1

200.99

133.99

67.00

33.50

0

0

0

1

0

200.00

66.67

66.67

33.33

0

0

0

1

1

206.00

137.33

68.67

34.33

0

0

1

0

0

133.33

133.33

66.67

33.33

0

0

1

0

1

214.00

142.66

71.33

35.67

0

0

1

1

0

218.00

145.33

72.67

36.33

0

0

1

1

1

222.00

148.00

74.00

37.00

0

1

0

0

0

100.00

133.33

66.67

33.33

0

1

0

0

1

100.99

134.65

67.33

33.66

0

1

0

1

0

100.00

66.67

66.67

33.33

0

1

0

1

1

103.00

137.33

68.67

34.33

0

1

1

0

0

100.00

133.33

66.67

33.33

0

1

1

0

1

107.00

142.66

71.33

35.67

0

1

1

1

0

109.00

145.33

72.67

36.33

0

1

1

1

1

111.00

148.00

74.00

37.00

1

0

0

0

0

166.67

133.33

66.67

33.33

1

0

0

0

1

166.99

133.59

66.80

33.40

1

0

0

1

0

166.67

66.67

66.67

33.33

1

0

0

1

1

171.67

137.33

68.67

34.33

1

0

1

0

0

175.00

140.00

70.00

35.00

1

0

1

0

1

178.34

142.66

71.33

35.67

1

0

1

1

0

181.67

145.33

72.67

36.33

1

0

1

1

1

185.00

148.00

74.00

37.00

1

1

0

0

0

133.33

133.33

66.67

33.33

1

1

0

0

1

133.99

133.99

67.00

33.50

1

1

0

1

0

133.33

66.67

66.67

33.33

1

1

0

1

1

137.33

137.33

68.67

34.33

1

1

1

0

0

140.00

140.00

70.00

35.00

1

1

1

0

1

142.66

142.66

71.33

35.67

1

1

1

1

0

145.33

145.33

72.67

36.33

1

1

1

1

1

148.00

148.00

74.00

37.00

VDDREF 1

48 VDDLAPIC

**FS0/REF0 2

47 IOAPIC1

**FS1/REF1 3

46 IOAPIC0

**FS4/REF2 4

45 GNDAPIC

GNDREF 5

44 CPU_STOP#*

X1 6

43 CPUCLKODT1

X2 7

42 RESET#

GNDZ 8

41 GNDCPU

ZCLK0 9

40 CPUCLKODT0

ZCLK1 10

39 CPUCLKODC0

VDDZ 11

38 VDDCPU

*PCI_STOP# 12

37 AGND

VDDPCI 13

36 AVDD

**FS2/PCICLK_F0 14

35 SCLK

*FS3/PCICLK_F1 15

34 SDATA

PCICLK0 16

33 PD#*

PCICLK1 17

32 GNDAGP

GNDPCI 18

31 AGPCLK0

VDDPCI 19

30 AGPCLK1

PCICLK2 20

29 VDDAGP

PCICLK3 21

28 AVDD48

PCICLK4 22

27 12_48MHz/SEL12#_48MHz*

PCICLK5 23

26 24_48MHz/SEL24#_48MHz**

GNDPCI 24

25 GND48

48-SSOP

* Internal Pull-Up Resistor

** Internal Pull-Down Resistor

I

C

S

952702

2

Integrated

Circuit

Systems, Inc.

ICS952702

0795D--05/06/05

The ICS952702 is a two chip clock solution for desktop designs using SIS 746 style chipsets. When used with a zero delay

buffer such as the ICS9179-16 for PC133 or the ICS93735 for DDR applications it provides all the necessary clocks signals

for such a system.

The ICS952702 is part of a whole new line of ICS clock generators and buffers called TCHTM (Timing Control Hub). ICS is the

first to introduce a whole product line which offers full programmability and flexibility on a single clock device. Employing the

use of a serially programmable I

2

C interface, this device can adjust the output clocks by configuring the frequency setting, the

output divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each

individual output clock. TCH also incorporates ICS's Watchdog Timer technology and a reset feature to provide a safe setting

under unstable system conditions. M/N control can configure output frequency with resolution up to 0.1MHz increment.

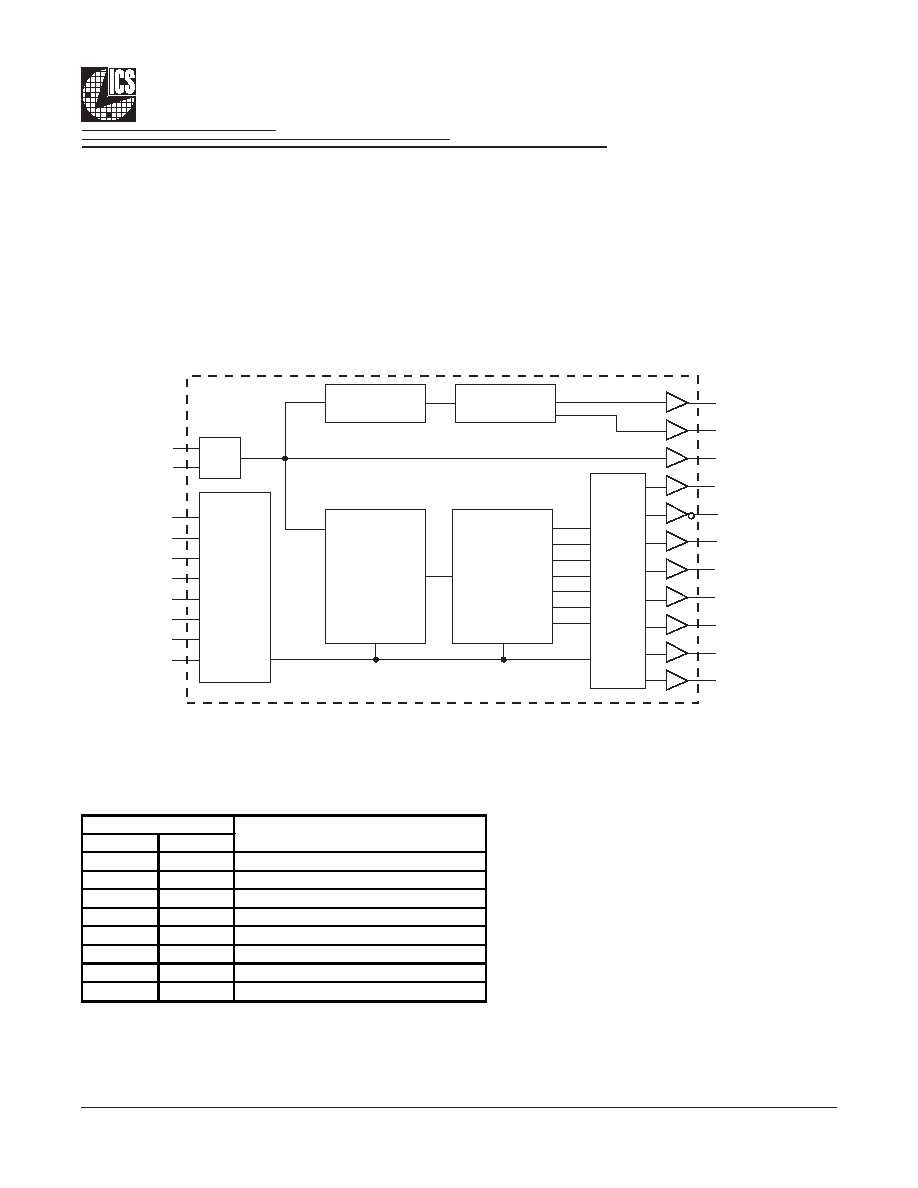

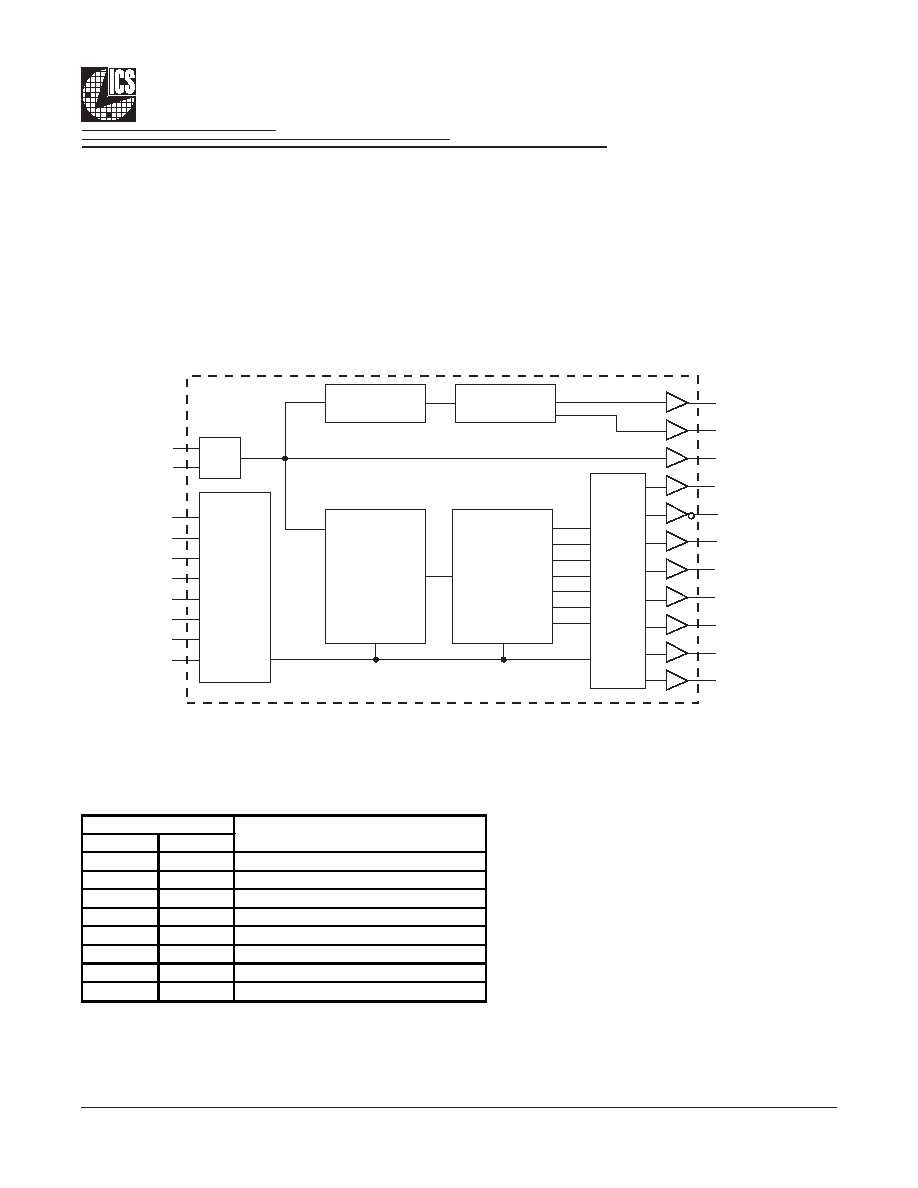

General Description

Block Diagram

Power Groups

PLL2

Frequency

Dividers

Programmable

Spread

PLL1

Programmable

Frequency

Dividers

STOP

Logic

ZCLK (1:0)

X1

X2

XTAL

CPU_STOP#

PCI_STOP#

SCLK

SEL24_48MHZ

SEL12_48

PD#

FS (4:0)

SDATA

Control

Logic

PCICLK (5:0)

AGPCLK (1:0)

12_48MHZ

24_48MHZ

REF (2:0)

CPUCLKODC0

CPUCLKODT (1:0)

RESET#

IOAPIC (1:0)

PCICLKF (1:0)

VDD

GND

1

5

REF output, Xtal

11

8

Hyper ZCLK output

28

25

24/48MHz fixed, Fixed PLL (Fix1)

13,19

18,24

PCICLK output

29

32

AGP output

48

45

IOAPIC output

38

41

CPU_T/C output

36

37

CPU PLL, CPU MCLK

Pin Number

Description

3

Integrated

Circuit

Systems, Inc.

ICS952702

0795D--05/06/05

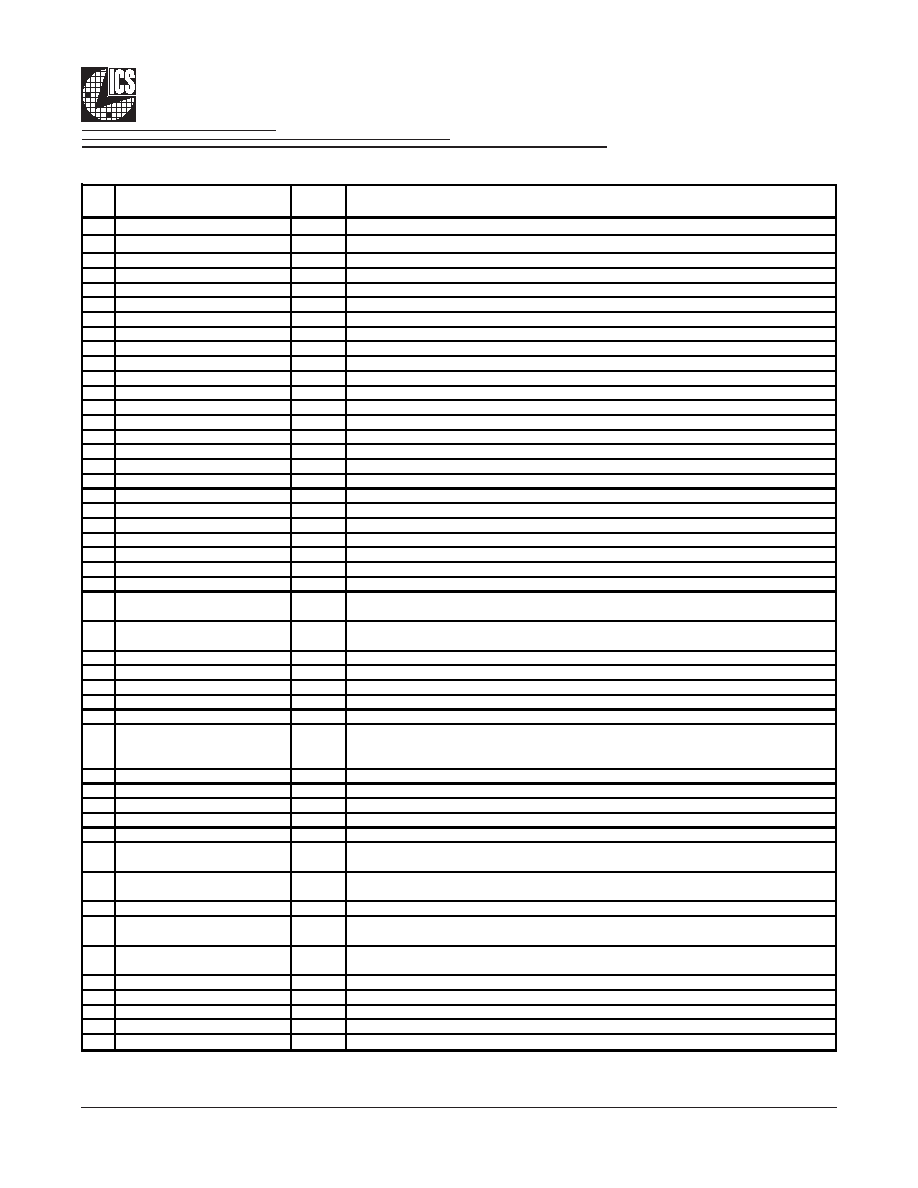

Pin Description

PIN #

PIN NAME

PIN

TYPE

DESCRIPTION

1

VDDREF

PWR

Ref, XTAL power supply, nominal 3.3V

2

**FS0/REF0

I/O

Frequency select latch input pin / 14.318 MHz reference clock.

3

**FS1/REF1

I/O

Frequency select latch input pin / 14.318 MHz reference clock.

4

**FS4/REF2

I/O

Frequency select latch input pin / 14.318 MHz reference clock.

5

GNDREF

PWR

Ground pin for the REF outputs.

6

X1

IN

Crystal input, Nominally 14.318MHz.

7

X2

OUT

Crystal output, Nominally 14.318MHz

8

GNDZ

PWR

Ground pin for the ZCLK outputs

9

ZCLK0

OUT

3.3V Hyperzip clock output.

10

ZCLK1

OUT

3.3V Hyperzip clock output.

11

VDDZ

PWR

Power supply for ZCLK clocks, nominal 3.3V

12

*PCI_STOP#

IN

Stops all PCICLKs besides the PCICLK_F clocks at logic 0 level, when input low.

13

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

14

**FS2/PCICLK_F0

I/O

Frequency select latch input pin / 3.3V PCI free running clock output.

15

*FS3/PCICLK_F1

I/O

Frequency select latch input pin / 3.3V PCI free running clock output.

16

PCICLK0

OUT

PCI clock output.

17

PCICLK1

OUT

PCI clock output.

18

GNDPCI

PWR

Ground pin for the PCI outputs

19

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

20

PCICLK2

OUT

PCI clock output.

21

PCICLK3

OUT

PCI clock output.

22

PCICLK4

OUT

PCI clock output.

23

PCICLK5

OUT

PCI clock output.

24

GNDPCI

PWR

Ground pin for the PCI outputs

25

GND48

PWR

Ground pin for the 48MHz outputs

26

24_48MHz/SEL24#_48MHz**

I/O

Selectable 24 or 48MHz clock output / Latched select input for 24/48MHz output. 0=24MHz,

1 = 48MHz.

27

12_48MHz/SEL12#_48MHz*

I/O

Selectable 12 or 48MHz clock output / Latched select input for 12/48MHz output. 0=12MHz,

1 = 48MHz.

28

AVDD48

PWR

Power for 24/48MHz outputs and fixed PLL core, nominal 3.3V

29

VDDAGP

PWR

Power supply for AGP clocks, nominal 3.3V

30

AGPCLK1

OUT

AGP clock output

31

AGPCLK0

OUT

AGP clock output

32

GNDAGP

PWR

Ground pin for the AGP outputs

33

PD#*

IN

Asynchronous active low input pin used to power down the device into a low power state. The

internal clocks are disabled and the VCO and the crystal are stopped. The latency of the

power down will not be greater than 1.8ms.

34

SDATA

I/O

Data pin for I2C circuitry 5V tolerant

35

SCLK

IN

Clock pin of I2C circuitry 5V tolerant

36

AVDD

PWR

3.3V Analog Power pin for Core PLL

37

AGND

PWR

Analog Ground pin for Core PLL

38

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

39

CPUCLKODC0

OUT

"Complememtary" clocks of differential pair CPU outputs. These open drain outputs need an

external 1.5V pull-up.

40

CPUCLKODT0

OUT

True clock of differential pair CPU outputs. These open drain outputs need an external 1.5V

pull-up.

41

GNDCPU

PWR

Ground pin for the CPU outputs

42

RESET#

OUT

Real time system reset signal for frequency gear ratio change or watchdog timer timeout.

This signal is active low.

43

CPUCLKODT1

OUT

True clock of differential pair CPU outputs. These open drain outputs need an external 1.5V

pull-up.

44

CPU_STOP#*

IN

Stops all CPUCLK besides the free running clocks

45

GNDAPIC

PWR

Ground pin for the IOAPIC outputs.

46

IOAPIC0

OUT

IOAPIC clock outputs, norminal 2.5V.

47

IOAPIC1

OUT

IOAPIC clock outputs, norminal 2.5V.

48

VDDLAPIC

PWR

Power pin for the IOAPIC outputs. 2.5V.

* Internal Pull-Up Resistor

** Internal Pull-Down Resistor

4

Integrated

Circuit

Systems, Inc.

ICS952702

0795D--05/06/05

General SMBus serial interface information for the ICS952702

How to Write:

· Controller (host) sends a start bit.

· Controller (host) sends the write address D2

(H)

· ICS clock will

acknowledge

· Controller (host) sends the begining byte location = N

· ICS clock will

acknowledge

· Controller (host) sends the data byte count = X

· ICS clock will

acknowledge

· Controller (host) starts sending

Byte N through

Byte N + X -1

(see Note 2)

· ICS clock will

acknowledge each byte one at a time

· Controller (host) sends a Stop bit

How to Read:

· Controller (host) will send start bit.

· Controller (host) sends the write address D2

(H)

· ICS clock will

acknowledge

· Controller (host) sends the begining byte

location = N

· ICS clock will

acknowledge

· Controller (host) will send a separate start bit.

· Controller (host) sends the read address D3

(H)

· ICS clock will

acknowledge

· ICS clock will send the data byte count = X

· ICS clock sends

Byte N + X -1

· ICS clock sends

Byte 0 through byte X (if X

(H)

was written to byte 8)

.

· Controller (host) will need to acknowledge each

byte

· Controllor (host) will send a not acknowledge bit

· Controller (host) will send a stop bit

ICS (Slave/Receiver)

T

WR

ACK

ACK

ACK

ACK

ACK

P

stoP bit

X Byt

e

Index Block Write Operation

Slave Address D2

(H)

Beginning Byte = N

WRite

starT bit

Controller (Host)

Byte N + X - 1

Data Byte Count = X

Beginning Byte N

T

starT bit

WR

WRite

RT

Repeat starT

RD

ReaD

Beginning Byte N

Byte N + X - 1

N

Not acknowledge

P

stoP bit

Slave Address D3

(H)

Index Block Read Operation

Slave Address D2

(H)

Beginning Byte = N

ACK

ACK

Data Byte Count = X

ACK

ICS (Slave/Receiver)

Controller (Host)

X Byt

e

ACK

ACK