iC-MFN

8-FOLD FAIL-SAFE N-FET DRIVER

Ausgabe A1, Seite 1/12

TSSOP20

EIGENSCHAFTEN

ANWENDUNGEN

Ë

8-fach Level-Shifter auf 5 V Ausgangsspannung

Ë

Sicherer Low-Zustand der Ausgänge bei Einfachfehlern

Ë

Schmitt-Trigger-Eingänge mit zweistufigem Pull-Down-Strom

zur Erhöhung der Störsicherheit bei begrenzter

Verlustleistung

Ë

Eingänge kompatibel zu TTL- und CMOS-Pegeln

(1.8 V bis 5 V)

Ë

Strombegrenzte und kurzschlussfeste Push-Pull-Endstufen

Ë

Push-Pull-Stromquellen zur Ansteuerung von

FET-Transistoren

Ë

Spannungsfeste Ausgänge bis 18 V (gepulst)

Ë

Überwachung der Anschlüsse von Masse und

Versorgungsspannung

Ë

ESD-Schutzbeschaltung

Ë

Erweiterter Temperaturbereich von -40 ... +150 °C

Ë

Betrieb von 5V-Logic-Level-

n-FETs aus 3.3V-Systemen

GEHÄUSE

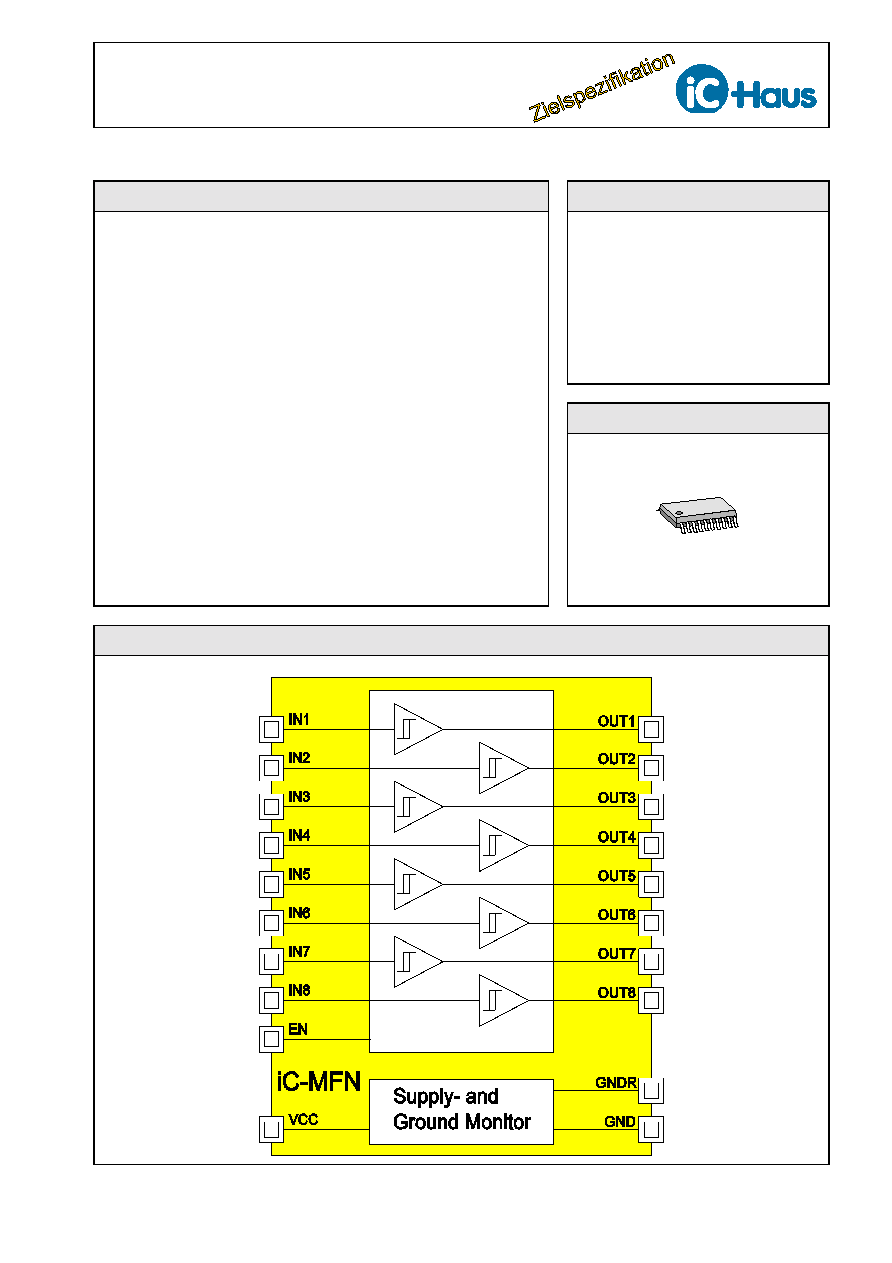

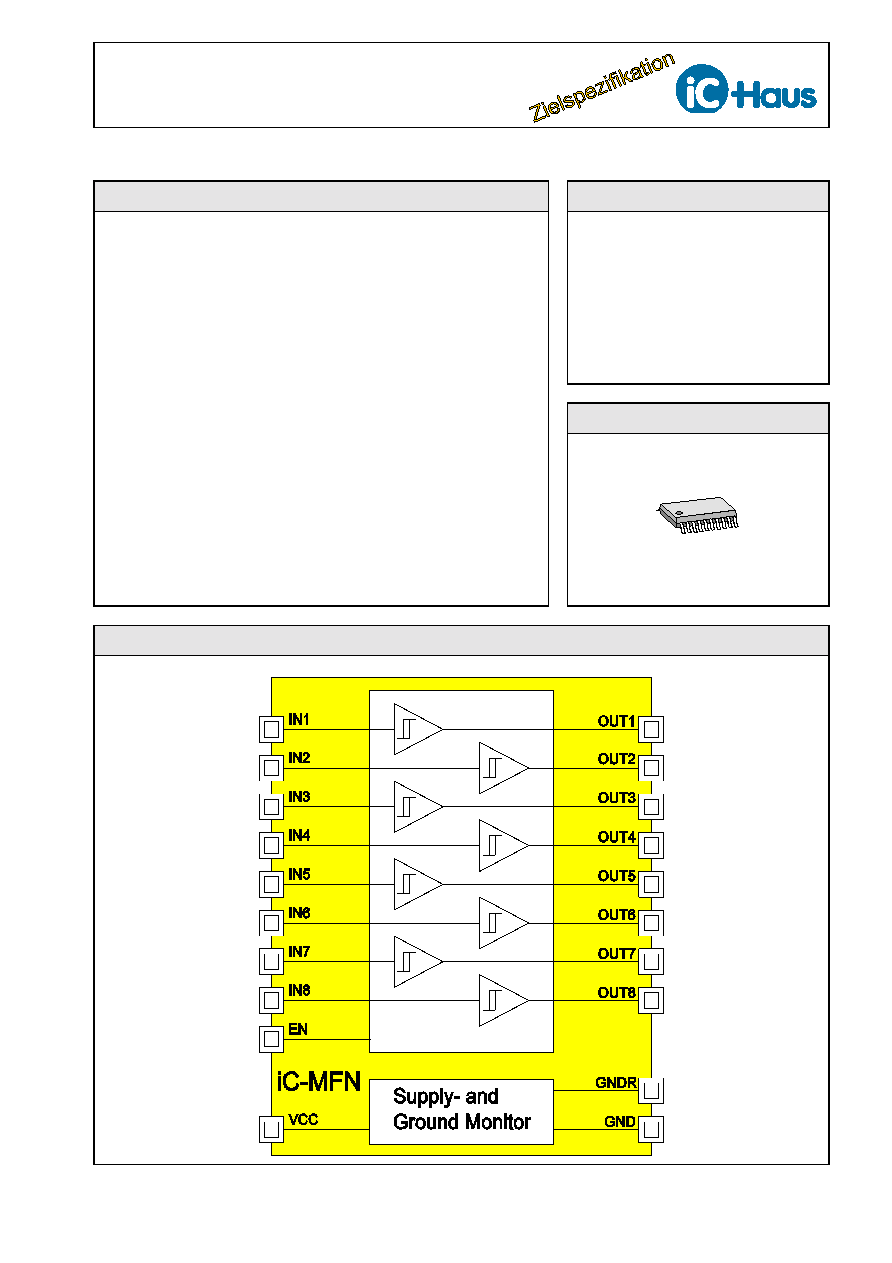

BLOCKSCHALTBILD

Copyright © 2003, iC-Haus

www.ichaus.com

iC-MFN

8-FOLD FAIL-SAFE N-FET DRIVER

Ausgabe A1, Seite 2/12

KURZBESCHREIBUNG

iC-MFN ist ein monolithisch integrierter, achtkanaliger Pegelanpassungsbaustein zur Ansteuerung von

n-Kanal FETs. Die internen Schaltungsblöcke sind dabei so aufgebaut, dass die Ausgangsstufen des iC-MFN

bei Einfachfehlern durch offene Pins oder durch Kurzschluss zweier Ausgänge in den sicheren, definierten

Low-Zustand gehen. Das iC-MFN schaltet somit bei einem Einfachfehler einen extern angeschlosenen n-

Kanal FET aus.

Die Eingänge der acht Kanäle bestehen aus einem Schmitt-Trigger mit Pull-Down-Stromquelle und sind zu

TTL- und CMOS-Pegeln (1.8 V bis 5 V) kompatibel. Die acht Kanäle haben am Ausgang eine strombegrenzte

Push-Pull-Endstufe und einen Pull-Down-Widerstand. Die Endstufen liefern ein Ausgangssignal von 5 V und

werden über ein hi-Signal am Pin EN freigegeben. Weiterhin können alle Endstufen kurze Störpulse von bis

zu 18 V am Ausgang aushalten.

Der Baustein iC-MFN überwacht die Versorgungsspannung an VCC und die Spannungen an den beiden

Masseanschlüssen GND und GNDR. Letztere müssen extern miteinander verbunden werden, um im

Fehlerfall den sicheren Low-Zustandes der Ausgangsstufen zu gewährleisten.

Falls die Versorgungsspannung an VCC unter eine definierte Schwelle fällt, so erzeugt die

Spannungsüberwachung ein internes Fehlersignal, mit dem die Ausgänge aktiv über die Low-Side-

Transistoren auf GND gezogen werden. Fällt die Versorgungsspannung an VCC ganz weg, so werden die

Ausgänge über Pull-Down-Widerstände auf GNDR gezogen.

Fällt das Massepotenzial an GND weg, so werden die High-Side- und Low-Side-Transistoren der Endstufen

abgeschaltet und die Ausgänge über Pull-Down-Widerstände auf GNDR gezogen.

Fällt dagegen das Massepotenzial an GNDR weg, so werden nur die High-Side-Transistoren der Endstufen

abgeschaltet und die Ausgänge aktiv über die Low-Side-Transistoren auf GND gezogen.

Offene Eingänge IN1..8 bzw. EN werden durch Pull-Down-Ströme aktiv auf GND gezogen. Die Pull-Down-

Ströme sind zweistufig ausgeführt, um bei erhöhter Störsicherheit die Verlustleistung zu begrenzen.

Falls sich beim Kurzschluss zweier Ausgänge eine Ausgangsstufe im Low- und die andere im High-Zustand

befindet, so überwiegt die Stromfähigkeit des Low-Side-Treibers und hält somit die angeschlossenen

n-Kanal-FETs im sicheren ausgeschalteten Zustand.

Der Baustein ist gegen Zerstörung durch ESD geschützt.

iC-MFN

8-FOLD FAIL-SAFE N-FET DRIVER

Ausgabe A1, Seite 3/12

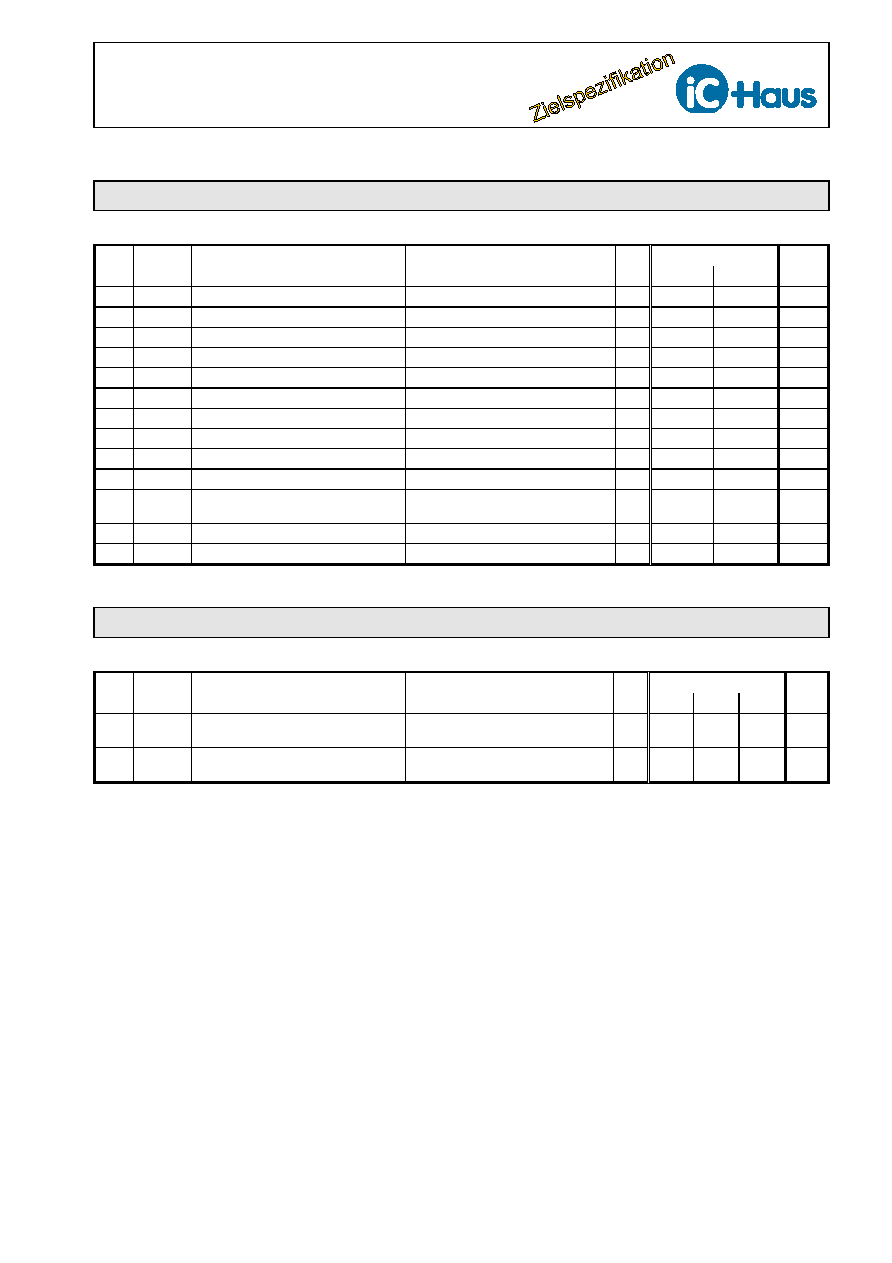

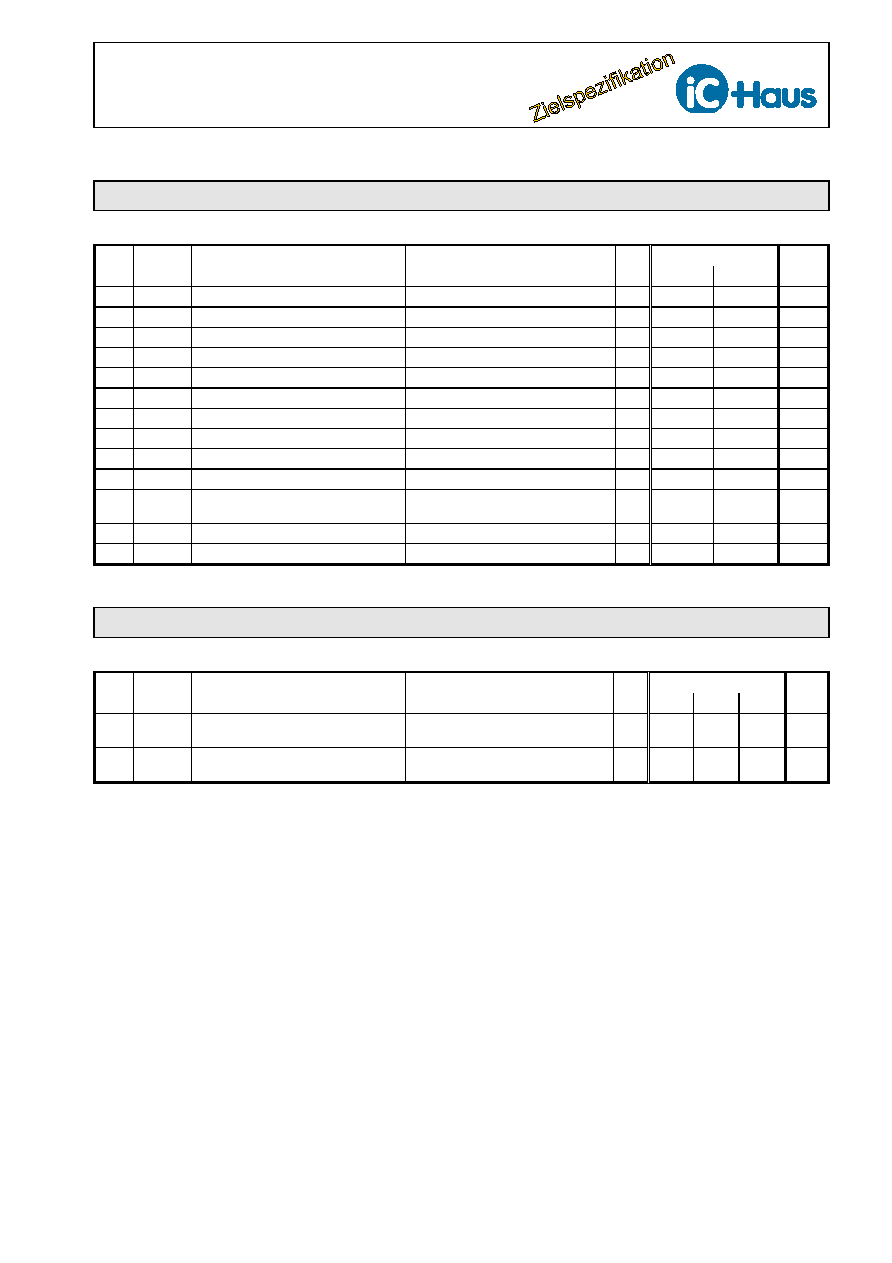

GEHÄUSE TSSOP20 nach JEDEC-Standard

ANSCHLUSSBELEGUNG TSSOP20 4.4 mm

PIN-FUNKTIONEN

(von oben)

Nr. Name Funktion

1

VCC

5 V Spannungsversorgung

2

IN1

Eingang Kanal 1

3

IN2

Eingang Kanal 2

4

IN3

Eingang Kanal 3

5

IN4

Eingang Kanal 4

6

IN5

Eingang Kanal 5

7

IN6

Eingang Kanal 6

8

IN7

Eingang Kanal 7

9

IN8

Eingang Kanal 8

10 EN

Enable-Eingang

11 GND

Masse

12 OUT8 5 V Ausgang Kanal 8

13 OUT7 5 V Ausgang Kanal 7

14 OUT6 5 V Ausgang Kanal 6

15 OUT5 5 V Ausgang Kanal 5

16 OUT4 5 V Ausgang Kanal 4

17 OUT3 5 V Ausgang Kanal 3

18 OUT2 5 V Ausgang Kanal 2

19 OUT1 5 V Ausgang Kanal 1

20 GNDR Masse (R)

iC-MFN

8-FOLD FAIL-SAFE N-FET DRIVER

Ausgabe A1, Seite 4/12

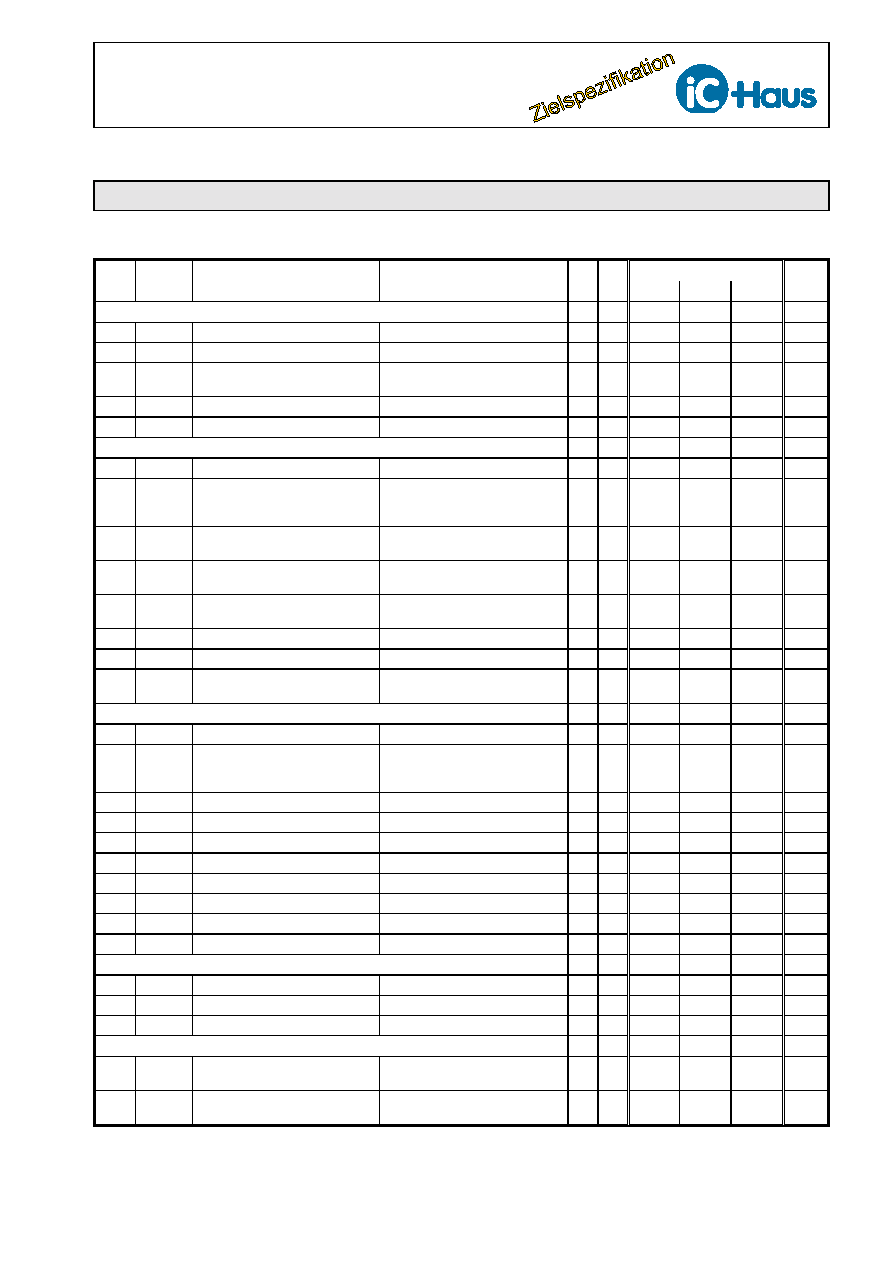

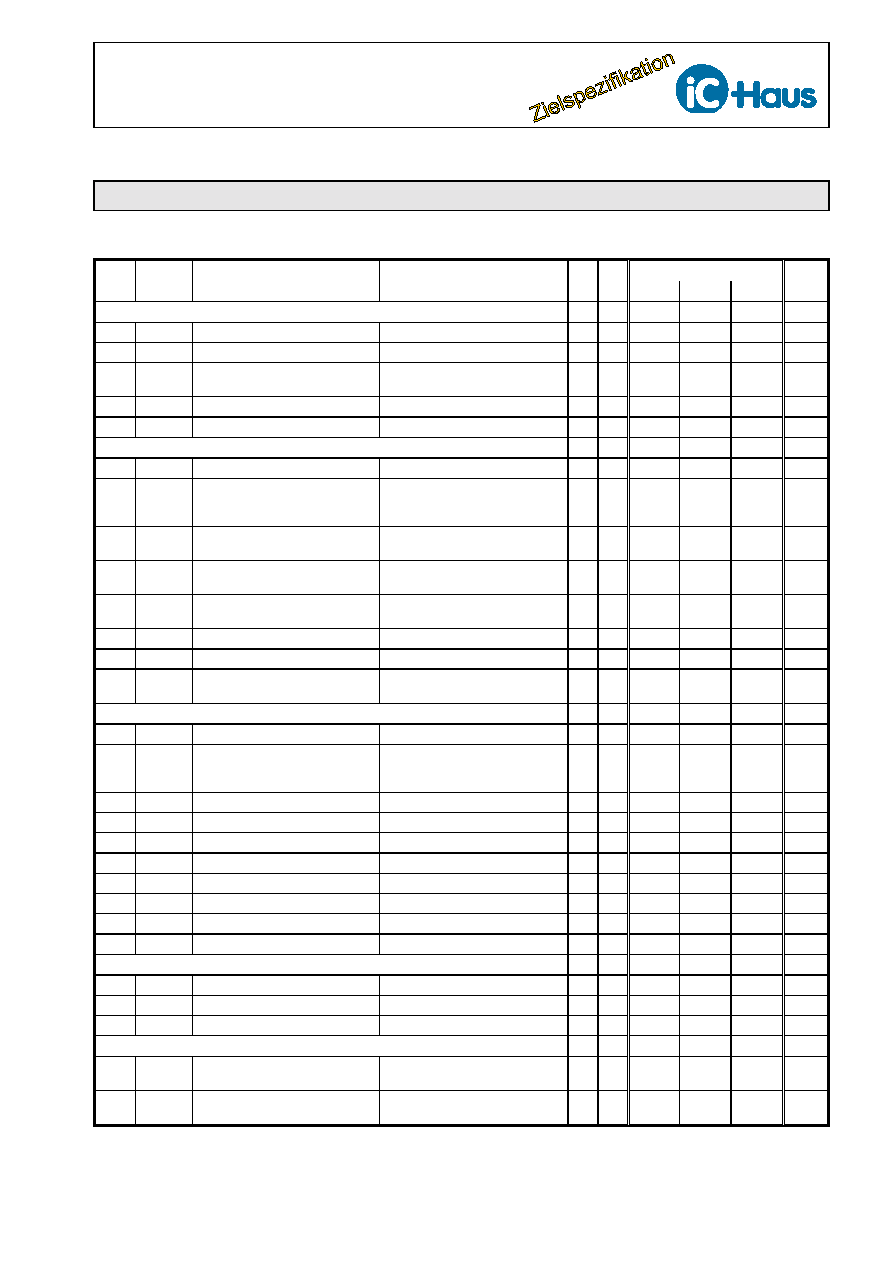

Alle Spannungsangaben beziehen sich auf Masse (Ground), wenn kein anderer Bezugspunkt angegeben ist.

In den Baustein hinein fließende Ströme zählen positiv, heraus fließende Ströme negativ.

GRENZWERTE

Keine Zerstörung, Funktion nicht garantiert.

Kenn Formel-

Benennung

Bedingungen

Bild

Einh.

Nr.

zeichen

Min.

Max.

G001 VCC

Versorgungsspannung

-0.3

6

V

G002 V()

Spannung an OUT1...8

-0.3

6

V

G003 Vp()

Peak Spannung an OUT1...8

t < 100 ms, Duty Cycle < 2 %

-0.3

18

V

G004 V()

Spannung an IN1...8, EN

-0.3

6

V

G005 V(GNDR) Spannung an GNDR gegen GND

-0.3

0.3

V

G006 V(GND)

Spannung an GND gegen GNDR

-0.3

0.3

V

G007 Imx()

Strom in OUT1...8, IN1...8, EN

-10

10

mA

G008 Imx()

Strom in OUT1...8

t < 100 ms, Duty Cycle < 2 %

-10

120

mA

G009 Imx()

Strom in VCC, GND

-50

50

mA

G010 Imx()

Strom in GND, GNDR

t < 100 ms, Duty Cycle < 2 %

-100

10

mA

E001 Vd()

Zulässige ESD-Prüfspannung an allen

Pins

MIL-STD-883, Methode 3015,

HBM 100 pF entladen über 1.5 k

2

kV

TG1 Tj

Chip-Temperatur

-40

150

EC

TG2 Ts

Lagertemperatur

-55

125

EC

THERMISCHE DATEN

Betriebsbedingungen: VCC = 5 V ± 10 %

Kenn Formel-

Benennung

Bedingungen

Bild

Einh.

Nr.

zeichen

Min.

Typ.

Max.

T1

Ta

Zulässiger Umgebungstemperatur-

bereich

-40

125

EC

T2

Rthja

Thermischer Widerstand

Chip/Umgebung

auf Board gelötet, ohne besondere

Kühlflächen

75

K/W

iC-MFN

8-FOLD FAIL-SAFE N-FET DRIVER

Ausgabe A1, Seite 5/12

KENNDATEN

Betriebsbedingungen:

VCC = 5 V ± 10 %, Tj = -40 ... 150

EC, wenn nicht anders angegeben

Kenn Symbol

Benennung

Bedingungen

Tj

Bild

Einh.

Nr.

EC

Min.

Typ.

Max.

Allgemeines

001 VCC

Zulässige Versorgungsspannung

4.5

5

5.5

V

002 I(VCC)

Versorgungsstrom in VCC

ohne Last

7

mA

003 I(VCC)

Fehlerstrom in VCC

VCC = 5 V,

ein Ausgang auf 18 V

-40

mA

004 I(GND)

Strom in GND

ohne Last

-6

mA

005 I(GNDR) Strom in GNDR

ohne Last, alle OUTx = hi

-4

-0.7

mA

Current Driver OUT1...8

101 Vc()hi

Klemmspannung hi

I() = 100 mA

18

30

V

102 Vc()lo

Klemmspannung lo gegen

niedrigstes Potenzial von

GND, GNDR

I() = -10 mA

-1.4

-0.7

V

103 Vs()hi

Sättigungsspannung hi gegen

VCC

I() = -0.5 mA

I() = -2 mA

-0.2

-0.8

V

V

104 Vs()lo

Sättigungsspannung lo gegen

GND

I() = 0.5 mA

I() = 2 mA

0.2

0.8

V

V

105 Rpd()

Pull-Down-Widerstand an OUTx

gegen GNDR

V(GND) > Vtr(GND)

12

30

70

k

106 Isc()lo

Kurzschlussstrom lo

V() = 0.8 V ... VCC

2

3.6

6

mA

107 Isc()hi

Kurzschlussstrom hi

V() = 0 ... VCC - 0.8 V

-6

-3

-2

mA

108 Vsh()

Ausgangsspannung bei

Kurzschluss zweier Ausgänge

bei zwei unterschiedlichen

Eingangssignalen hi und lo

1

V

Input IN1...8, EN

201 Vc()hi

Klemmspannung hi

I() = 10 mA

6

V

202 Vc()lo

Klemmspannung lo gegen

niedrigstes Potential von

GND, GNDR

I() = -10 mA

-1.4

-0.7

V

203 Vt()hi

Schwellspannung hi

1.15

1.4

V

204 Vt()lo

Schwellspannung lo

0.8

1.05

V

205 Vt()hys

Hysterese

Vt()hys = Vt()hi - Vt()lo

200

400

mV

206 Ipd1()

Pull-Down-Strom 1

0.4 V < V() < Vt()hi

3

150

225

350

µA

207 Ipd2()

Pull-Down-Strom 2

V() > 1.4 V

3

20

45

70

µA

208 Cin()

Eingangskapazität

20

pF

209 Ileak()

Eingangsleckstrom

VCC = 0 V, V() = 0 ... 5.5 V

-10

10

µA

210 Vl()

Leerlaufspannung

V

Supply Monitor

301 VCCon

Einschaltschwelle VCC

3.9

4.4

V

302 VCCoff

Abschaltschwelle VCC

abnehmende Spannung VCC

3.5

4.1

V

303 VCChys Hysterese

VCChys = VCCon - VCCoff

200

mV

Ground Monitor GND, GNDR

401 Vtg()

GND-Überwachung

Monitorschwelle an GND bezogen

auf GNDR

30

80

150

mV

402 Vtr()

GNDR-Überwachung

Monitorschwelle an GNDR

bezogen auf GND

30

80

150

mV