GL850

USB 2.0

4-PORT HUB Controller

Datasheet

Revision 1.11

Jun. 25, 2003

Genesys Logic, Inc.

GL850 USB 2.0 4-Port HUB Controller

©2000-2003

Genesys

Logic

Inc.--All

rights

reserved. Page

2

Copyright:

Copyright © 2003 Genesys Logic Incorporated. All rights reserved. No part of the materials may be

reproduced in any form or by any means without prior written consent of Genesys Logic Inc..

Disclaimer:

ALL MATERIALS ARE PROVIDED "AS IS" WITHOUT EXPRESS OR IMPLIED WARRANTY OF ANY

KIND. NO LICENSE OR RIGHT IS GRANTED UNDER ANY PATENT OR TRADEMARK OF

GENESYS LOGIC INC.. GENESYS LOGIC HEREBY DISCLAIMS ALL WARRANTIES AND

CONDITIONS IN REGARD TO MATERIALS, INCLUDING ALL WARRANTIES, IMPLIED OR

EXPRESS, OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, AND

NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. IN NO EVENT SHALL GENESYS LOGIC

BE LIABLE FOR ANY DAMAGES INCLUDING, WITHOUT LIMITATION, DAMAGES RESULTING

FROM LOSS OF INFORMATION OR PROFITS. PLEASE BE ADVISED THAT THE MATERIALS

MAY CONTAIN ERRORS OR OMMISIONS. GENESYS LOGIC MAY MAKE CHANGES TO THE

MATERIALS OR TO THE PRODUCTS DESCRIBED THEREIN AT ANY TIME WITHOUT NOTICE.

Trademarks:

is a registrated trademark of Genesys Logic Inc..

All trademarks are the properties of their respective owners.

Office:

Genesys Logic, Inc.

12F, No. 205, Sec. 3, Beishin Rd., Shindian City,

Taipei, Taiwan

Tel: (886-2) 8913-1888

Fax: (886-2) 6629-6168

http://www.genesyslogic.com

GL850 USB 2.0 4-Port HUB Controller

©2000-2003

Genesys

Logic

Inc.--All

rights

reserved. Page

3

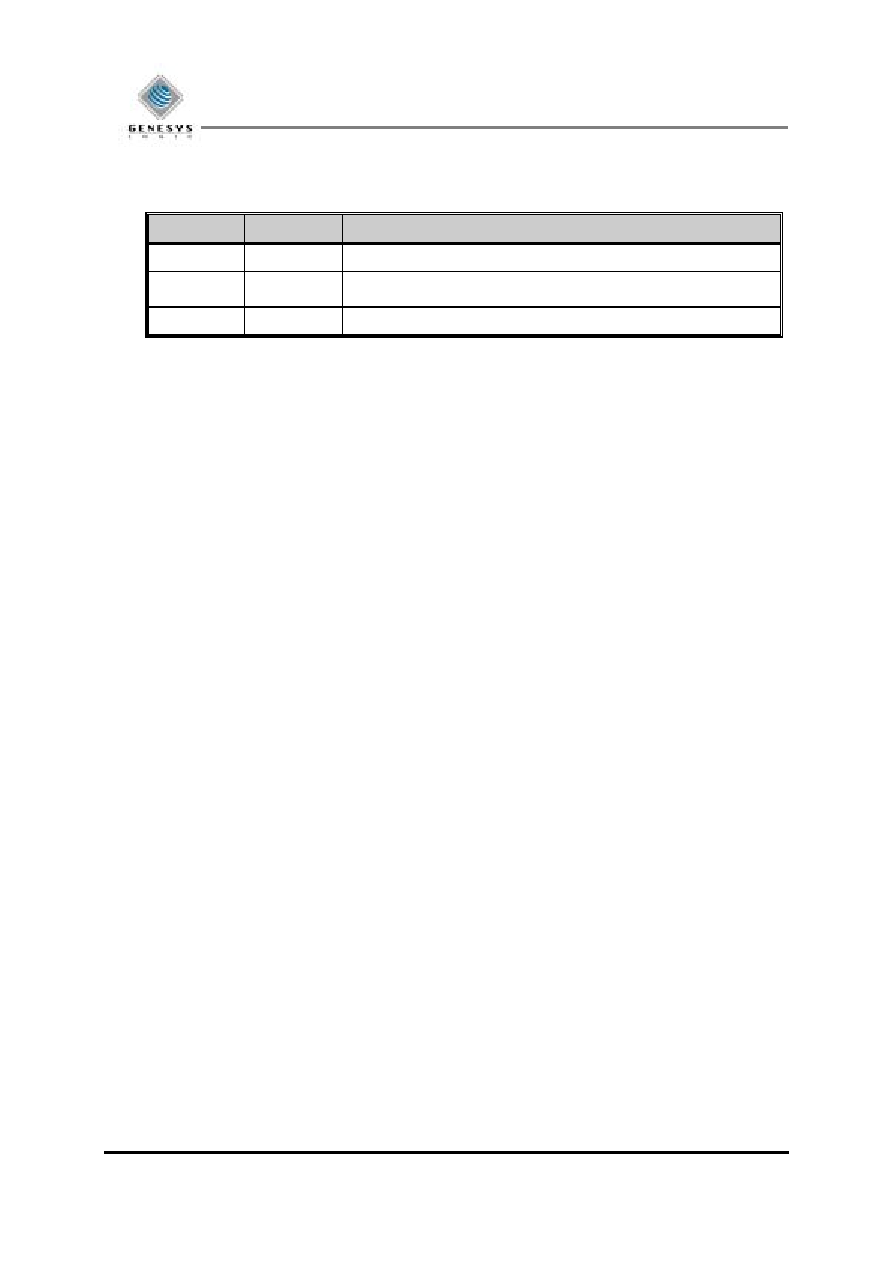

Revision History

Revision

Date

Description

1.00

05/22/2003 First formal release

1.10 06/11/2003

Add Bus Power statement

Gang/Individual mode setting modified

1.11 06/25/2003

Add "4 port" bus power statement

GL850 USB 2.0 4-Port HUB Controller

©2000-2003

Genesys

Logic

Inc.--All

rights

reserved. Page

4

TABLE OF CONTENTS

CHAPTER 1 GENERAL DESCRIPTION........................................................................ 9

CHAPTER 2 FEATURES ................................................................................................. 10

CHAPTER 3 PIN ASSIGNMENT.................................................................................... 11

3.1 P

INOUTS

....................................................................................................................... 11

3.2 P

IN

L

IST

........................................................................................................................ 12

3.3 P

IN

D

ESCRIPTIONS

....................................................................................................... 13

CHAPTER 4 BLOCK DIAGRAM................................................................................... 15

CHAPTER 5 FUNCTION DESCRIPTION .................................................................... 16

5.1 G

ENERAL

...................................................................................................................... 16

5.1.1 USPORT Transceiver......................................................................................... 16

5.1.2 PLL (Phase Lock Loop) ..................................................................................... 16

5.1.3 FRTIMER ........................................................................................................... 16

5.1.4 µC ......................................................................................................................... 16

5.1.5 UTM (USB2.0 Transceiver Macrocell Interface) ............................................ 16

5.1.6 USPORT logic ..................................................................................................... 16

5.1.7 SIE (Serial Interface Engine)............................................................................. 16

5.1.8 Control/Status register ....................................................................................... 16

5.1.9 REPEATER ........................................................................................................ 17

5.1.10 TT (Transaction Translator) ........................................................................... 17

5.1.11 REPEATER/TT routing logic ......................................................................... 17

5.1.11.1 Connected to 1.1 Host/Hub ...................................................................... 17

5.1.11.2 Connected to USB2.0 Host/Hub .............................................................. 18

5.1.12 DSPORT logic ................................................................................................... 18

5.1.13 DSPORT Transceiver....................................................................................... 18

5.2 C

ONFIGURATION AND

I/O S

ETTINGS

.......................................................................... 19

5.2.1 RESET# Setting .................................................................................................. 19

5.2.2 PGANG/SUSPND Setting .................................................................................. 20

5.2.3 SELF/BUS Power Setting .................................................................................. 21

5.2.4 LED Connections................................................................................................ 22

5.2.5 EEPROM Setting................................................................................................ 22

5.3 USB P

ROTOCOLS

......................................................................................................... 23

GL850 USB 2.0 4-Port HUB Controller

©2000-2003

Genesys

Logic

Inc.--All

rights

reserved. Page

5

5.3.1 Host Commands and Hub Answers .................................................................. 24

5.3.1.1 Standard Requests ...................................................................................... 24

5.3.1.2 Hub Class Requests .................................................................................... 25

5.4 D

ESCRIPTORS

............................................................................................................... 27

5.4.1 Full Speed Case................................................................................................... 27

5.4.1.1 Device Descriptor........................................................................................ 27

5.4.1.2 Device Qualifier Descriptor ....................................................................... 28

5.4.1.3 Configuration Descriptor ........................................................................... 28

5.4.1.4 Interface Descriptor.................................................................................... 29

5.4.1.5 Endpoint Descriptor ................................................................................... 29

5.4.1.6 Other Speed Configuration Descriptor..................................................... 30

5.4.1.7 Interface Descriptor combined with Other Speed Configuration

Descriptor .................................................................................................... 30

5.4.1.8 Endpoint Descriptor combined with Other Speed Configuration

Descriptor .................................................................................................... 31

5.4.1.9 String Descriptor......................................................................................... 31

5.4.2 High Speed Case ................................................................................................. 32

5.4.2.1 Device Descriptor........................................................................................ 32

5.4.2.2 Device Qualifier Descriptor ....................................................................... 33

5.4.2.3 Configuration Descriptor ........................................................................... 33

5.4.2.4 Interface Descriptor.................................................................................... 34

5.4.2.5 Endpoint Descriptor in Configuration Descriptor .................................. 34

5.4.2.6 Other Speed Configuration Descriptor..................................................... 35

5.4.2.7 Interface Descriptor in Other Speed Configuration Descriptor............. 35

5.4.2.8 Endpoint Descriptor in Other Speed Configuration Descriptor ............ 36

5.4.2.9 String Descriptor......................................................................................... 36

5.4.3 Hub Class Descriptor ......................................................................................... 37

CHAPTER 6 ELECTRICAL CHARACTERISTICS .................................................... 38

6.1 M

AXIMUM

R

ATINGS

.................................................................................................... 38

6.2 DC C

HARACTERISTICS

................................................................................................ 38

CHAPTER 7 PACKAGE DIMENSION.......................................................................... 40