DS07-13728-3E

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontroller

CMOS

F

2

MC-16LX MB90455 Series

MB90F455 (S) /F456 (S) /F457 (S)

MB90455 (S) /456 (S) /457 (S) /V495G

s

DESCRIPTION

MB90455 series devices are general-purpose high-performance 16-bit micro controllers designed for process

control of consumer products, which require high-speed real-time processing.

The system, inheriting the architecture of F

2

MC* family, employs additional instruction ready for high-level lan-

guages, expanded addressing mode, enhanced multiply-divide instructions, and enriched bit-processing instruc-

tions. Furthermore, employment of 32-bit accumulator achieves processing of long-word data (32 bits).

The peripheral resources of MB90455 series include the following:

8/10-bit A/D converter, UART 1, 8/16-bit PPG timer, 16-bit input-output timer (16-bit free-run timer, input capture

0, 1, 2, 3 (ICU)).

*: "F

2

MC", an abbreviation for FUJITSU Flexible Microcontroller, is a registered trademark of FUJITSU Ltd.

s

FEATURES

·

·

·

·

Clock

· Built-in PLL clock frequency multiplication circuit

· Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and

multiplication of 1 to 4 times of oscillation clock (for 4-MHz oscillation clock, 4 MHz to 16 MHz).

· Operation by sub-clock (8.192 kHz) is allowed.

· Minimum execution time of instruction: 62.5 ns (when operating with 4-MHz oscillation clock, and 4-time multi-

plied PLL clock).

(Continued)

s

PACKAGE

48-pin plastic-LQFP

(FPT-48P-M26)

MB90455 Series

2

·

·

·

·

16 Mbyte CPU memory space

· 24-bit internal addressing

·

·

·

·

Instruction system best suited to controller

· Wide choice of data types (bit, byte, word, and long word)

· Wide choice of addressing modes (23 types)

· Enhanced multiply-divide instructions and RETI instructions

· Enhanced high-precision computing with 32-bit accumulator

·

·

·

·

Instruction system compatible with high-level language (C language) and multitask

· Employing system stack pointer

· Enhanced various pointer indirect instructions

· Barrel shift instructions

·

·

·

·

Increased processing speed

· 4-byte instruction queue

·

·

·

·

Powerful interrupt function with 8 levels and 34 factors

·

·

·

·

Automatic data transfer function independent of CPU

· Expanded intelligent I/O service function (EI

2

OS): Maximum of 16 channels

·

·

·

·

Low power consumption (standby) mode

· Sleep mode (a mode that halts CPU operating clock)

· Time-base timer mode (a mode that operates oscillation clock, sub clock, time-base timer and clock timer only)

· Clock mode (a mode that operates sub clock and clock timer only)

· Stop mode (a mode that stops oscillation clock and sub clock)

· CPU blocking operation mode

·

·

·

·

Process

· CMOS technology

·

·

·

·

I/O port

· General-purpose input/output port (CMOS output): 34 ports(MB90F455/F456/F457, MB90455/456/457) (in-

cluding 4 high-current output ports) (When sub clock is not used, 36 ports(MB90F455S/F456S/F457S,

MB90455S/456S/457S))

·

·

·

·

Timer

· Time-base timer, clock timer, watchdog timer: 1 channel

· 8/16-bit PPG timer: 8-bit x 4 channels, or 16-bit x 2 channels

· 16-bit reload timer: 2 channels

· 16-bit input/output timer

- 16-bit free run timer: 1 channel

- 16-bit input capture: (ICU): 4 channels

Interrupt request is issued upon latching a count value of 16-bit free run timer by detection of an edge on pin

input.

·

·

·

·

UART 1: 1 channel

· Equipped with full-duplex double buffer

· Clock-asynchronous or clock-synchronous serial transmission is available

(Continued)

MB90455 Series

3

(Continued)

·

·

·

·

DTP/External interrupt: 4 channels

· Module for activation of expanded intelligent I/O service (EI

2

OS), and generation of external interrupt.

·

·

·

·

Delay interrupt generator module

· Generates interrupt request for task switching.

·

·

·

·

8/10-bit A/D converter: 8 channels

· Resolution is selectable between 8-bit and 10-bit.

· Activation by external trigger input is allowed.

· Conversion time: 6.125

µ

s (at 16-MHz machine clock, including sampling time)

·

·

·

·

Program patch function

· Address matching detection for 2 address pointers.

MB90455 Series

4

s

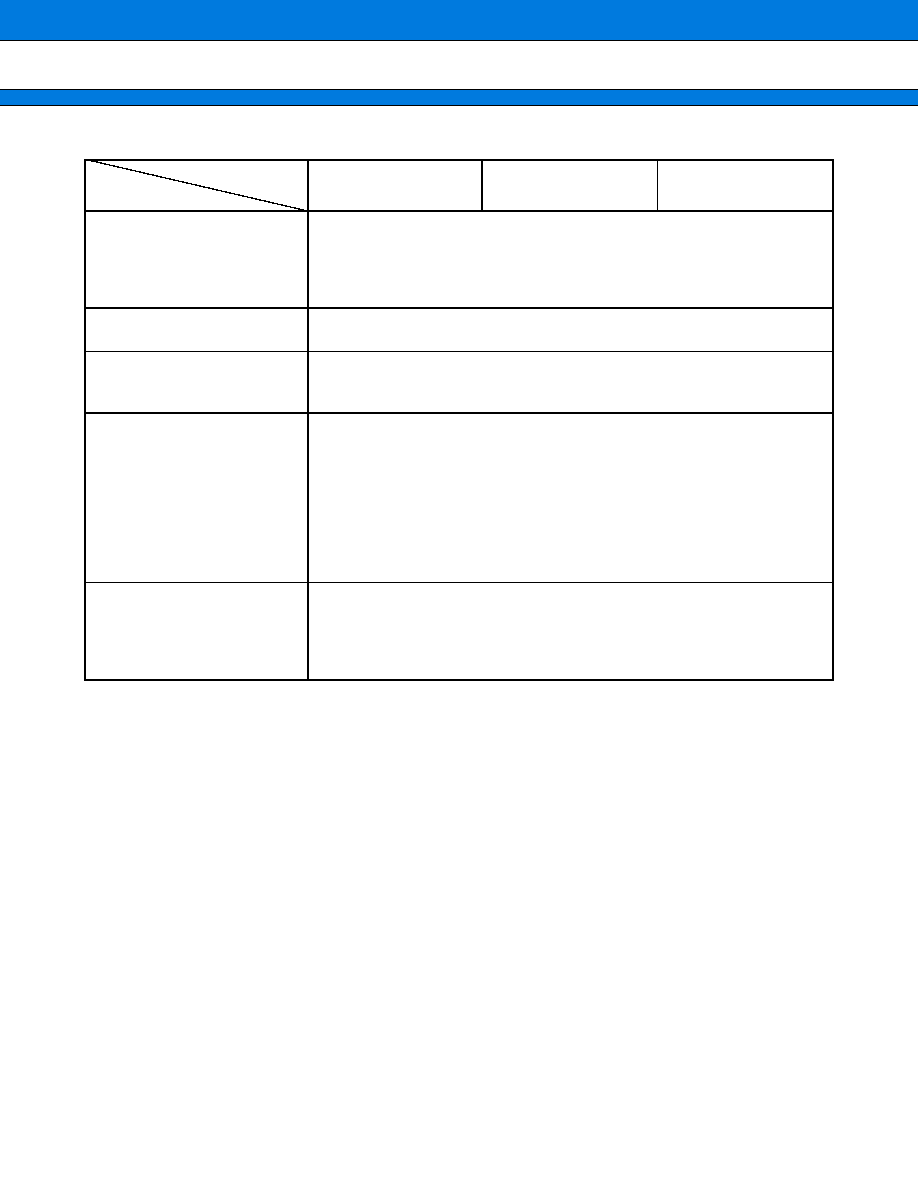

PRODUCT LINEUP

(Continued)

Part Number

MB90F455 (S) /

F456 (S) /F457 (S)

MB90455 (S) /

456 (S) /457 (S)

MB90V495G

Parameter

Classification

Flash ROM

Mask ROM

Evaluation product

ROM capacity

MB90F455 (S) : 24 Kbytes

MB90F456 (S) : 32 Kbytes

MB90F457 (S) : 64 Kbytes

MB90455 (S) : 24 Kbytes

MB90456 (S) : 32 Kbytes

MB90457 (S) : 64 Kbytes

RAM capacity

2 Kbytes

6 Kbytes

Clock

MB90F455/F456/F457 :

2 systems

MB90F455S/F456S/F457S :

1 system

MB90455/456/457 :

2 systems

MB90455S/456S/457S :

1 system

2 systems

Process

CMOS

Package

LQFP-48 (0.50 mm width)

PGA256

Operating power supply voltage

3.5 V to 5.5 V

4.5 V

to

5.5 V

Special power supply for

emulator*

1

None

CPU functions

Number of basic instructions

Instruction bit length

Instruction length

Data bit length

: 351 instructions

: 8 bits and 16 bits

: 1 byte to 7 bytes

: 1 bit, 8 bits, 16 bits

Minimum instruction execution time : 62.5 ns (at 16-MHz machine clock)

Interrupt processing time : 1.5

µ

s at minimum (at 16-MHz machine clock)

Low power consumption

(standby) mode

Sleep mode/Clock mode/Time-base timer mode/

Stop mode/CPU intermittent

I/O port

General-purpose input/output ports (CMOS output) : 34 ports (36 ports*

2

)

including 4 high-current output ports (P14 to P17)

Time-base timer

18-bit free-run counter

Interrupt cycle : 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms

(with oscillation clock frequency at 4 MHz)

Watchdog timer

Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms

(with oscillation clock frequency at 4 MHz)

16-bit input/

output timer

16-bit free-run

timer

Number of channels: 1

Interrupt upon occurrence of overflow

Input capture

Number of channels: 4

Retaining free-run timer value set by pin input (rising edge, falling edge, and

both edges)

16-bit reload timer

Number of channels: 2

16-bit reload timer operation

Count clock cycle: 0.25

µ

s, 0.5

µ

s, 2.0

µ

s

(at 16-MHz machine clock frequency)

External event count is allowed.

Clock timer

15-bit free-run counter

Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s

(with 8.192 kHz sub clock)

MB90455 Series

5

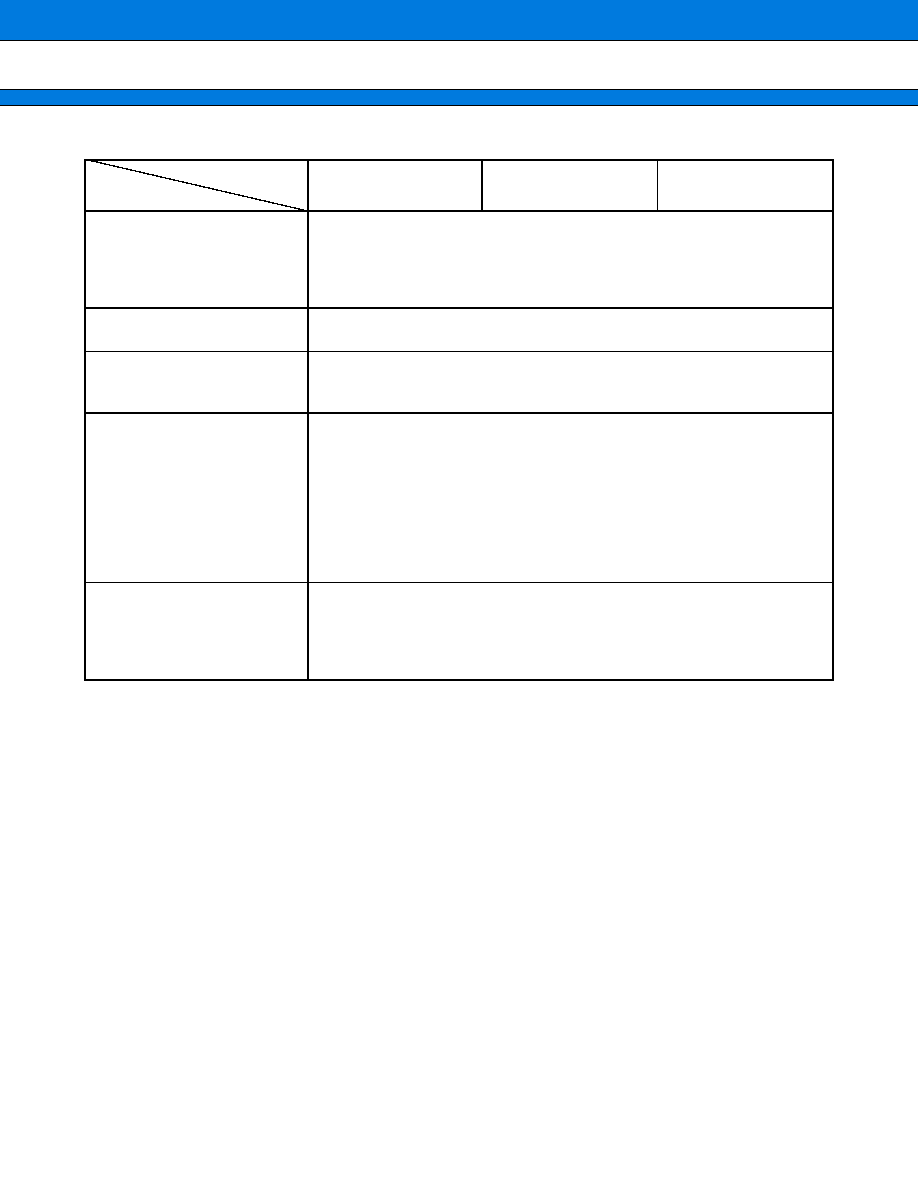

(Continued)

*1 : Settings of DIP switch S2 for using emulation pod MB2145-507. For details, See MB2145-507 Hardware Manual

(2.7 Power Pin solely for Emulator).

*2 : MB90F455S/F456S/F457S, MB90455S/456S/457S

Part Number

MB90F455 (S) /

F456 (S) /F457 (S)

MB90455 (S) /

456 (S) /457 (S)

MB90V495G

Parameter

8/16-bit PPG timer

Number of channels: 2 (four 8-bit channels are available also)

PPG operation is allowed with four 8-bit channels or one 16-bit channel.

Outputting pulse wave of arbitrary cycle or arbitrary duty is allowed.

Count clock: 62.5 ns to 1

µ

s

(with 16 MHz machine clock)

Delay interrupt generator

module

Interrupt generator module for task switching. Used for Real-time OS.

DTP/External interrupt

Number of inputs: 4

Activated by rising edge, falling edge, "H" level or "L" level input.

External interrupt or expanded intelligent I/O service (EI

2

OS) is available.

8/10-bit A/D converter

Number of channels: 8

Resolution: Selectable 10-bit or 8-bit.

Conversion time: 6.125

µ

s (at 16-MHz machine clock, including sampling time)

Sequential conversion of two or more successive channels is allowed. (Setting

a maximum of 8 channels is allowed.)

Single conversion mode

: Selected channel is converted only once.

Sequential conversion mode: Selected channel is converted repetitively.

Halt conversion mode

: Conversion of selected channel is stopped and

activated alternately.

UART 1

Number of channels: 1

Clock-synchronous transfer: 62.5 Kbps to 2 Mbps

Clock-asynchronous transfer: 9,615 bps to 500 Kbps

Communication is allowed by bi-directional serial communication function and

master/slave type connection.