DS05-50103-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

MCP (Multi-Chip Package) FLASH MEMORY & SRAM

CMOS

16M (

×

8) FLASH MEMORY &

2M (

×

8) STATIC RAM

MB84VA2100

-10

/MB84VA2101

-10

s

FEATURES

· Power supply voltage of 2.7 to 3.6 V

· High performance

100 ns maximum access time

· Operating Temperature

20 to +85

°

C

-- FLASH MEMORY

· Minimum 100,000 write/erase cycles

· Sector erase architecture

One 16 K byte, two 8 K bytes, one 32 K byte, and thirty one 64 K bytes.

Any combination of sectors can be concurrently erased. Also supports full chip erase.

· Boot Code Sector Architecture

MB84VA2100: Top sector

MB84VA2101: Bottom sector

· Embedded Erase

TM

Algorithms

Automatically pre-programs and erases the chip or any sector

· Embedded Program

TM

Algorithms

Automatically writes and verifies data at specified address

· Data Polling and Toggle Bit feature for detection of program or erase cycle completion

· Ready-Busy output (RY/BY)

Hardware method for detection of program or erase cycle completion

· Automatic sleep mode

When addresses remain stable, automatically switch themselves to low power mode.

· Low V

CC

write inhibit

2.5 V

· Erase Suspend/Resume

Suspends the erase operation to allow a read in another sector within the same device

Please refer to "MBM29LV160T/B" data sheet in detailed function

-- SRAM

· Power dissipation

Operating : 35 mA max.

Standby : 50

µ

A max.

· Power down features using CE1s and CE2s

· Data retention supply voltage: 2.0 V to 3.6 V

Embedded Erase

TM

and Embedded Program

TM

are trademarks of Advanced Micro Devices, Inc.

3

MB84VA2100

-10

/MB84VA2101

-10

s

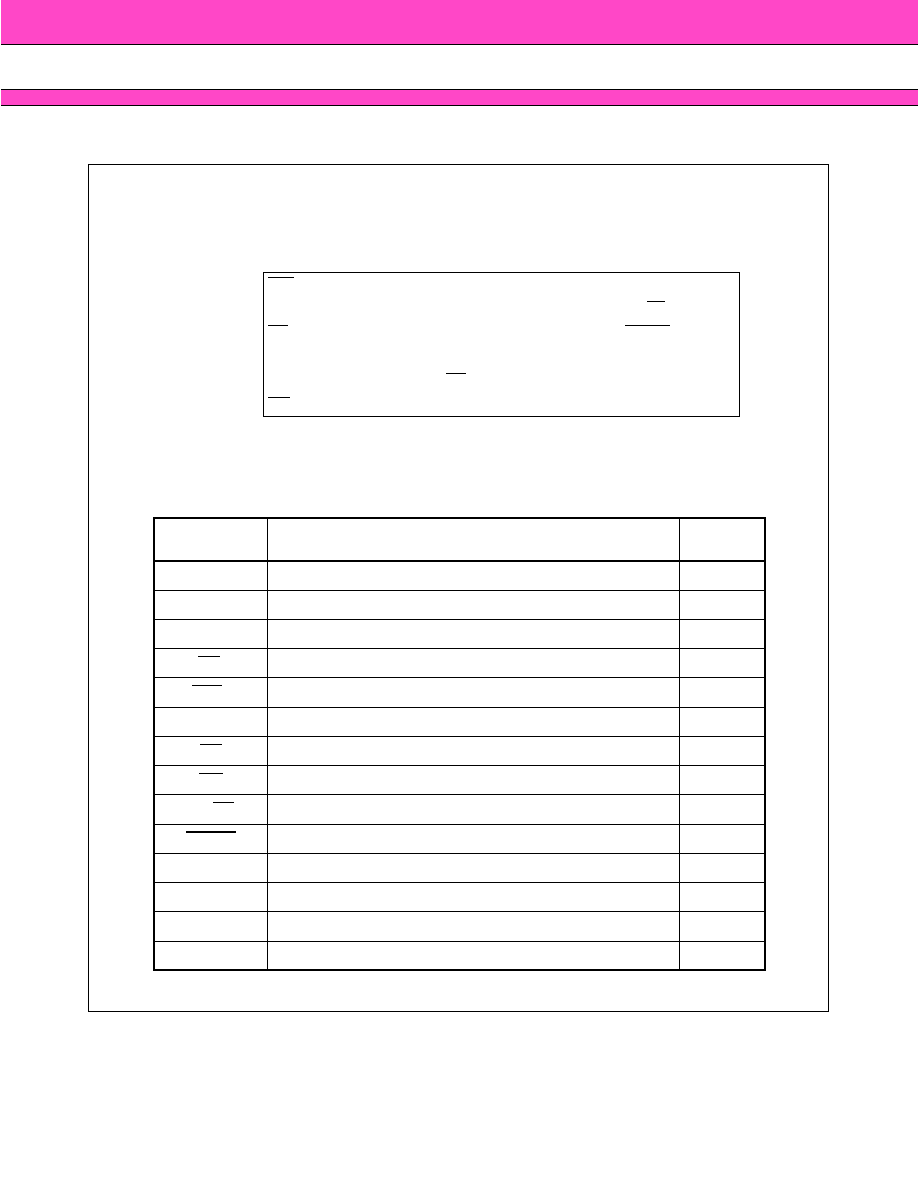

PIN ASSIGNMENTS

(Top View)

A

B

C

D

E

F

G

H

6

CE1s

V

SS

DQ

1

A

1

A

2

A

4

CE2s

A

9

5

A

10

DQ

5

DQ

2

A

0

A

3

A

7

RY/BY

A

15

4

OE

DQ

7

DQ

4

DQ

0

A

6

A

19

RESET

A

16

3

A

11

A

8

A

5

N.C.

DQ

3

N.C.

A

13

A

20

2

A

14

A

18

N.C.

CEf

N.C.

V

CC

f

DQ

6

A

12

1

WE

V

CC

s

A

17

V

SS

N.C.

N.C.

N.C.

N.C.

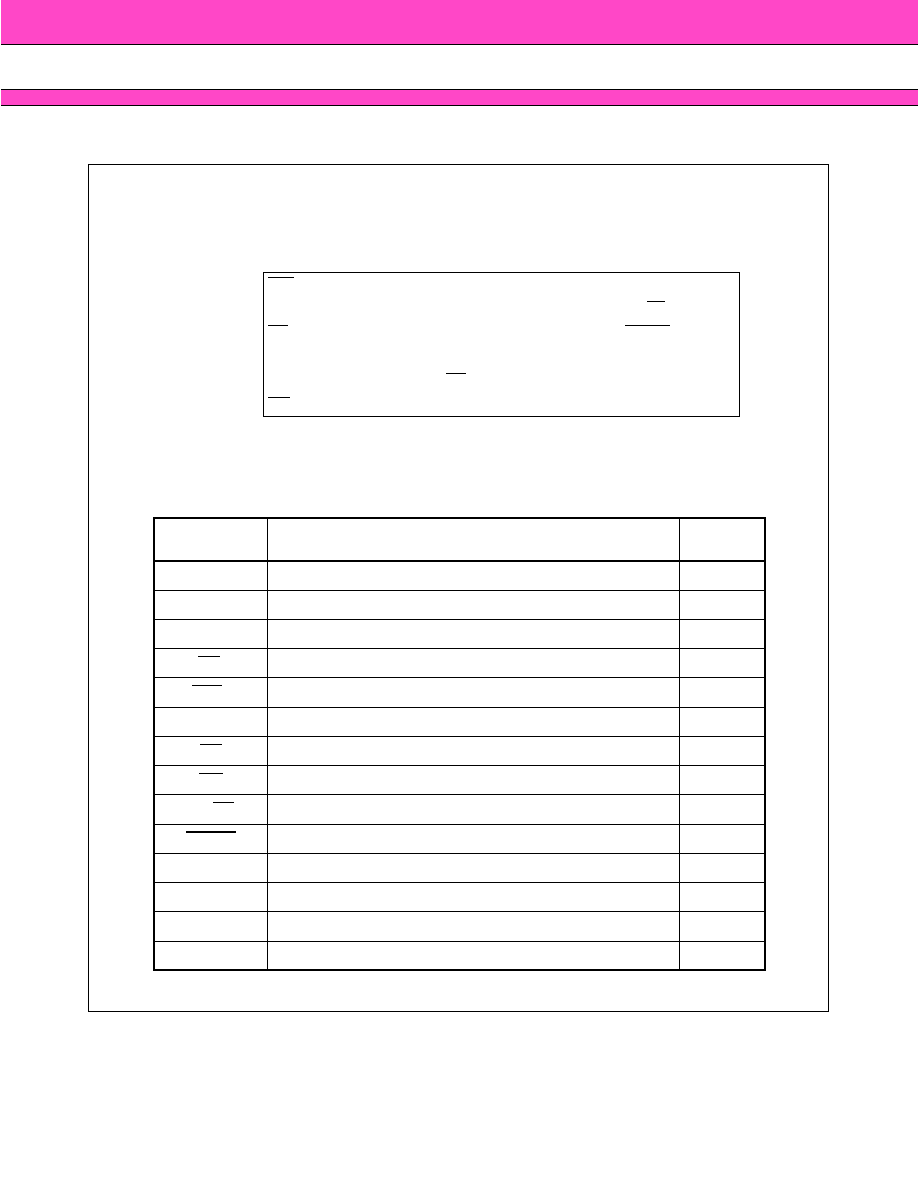

Table 1 Pin Configuration

Pin

Function

Input/

Output

A

0

to A

17

Address Inputs (Common)

I

A

18

to A

20

Address Input (Flash)

I

DQ

0

to DQ

7

Data Inputs/Outputs (Common)

I/O

CEf

Chip Enable (Flash)

I

CE1s

Chip Enable (SRAM)

I

CE2s

Chip Enable (SRAM)

I

OE

Output Enable (Common)

I

WE

Write Enable (Common)

I

RY/BY

Ready/Busy Outputs (Flash)

O

RESET

Hardware Reset Pin/Sector Protection Unlock (Flash)

I

N.C.

No Internal Connection

--

V

SS

Device Ground (Common)

Power

V

CC

f

Device Power Supply (Flash)

Power

V

CC

s

Device Power Supply (SRAM)

Power

4

MB84VA2100

-10

/MB84VA2101

-10

s

PRODUCT LINE UP

s

BUS OPERATIONS

Legend: L = V

IL

, H = V

IH

, X = V

IL

or V

IH

. See DC Characteristics for voltage levels.

Notes: 1. Other operations except for indicated this column are inhibited.

2. WE can be V

IL

if OE is V

IL

, OE at V

IH

initiates the write operations.

3. Do not apply CEf = V

IL

, CE1s = V

IL

and CE2s = V

IH

at a time.

Flash Memory

SRAM

Ordering Part No.

V

CC

= 3.0 V

MB84VA2100-10/MB84VA2101-10

Max. Address Access Time (ns)

100

100

Max. CE Access Time (ns)

100

100

Max. OE Access Time (ns)

40

50

Table 2 User Bus Operations

Operation (1), (3)

CEf

CE1s

CE2s

OE

WE

DQ

0

to DQ

7

RESET

Full Standby

H

H

X

X

X

HIGH-Z

H

X

L

Output Disable

X

X

X

H

H

HIGH-Z

H

Read from Flash (2)

L

H

X

L

H

D

OUT

H

X

L

Write to Flash

L

H

X

H

L

D

IN

H

X

L

Read from SRAM

H

L

H

L

H

D

OUT

H

Write to SRAM

H

L

H

X

L

D

IN

H

Flash Hardware Reset

X

H

X

X

X

HIGH-Z

L

X

L

+0.6 V

0.3 V

5

MB84VA2100

-10

/MB84VA2101

-10

s

FLEXIBLE SECTOR-ERASE ARCHITECTURE on FLASH MEMORY

· One 16 K byte, two 8 K bytes, one 32 K byte, and thirty one 64 K bytes.

Individual-sector, multiple-sector, or bulk-erase capability.

.

MB84VA2100 Sector Architecture

Sector Size

Address Range

64 Kbytes

00000H to 0FFFFH

64 Kbytes

10000H to 1FFFFH

64 Kbytes

20000H to 2FFFFH

64 Kbytes

30000H to 3FFFFH

64 Kbytes

40000H to 4FFFFH

64 Kbytes

50000H to 5FFFFH

64 Kbytes

60000H to 6FFFFH

64 Kbytes

70000H to 7FFFFH

64 Kbytes

80000H to 8FFFFH

64 Kbytes

90000H to 9FFFFH

64 Kbytes

A0000H to AFFFFH

64 Kbytes

B0000H to BFFFFH

64 Kbytes

C0000H to CFFFFH

64 Kbytes

D0000H to DFFFFH

64 Kbytes

E0000H to EFFFFH

64 Kbytes

F0000H to FFFFFH

64 Kbytes

100000H to 10FFFFH

64 Kbytes

110000H to 11FFFFH

64 Kbytes

120000H to 12FFFFH

64 Kbytes

130000H to 13FFFFH

64 Kbytes

140000H to 14FFFFH

64 Kbytes

150000H to 15FFFFH

64 Kbytes

160000H to 16FFFFH

64 Kbytes

170000H to 17FFFFH

64 Kbytes

180000H to 18FFFFH

64 Kbytes

190000H to 19FFFFH

64 Kbytes

1A0000H to 1AFFFFH

64 Kbytes

1B0000H to 1BFFFFH

64 Kbytes

1C0000H to 1CFFFFH

64 Kbytes

1D0000H to 1DFFFFH

64 Kbytes

1E0000H to 1EFFFFH

32 Kbytes

1F0000H to 1F7FFFH

8 Kbytes

1F8000H to 1F9FFFH

8 Kbytes

1FA000H to 1FBFFFH

16 Kbytes

1FC000H to 1FFFFFH

MB84VA2101 Sector Architecture

Sector Size

Address Range

16 Kbytes

00000H to 03FFFH

8 Kbytes

04000H to 05FFFH

8 Kbytes

06000H to 07FFFH

32 Kbytes

08000H to 0FFFFH

64 Kbytes

10000H to 1FFFFH

64 Kbytes

20000H to 2FFFFH

64 Kbytes

30000H to 3FFFFH

64 Kbytes

40000H to 4FFFFH

64 Kbytes

50000H to 5FFFFH

64 Kbytes

60000H to 6FFFFH

64 Kbytes

70000H to 7FFFFH

64 Kbytes

80000H to 8FFFFH

64 Kbytes

90000H to 9FFFFH

64 Kbytes

A0000H to AFFFFH

64 Kbytes

B0000H to BFFFFH

64 Kbytes

C0000H to CFFFFH

64 Kbytes

D0000H to DFFFFH

64 Kbytes

E0000H to EFFFFH

64 Kbytes

F0000H to FFFFFH

64 Kbytes

100000H to 10FFFFH

64 Kbytes

110000H to 11FFFFH

64 Kbytes

120000H to 12FFFFH

64 Kbytes

130000H to 13FFFFH

64 Kbytes

140000H to 14FFFFH

64 Kbytes

150000H to 15FFFFH

64 Kbytes

160000H to 16FFFFH

64 Kbytes

170000H to 17FFFFH

64 Kbytes

180000H to 18FFFFH

64 Kbytes

190000H to 19FFFFH

64 Kbytes

1A0000H to 1AFFFFH

64 Kbytes

1B0000H to 1BFFFFH

64 Kbytes

1C0000H to 1CFFFFH

64 Kbytes

1D0000H to 1DFFFFH

64 Kbytes

1E0000H to 1EFFFFH

64 Kbytes

1F0000H to 1FFFFFH