Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

©2002 Fairchild Semiconductor Corporation

RFG60P05E Rev. B

RFG60P05E

60A, 50V, 0.030 Ohm, ESD Rated,

P-Channel Power MOSFET

This is a P-Channel power MOSFET manufactured using the

MegaFET process. This process, which uses feature sizes

approaching those of LSI circuits, gives optimum utilization

of silicon, resulting in outstanding performance. It was

designed for use in applications such as switching

regulators, switching converters, motor drivers, and relay

drivers. This type can be operated directly from integrated

circuits.

Formerly developmental type TA09835.

Features

· 60A, 50V

· r

DS(ON)

= 0.030

· Temperature Compensating PSPICE

®

Model

· 2kV ESD Rated

· Peak Current vs Pulse Width Curve

· UIS Rating Curve

· 175

o

C Operating Temperature

· Related Literature

- TB334 "Guidelines for Soldering Surface Mount

Components to PC Boards"

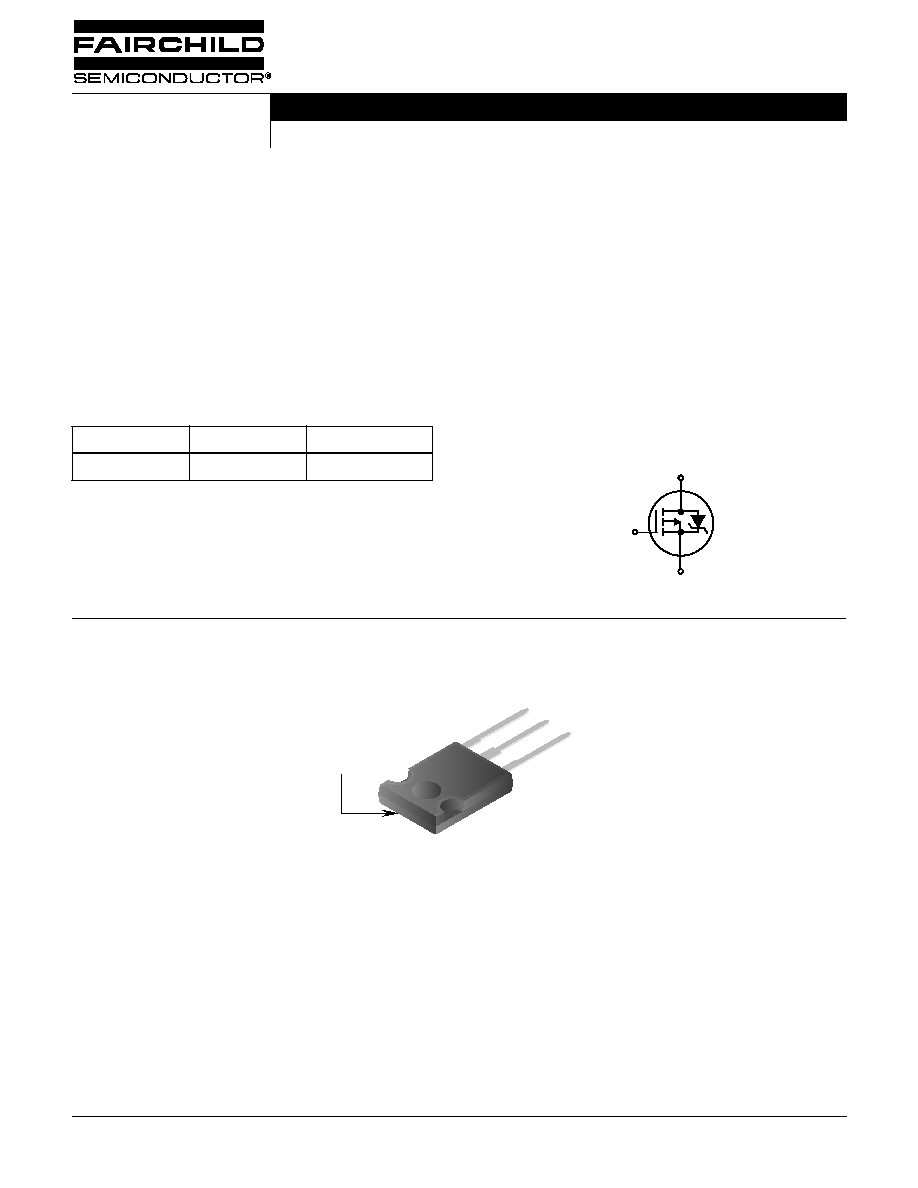

Symbol

Packaging

JEDEC STYLE TO-247

Ordering Information

PART NUMBER

PACKAGE

BRAND

RFG60P05E

TO-247

RFG60P05E

NOTE:

When ordering, use the entire part number.

D

G

S

DRAIN

(BOTTOM

SIDE METAL)

SOURCE

DRAIN

GATE

Data Sheet

January 2002

©2002 Fairchild Semiconductor Corporation

RFG60P05E Rev. B

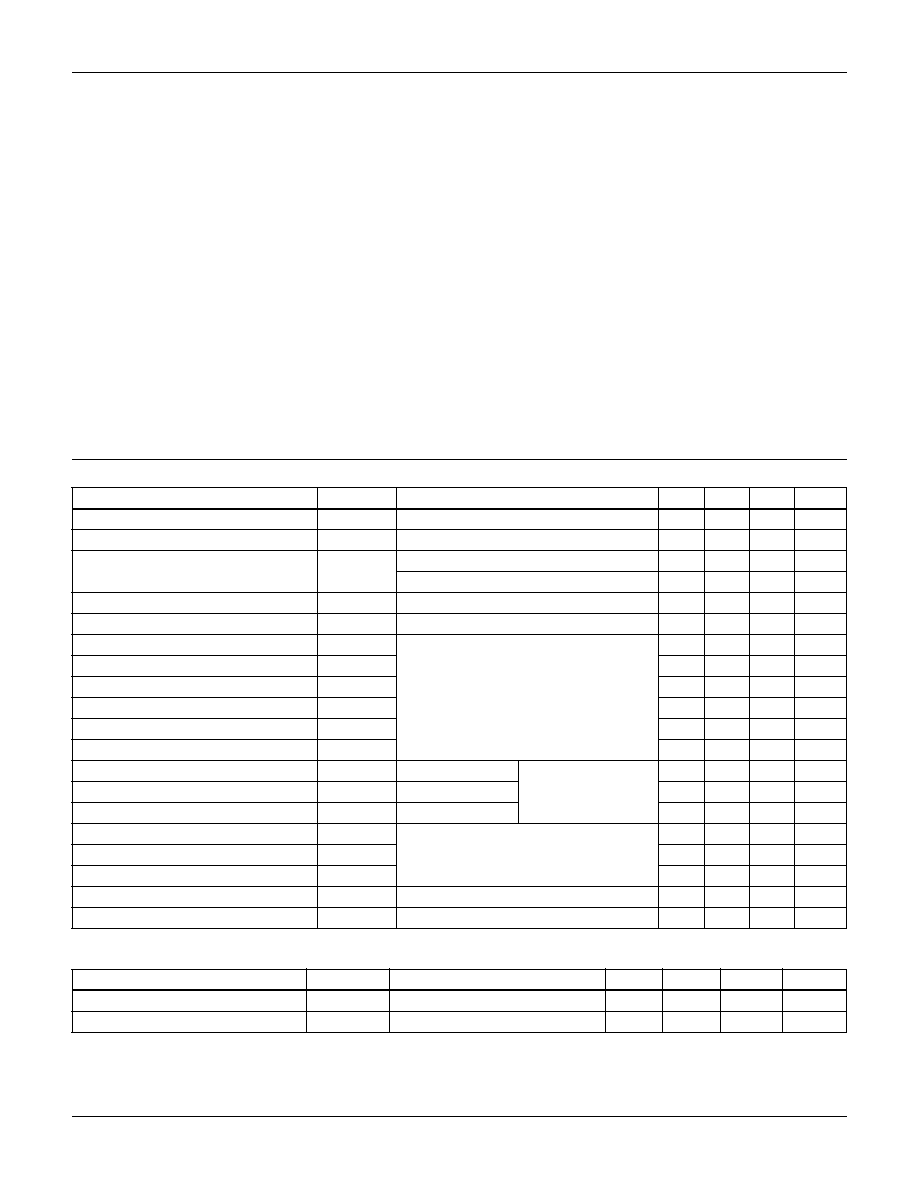

Absolute Maximum Ratings

T

C

= 25

o

C, Unless Otherwise Specified

RFG60P05E

UNITS

Drain to Source Breakdown Voltage (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DS

-50

V

Drain to Gate Voltage (R

GS

= 20k

) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DGR

-50

V

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

GS

±

20

V

Continuous Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

D

Pulsed Drain Current (Note 3) (Figure 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .I

DM

60

Refer to Peak Current Curve

A

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . P

D

Derate above 25

o

C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

215

1.43

W

W/

o

C

Single Pulse Avalanche Rating (Figure 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E

AS

Refer to UIS Curve

W/

o

C

Electrostatic Discharge Rating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E

SD

MIL-STD-883, Category B(2)

2

kV

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .T

J,

T

STG

-55 to 175

o

C

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .T

L

Package Body for 10s, See Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

pkg

300

260

o

C

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. T

J

= 25

o

C to 150

o

C.

Electrical Specifications

T

C

= 25

o

C, Unless Otherwise Specified

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Drain to Source Breakdown Voltage

BV

DSS

I

D

= 250

µ

A, V

GS

= 0V

-50

-

-

V

Gate Threshold Voltage

V

GS(TH)

V

GS

= V

DS

, I

D

= 250

µ

A

-2

-

-4

V

Zero Gate Voltage Drain Current

I

DSS

V

DS

= -50V, V

GS

= 0V

-

-

-1

µ

A

V

DS

= 0.8 x Rated BV

DSS

, T

C

= 150

o

C

-

-

-25

µ

A

Gate to Source Leakage Current

I

GSS

V

GS

=

±

20V

-

-

±

100

nA

Drain to Source On Resistance (Note 2)

r

DS(ON)

I

D

= 60A, V

GS

= -10V (Figure 9)

-

-

0.030

Turn-On Time

t

(ON)

V

DD

= -25V, I

D

= 30A, R

L

= 0.83

,

V

GS

= -10V, R

GS

= 2.5

(Figure 13)

-

-

125

ns

Turn-On Delay Time

t

d(ON)

-

20

-

ns

Rise Time

t

r

-

60

-

ns

Turn-Off Delay Time

t

d(OFF)

-

65

-

ns

Fall Time

t

F

-

20

-

ns

Turn-Off Time

t

(OFF)

-

-

125

ns

Total Gate Charge

Q

g(TOT)

V

GS

= 0V to -20V

V

DD

= -40V, I

D

= 60A,

R

L

= 0.67

I

g(REF)

= -4mA

-

-

450

nC

Gate Charge at 10V

Q

g(-10)

V

GS

= 0V to -10V

-

-

225

nC

Threshold Gate Charge

Q

g(TH)

V

GS

= 0V to -2V

-

-

15

nC

Input Capacitance

C

ISS

V

DS

= -25V, V

GS

= 0V, f = 1MHz

(Figure 12)

-

7200

-

pF

Output Capacitance

C

OSS

-

1700

-

pF

Reverse Transfer Capacitance

C

RSS

-

325

-

pF

Thermal Resistance, Junction to Case

R

JC

-

-

0.70

o

C/W

Thermal Resistance, Junction to Ambient

R

JA

-

-

30

o

C/W

Source to Drain Diode Specifications

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Source to Drain Diode Voltage (Note 2)

V

SD

I

SD

= -60A

-

-

-1.75

V

Diode Reverse Recovery Time

t

RR

I

SD

= -60A, dI

SD

/dt = 100A/

µ

s

-

-

200

ns

NOTE:

2. Pulse test: pulse width

300

µ

s maximum, duty cycle

2%.

3. Repetitive rating: pulse width limited by maximum junction temperature. See Transient Thermal Impedance curve (Figure 3).

RFG60P05E

©2002 Fairchild Semiconductor Corporation

RFG60P05E Rev. B

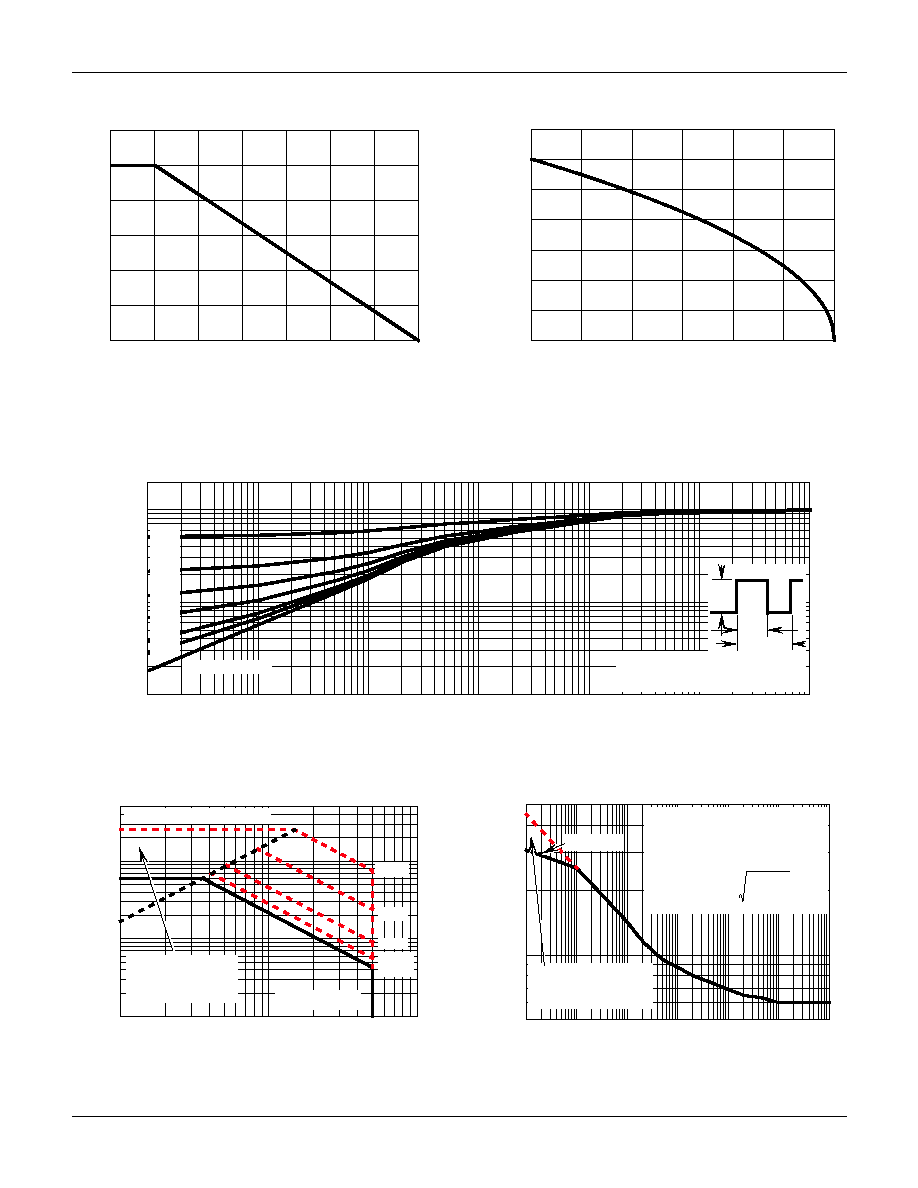

Typical Performance Curves

Unless Otherwise Specified

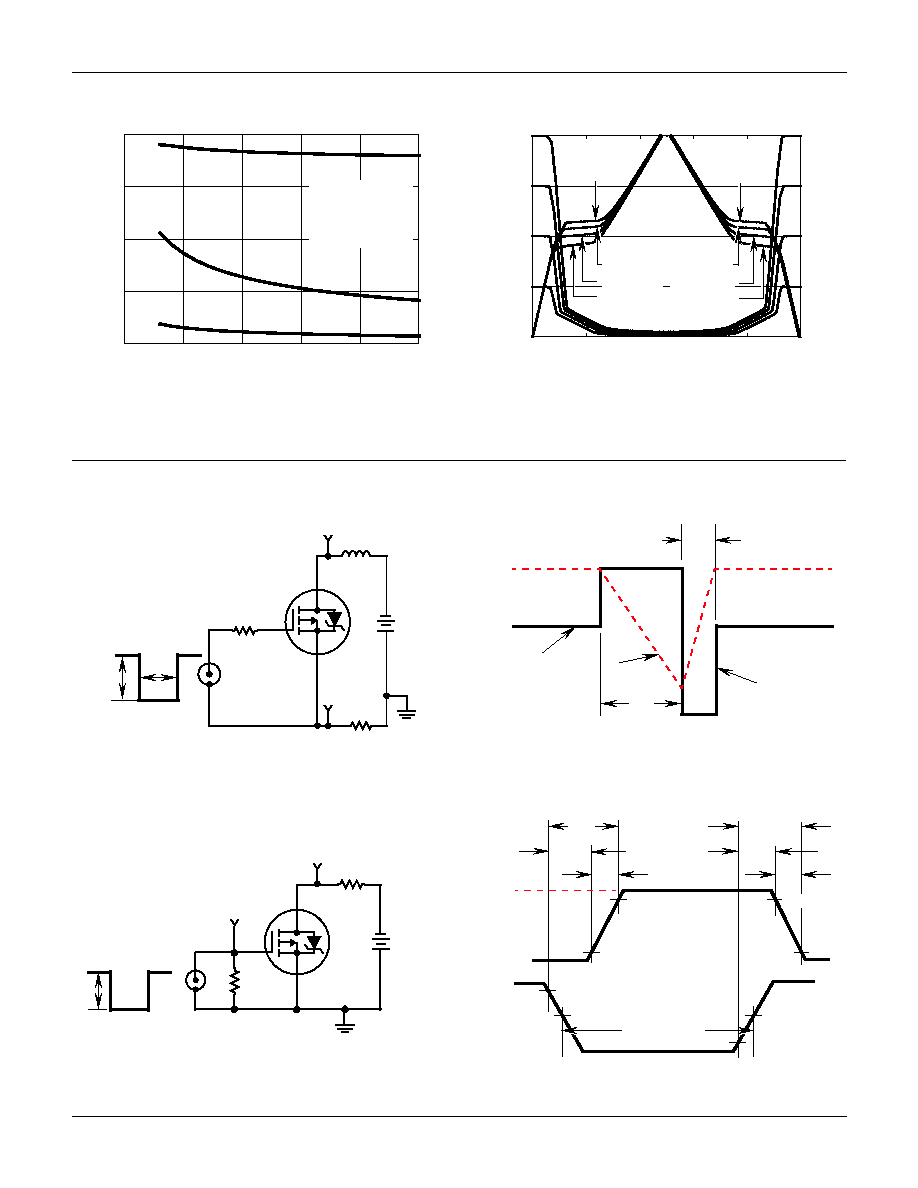

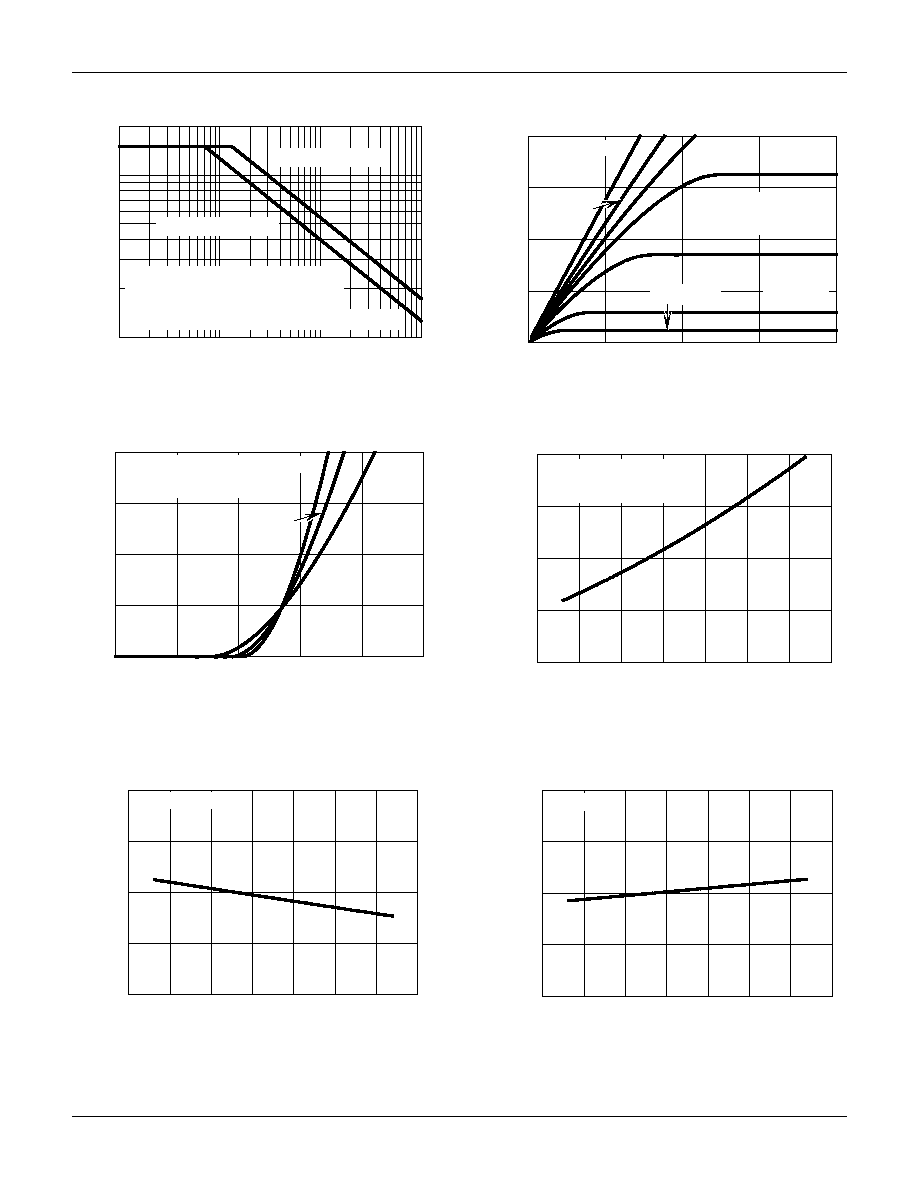

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE

TEMPERATURE

FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

CASE TEMPERATURE

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

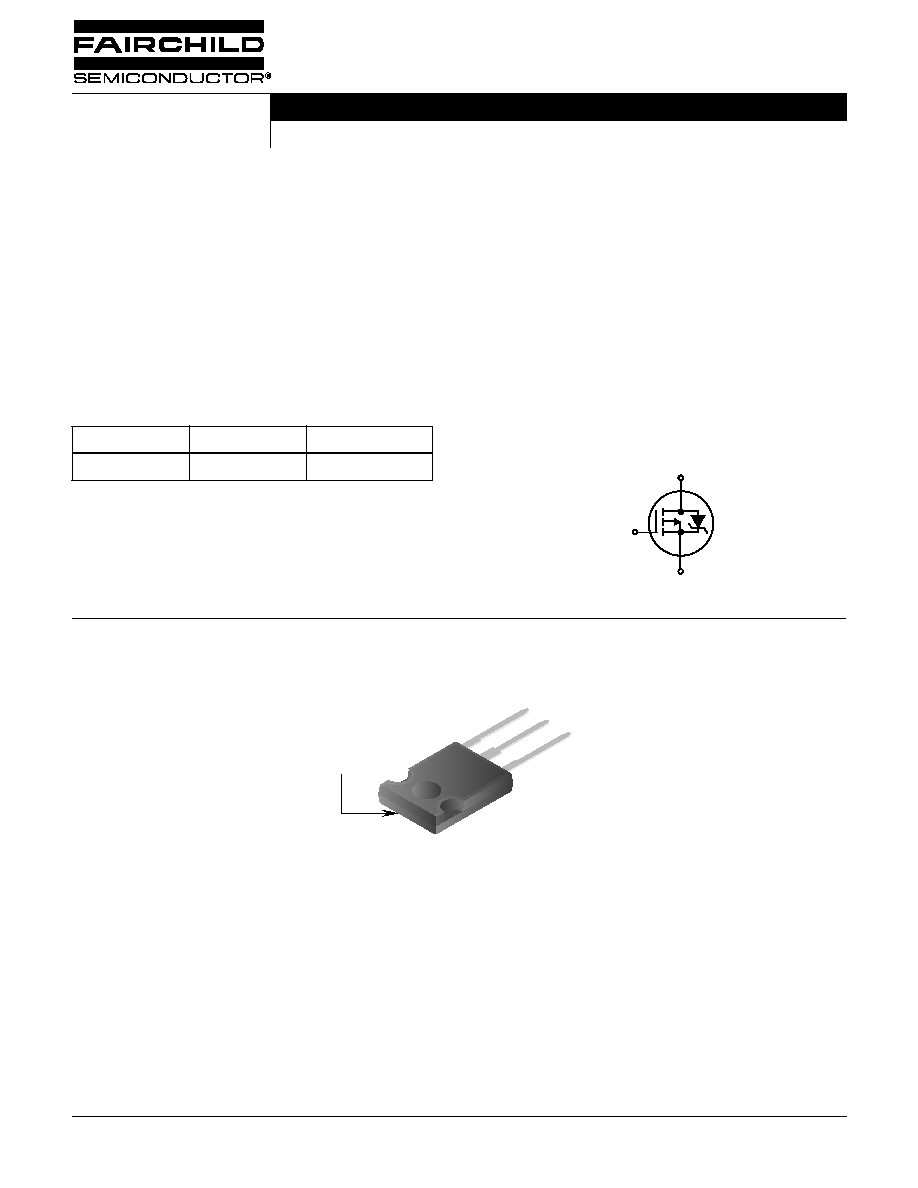

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA

FIGURE 5. PEAK CURRENT CAPABILITY

T

C

, CASE TEMPERATURE (

o

C)

PO

WER DISSIP

A

TION MUL

TIPLIER

0

0

25

50

75

100

175

0.2

0.4

0.6

0.8

1.0

1.2

125

150

-50

-40

-30

-20

-10

0

25

50

75

100

125

150

175

I

D

,

DRAIN CURRENT (A)

T

C

,

CASE TEMPERATURE (

o

C)

-60

-70

2

1

0.1

0.01

10

-5

10

-4

10

-3

10

-2

10

-1

10

0

10

1

THERMAL IMPED

ANCE

Z

JC

,

NORMALIZED

TRANSIENT

SINGLE PULSE

0.01

0.02

0.05

0.1

0.2

0.5

NOTES:

DUTY FACTOR: D = t

1

/t

2

PEAK T

J

= P

DM

x Z

JC

x R

JC

+ T

C

P

DM

t

1

t

2

t, RECTANGULAR PULSE DURATION (s)

-500

-100

-10

-1

-1

-10

-100

V

DS

,

DRAIN TO SOURCE VOLTAGE (V)

I

D

,

DRAIN CURRENT (A)

V

DSS

MAX = -50V

OPERATION IN THIS

AREA MAY BE

LIMITED BY r

DS(ON)

1ms

10ms

100ms

DC

100ms

T

C

= 25

o

C, T

J

= MAX RATED

10

-5

10

-4

10

-3

10

-2

10

-1

10

0

10

1

-100

-500

t, PULSE WIDTH (s)

I

DM

,

PEAK CURRENT (A)

-50

FOR TEMPERATURES ABOVE 25

o

C

DERATE PEAK CURRENT

CAPABILITY AS FOLLOWS:

I

I

25

175

T

C

150

---------------------

=

TRANSCONDUCTANCE

MAY LIMIT CURRENT

IN THIS REGION

V

GS

= -10V

T

C

= 25

o

C

RFG60P05E

©2002 Fairchild Semiconductor Corporation

RFG60P05E Rev. B

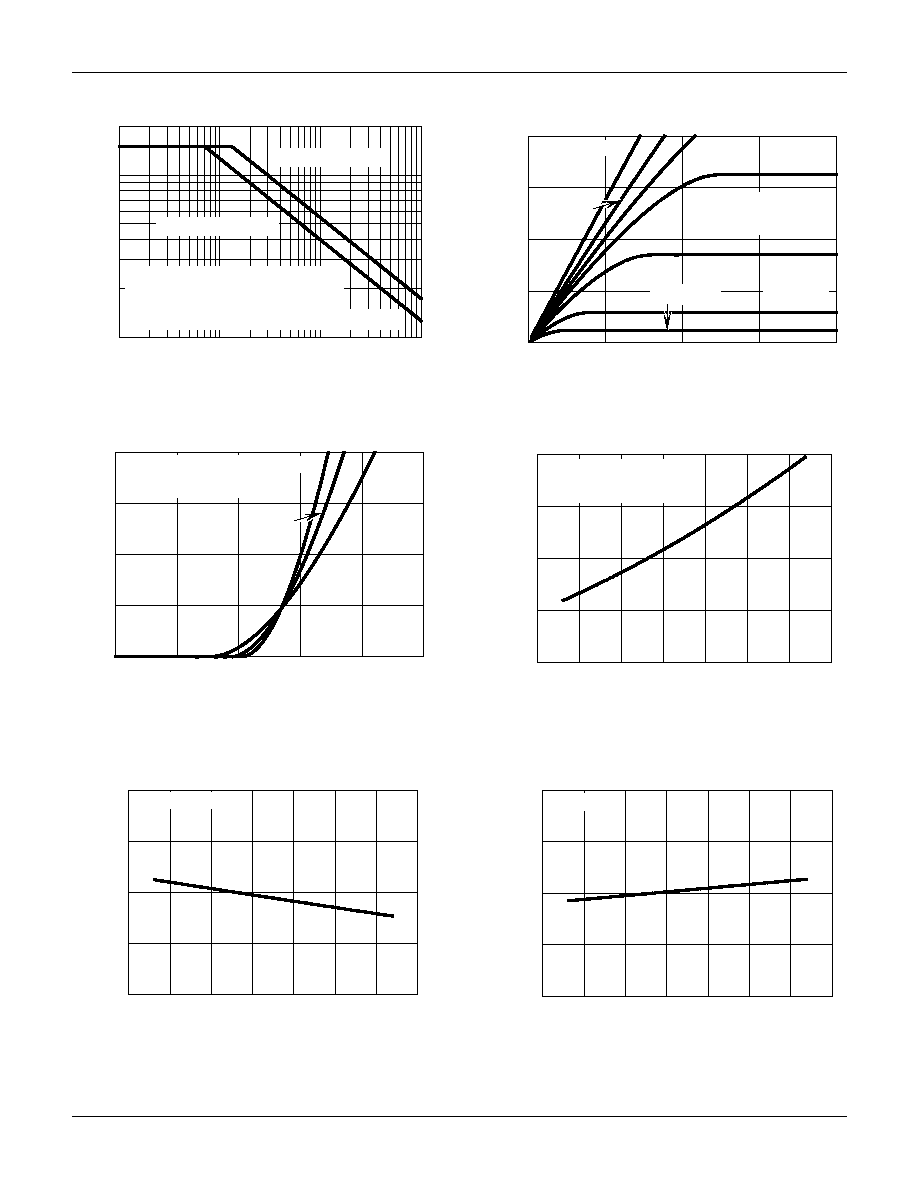

NOTE: Refer to Fairchild Application Notes AN9321 and AN9322.

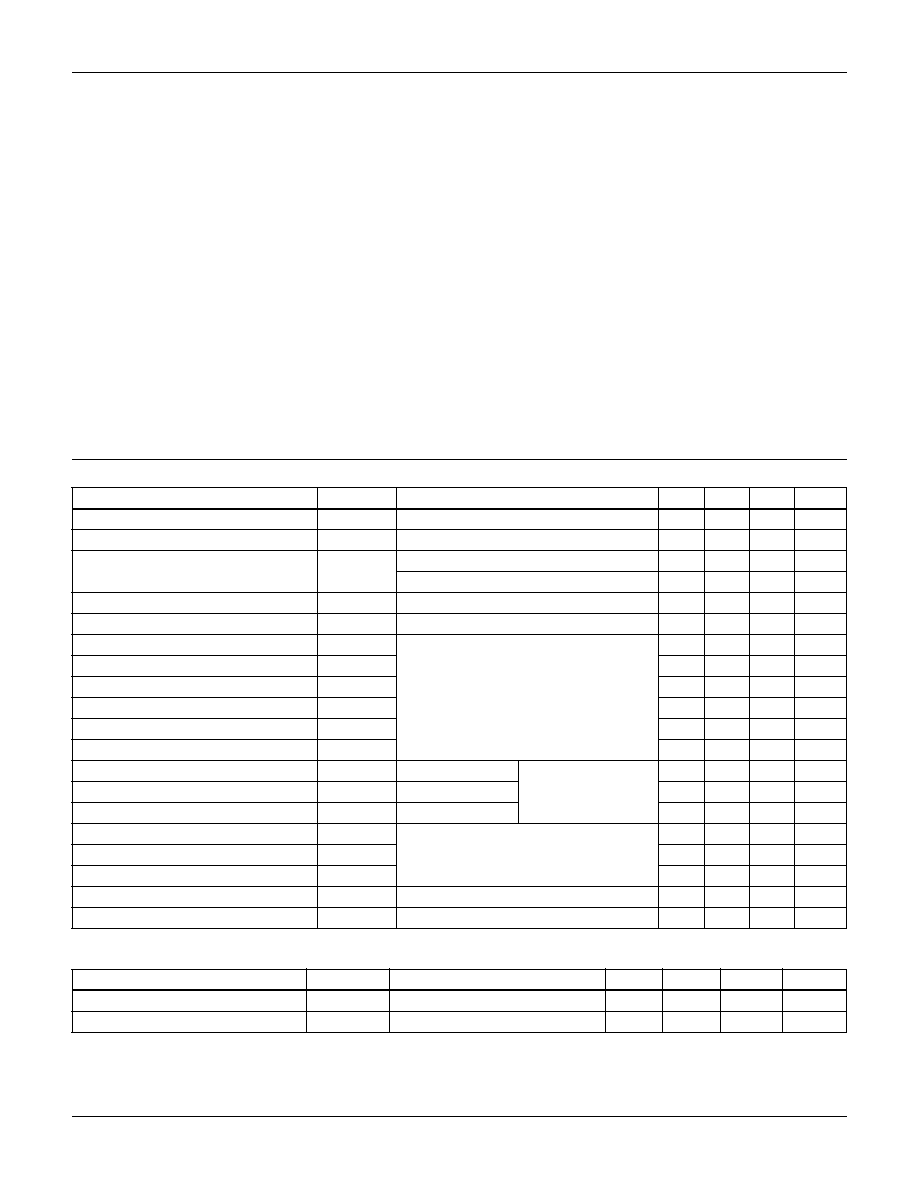

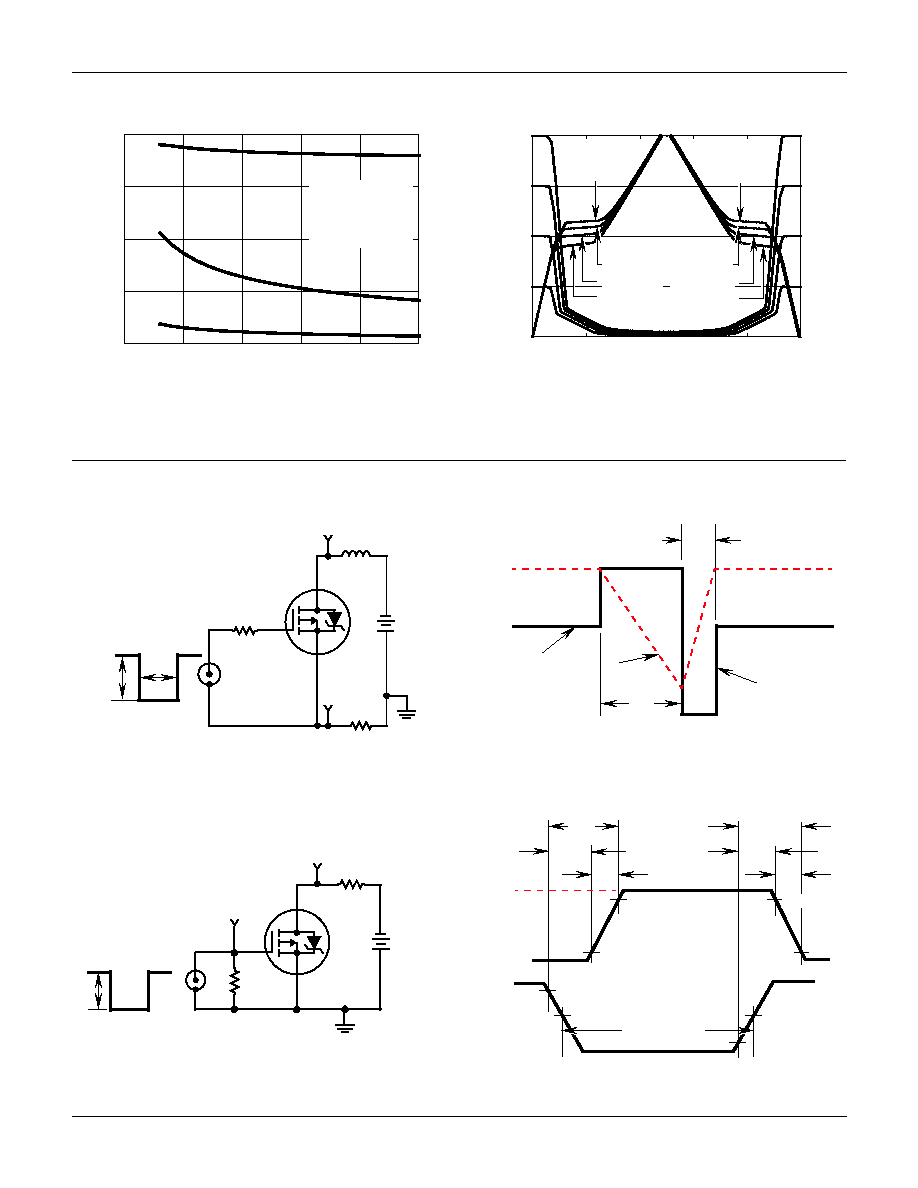

FIGURE 6. UNCLAMPED INDUCTIVE SWITCHING CAPABILITY

FIGURE 7. SATURATION CHARACTERISTICS

FIGURE 8. TRANSFER CHARACTERISTICS

FIGURE 9. NORMALIZED DRAIN TO SOURCE ON

RESISTANCE vs JUNCTION TEMPERATURE

FIGURE 10. NORMALIZED GATE THRESHOLD VOLTAGE vs

JUNCTION TEMPERATURE

FIGURE 11. NORMALIZED DRAIN TO SOURCE BREAKDOWN

VOLTAGE vs JUNCTION TEMPERATURE

Typical Performance Curves

Unless Otherwise Specified (Continued)

-200

-100

-10

0.01

0.1

1

10

t

AV

,

TIME IN AVALANCHE (ms)

I

AS

,

A

V

ALANCHE CURRENT (A)

If R = 0

t

AV

= (L) (I

AS

) / (1.3RATED BV

DSS

- V

DD

)

If R

0

t

AV

= (L/R) ln [(I

AS

*R) / (1.3 RATED BV

DSS

- V

DD

) + 1]

STARTING T

J

= 150

o

C

STARTING T

J

= 25

o

C

0

0

-2

-4

-6

-8

I

D

,

DRAIN CURRENT (A)

V

DS

, DRAIN TO SOURCE VOLTAGE (V)

V

GS

= -8V

V

GS

= -7V

V

GS

= -10V

-40

-80

-120

-160

V

GS

= -20V

V

GS

= -6V

V

GS

= -5V

V

GS

= -4.5V

PULSE DURATION = 80

µs

T

C

= 25

o

C

DUTY CYCLE = 0.5% MAX

0

-2

-4

-6

-8

-10

V

GS

, GATE TO SOURCE VOLTAGE (V)

I

DS(ON)

,

DRAIN

T

O

SOURCE CURRENT (A)

0

175

o

C

25

o

C

-40

-80

-160

-120

PULSE DURATIONM = 80

µs

DUTY CYCLE = 0.5% MAX

-55

o

C

V

DD

= -15V

2

1.5

1

0.5

0

-80

-40

0

40

80

120

160

200

T

J

,

JUNCTION TEMPERATURE (

o

C)

NORMALIZED DRAIN

T

O

SOURCE

PULSE DURATION = 80

µs

V

GS

= -10V, I

D

= 60A

ON RESIST

ANCE

DUTY CYCLE = 0.5% MAX

2

1.5

1

0.5

0

-80

-40

0

40

80

160

120

200

THRESHOLD

V

O

L

T

A

GE

T

J

, JUNCTION TEMPERATURE (

o

C)

NORMALIZED GA

TE

V

GS

= V

DS

, I

D

= 250

µA

2

1.5

1

0.5

0

-80

-40

0

40

80

120

160

200

NORMALIZED DRAIN

T

O

SOURCE

BREAKDO

WN V

O

L

T

A

GE

T

J

, JUNCTION TEMPERATURE (

o

C)

I

D

= 250

µA

RFG60P05E

©2002 Fairchild Semiconductor Corporation

RFG60P05E Rev. B

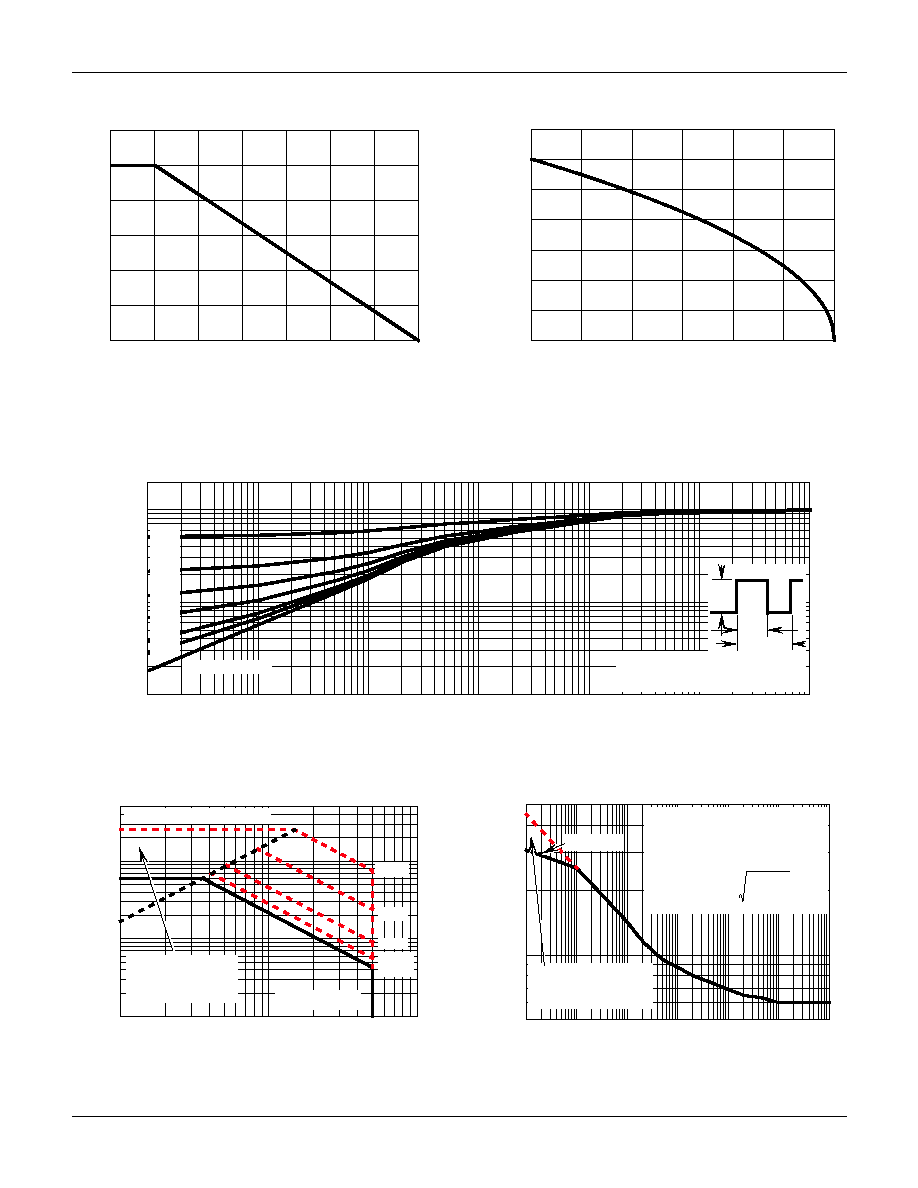

FIGURE 12. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE

NOTE: Refer to Fairchild Application Notes AN7254 and AN7260.

FIGURE 13. NORMALIZED SWITCHING WAVEFORMS FOR

CONSTANT GATE CURRENT

Test Circuits and Waveforms

FIGURE 14. UNCLAMPED ENERGY TEST CIRCUIT

FIGURE 15. UNCLAMPED ENERGY WAVEFORMS

FIGURE 16. SWITCHING TIME TEST CIRCUIT

FIGURE 17. RESISTIVE SWITCHING WAVEFORMS

Typical Performance Curves

Unless Otherwise Specified (Continued)

C

ISS

C

OSS

C

RSS

6000

4000

2000

0

0

-10

-15

-20

-25

C

,

CAP

A

CIT

ANCE (pF)

V

DS

,

DRAIN TO SOURCE VOLTAGE

(V)

8000

-5

V

GS

= 0V, f = 1MHz

C

ISS

= C

GS

+ C

GD

C

RSS

= C

GD

C

OSS

C

DS

+ C

GS

-50

-37.5

-25

-12.5

0

-10

-7.5

-5

-2.5

0

V

DD

= BV

DSS

V

DD

= BV

DSS

V

DS

,

DRAIN

T

O

SOURCE

V

O

L

T

A

GE (V)

V

GS

,

GA

TE

T

O

SOURCE

V

O

L

T

A

GE (V)

20

I

G REF

(

)

I

G ACT

(

)

-------------------------

t, TIME (

µs)

80

I

G REF

(

)

I

G ACT

(

)

-------------------------

R

L

= 0.83

I

G(REF)

= 4mA

V

GS

= -10V

0.75 BV

DSS

0.50 BV

DSS

0.25 BV

DSS

0.75 BV

DSS

0.50 BV

DSS

0.25 BV

DSS

t

P

0.01

L

I

AS

+

-

V

DS

V

DD

R

G

DUT

VARY t

P

TO OBTAIN

REQUIRED PEAK I

AS

0V

V

GS

V

DD

V

DS

BV

DSS

t

P

I

AS

t

AV

0

V

GS

R

L

R

GS

DUT

+

-

V

DD

V

DS

V

GS

t

d(ON)

t

r

90%

10%

V

DS

90%

t

f

t

d(OFF)

t

OFF

90%

50%

50%

10%

PULSE WIDTH

V

GS

t

ON

10%

0

0

RFG60P05E