E

Copyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

DS87C530

EPROM Micro with Real Time Clock

DS87C530

PRELIMINARY

022197 1/40

FEATURES

·

80C52 Compatible

8051 Instruction set

Four 8bit I/O ports

Three 16bit timer/counters

256 bytes scratchpad RAM

·

Large Onchip Memory

16KB EPROM (OTP)

1KB extra onchip SRAM for MOVX

·

ROMSIZE

TM

Feature

Selects effective onchip ROM size from

0 to 16KB

Allows access to entire external memory map

Dynamically adjustable by software

Useful as boot block for external Flash

·

Nonvolatile Functions

Onchip Real Time Clock w/ Alarm Interrupt

Battery backup support of 1KB SRAM

·

HighSpeed Architecture

4 clocks/machine cycle (8051 = 12)

Runs DC to 33 MHz clock rates

Singlecycle instruction in 121 ns

Dual data pointer

Optional variable length MOVX to access

fast/slow RAM /peripherals

·

Power Management Mode

Programmable clock source saves power

Runs from (crystal/64) or (crystal/1024)

Provides automatic hardware and software exit

·

EMI Reduction Mode disables ALE

·

High integration controller includes:

Powerfail reset

Earlywarning powerfail interrupt

Programmable Watchdog timer

·

Two fullduplex hardware serial ports

·

14 total interrupt sources with 6 external

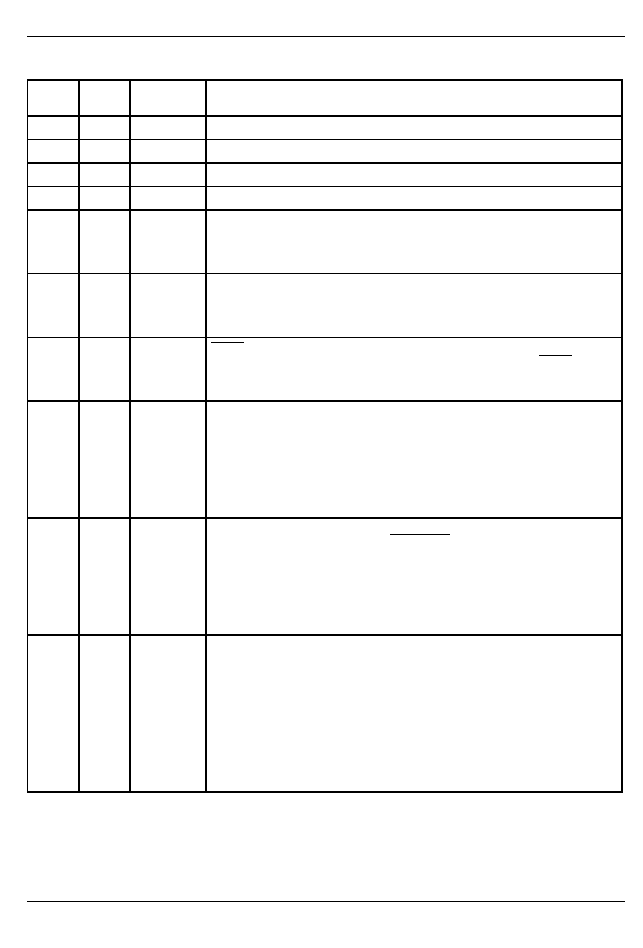

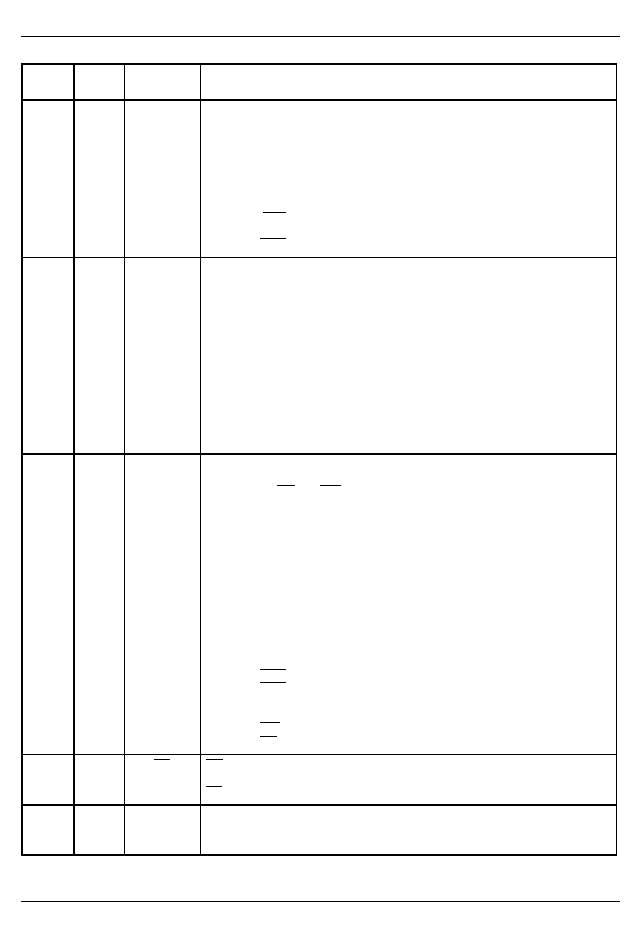

PACKAGE OUTLINE

DALLAS

DS87C530

52PIN PLCC

52PIN CER QUAD

1

47

7

21

33

8

20

34

46

52

13

14

26

27

39

40

52PIN TQFP OUTLINE

DALLAS

DS87C530

DESCRIPTION

The DS87C530 is an 8051 compatible microcontroller

based on the Dallas High Speed core. It uses four clocks

per instruction cycle instead of 12 used by the standard

8051. It also provides a unique mix of peripherals not

widely available on other processors. They include an

onchip Real Time Clock (RTC) and battery back up

support for an onchip 1K x 8 SRAM. The new Power

Management Mode allows software to select reduced

power operation while still processing.

DS87C530

022197 2/40

A combination of high performance microcontroller

core, real time clock, battery backed SRAM, and power

management makes the DS87C530 ideal for instru-

ments and portable applications. It also provides sev-

eral peripherals found on other Dallas HighSpeed

Microcontrollers. These include two independent serial

ports, two data pointers, onchip power monitor with

brownout detection and a watchdog timer.

Power Management Mode (PMM) allows software to

select a slower CPU clock. While default operation uses

four clocks per machine cycle, the PMM runs the pro-

cessor at 64 or 1024 clocks per cycle. There is a corre-

sponding drop in power consumption when the proces-

sor slows.

Note: The DS87C530 is a monolithic device. A user

must supply an external battery or supercap and a

32.768 KHz timekeeping crystal to have permanently

powered timekeeping or nonvolatile RAM. The

DS87C530 provides all the support and switching cir-

cuitry needed to manage these resources.

ORDERING INFORMATION

PART NUMBER

PACKAGE

MAX. CLOCK SPEED

TEMPERATURE RANGE

DS87C530QCL

52pin PLCC

33 MHz

0

°

C to 70

°

C

DS87C530QNL

52pin PLCC

33 MHz

40

°

C to +85

°

C

DS87C530KCL

52pin windowed CERQUAD

33 MHz

0

°

C to 70

°

C

DS87C530ECL

52PIN TQFP

33 MHz

0

°

C to 70

°

C

DS87C530ENL

52PIN TQFP

33 MHz

40

°

C to +85

°

C

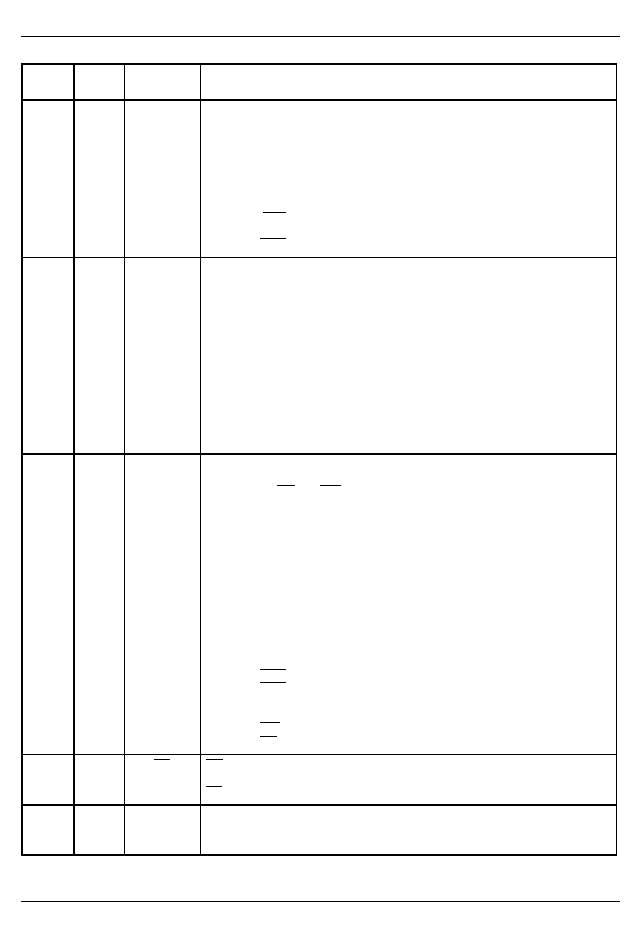

DS87C530 BLOCK DIAGRAM Figure 1

P1.0P1.7

P3.0P3.7

POR

T

1

POR

T

3

INTERRUPT

AD0AD7

P2.0P2.7

CLOCKS AND

LOGIC

MEMORY CONTROL

INTERRUPT REG.

INSTRUCTION

DECODE

PSW

STACK POINTER

ALU REG. 2

B REGISTER

ACCUMULATOR

ALU REG. 1

ALU

V

CC

POWER MONITOR

OSCILLATOR

WATCHDOG TIMER

POWER CONTROL REG.

WATCHDOG REG.

RESET

CONTROL

256 BYTES

SFR 8 RAM

DPTR1

PC ADDR. REG.

BUFFER

PC INCREMENT

PROG. COUNTER

DPTR0

POR

T

0

POR

T

2

TIMER 2

TIMER 1

TIMER 0

POR

T

LA

TCH

SERIAL

POR

T

0

SERIAL

POR

T

1

POR

T

LA

TCH

TIMED

ACCESS

SFR RAM

ADDRESS

POR

T

LA

TCH

ADDRESS BUS

DA

T

A

BUS

GND

XT

AL2

XT

AL1

ALE

PSEN

RST

VCC

POR

T

LA

TCH

16K X 8

OTP

ROM

1K X 8

SRAM

REAL TIME

BATTERY

CONTROL

CLOCK

V

CC

V

BAT

RTCX1 RTCX2

GND

V

CC2

DS87C530

022197 3/40

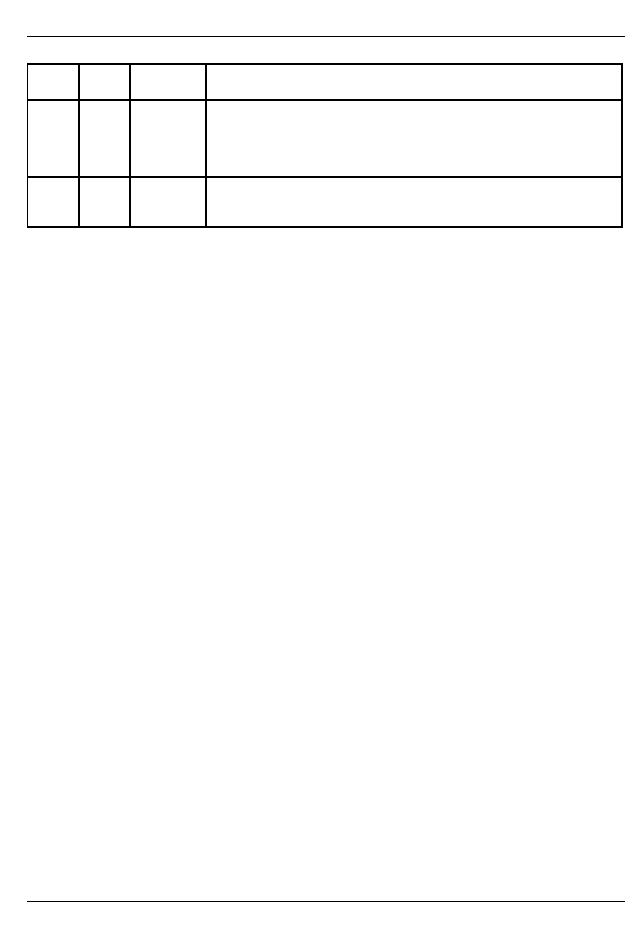

PIN DESCRIPTION Table 1

PLCC

TQFP

SIGNAL

NAME

DESCRIPTION

52

45

V

CC

V

CC

+5V. Processor power supply.

1,25

18, 46

GND

GND Processor digital circuit ground.

29

22

V

CC2

V

CC2

+5V Real Time Clock supply.

26

19

GND2

GND2 Real Time Clock circuit ground.

12

5

RST

RST Input. The RST input pin contains a Schmitt voltage input to recognize

external active high Reset inputs. The pin also employs an internal pulldown

resistor to allow for a combination of wired OR external Reset sources. An RC

is not required for powerup, as the DS87C530 provides this function internally.

23

24

16

17

XTAL2

XTAL1

XTAL1, XTAL2 The crystal oscillator pins XTAL1 and XTAL2 provide support

for parallel resonant, AT cut crystals. XTAL1 acts also as an input if there is an

external clock source in place of a crystal. XTAL2 serves as the output of the

crystal amplifier.

38

31

PSEN

PSEN Output. The Program Store Enable output. This signal is commonly

connected to optional external ROM memory as a chip enable. PSEN will pro-

vide an active low pulse and is driven high when external ROM is not being

accessed.

39

32

ALE

ALE Output. The Address Latch Enable output functions as a clock to latch

the external address LSB from the multiplexed address/data bus on Port 0.

This signal is commonly connected to the latch enable of an external 373 family

transparent latch. ALE has a pulse width of 1.5 XTAL1 cycles and a period of

four XTAL1 cycles. ALE is forced high when the DS87C530 is in a Reset condi-

tion. ALE can be disabled by writing ALEOFF=1 (PMR.Z). When ALEOFF=1,

ALE is forced high. ALE operates independently of ALEOFF during external

memory accesses.

50

49

48

47

46

45

44

43

43

42

41

40

39

38

37

36

P0.0 (AD0)

P0.1 (AD1)

P0.2 (AD2)

P0.3 (AD3)

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

Port 0 (AD07) I/O. Port 0 is an opendrain 8bit bidirectional I/O port. As

an alternate function Port 0 can function as the multiplexed address/data bus

to access offchip memory. During the time when ALE is high, the LSB of a

memory address is presented. When ALE falls to a logic 0, the port transitions

to a bidirectional data bus. This bus is used to read external ROM and read/

write external RAM memory or peripherals. When used as a memory bus, the

port provides active high drivers. The reset condition of Port 0 is tristate.

Pullup resistors are required when using Port 0 as an I/O port.

310

4852,

13

P1.0 P1.7

Port 1 I/O. Port 1 functions as both an 8bit bidirectional I/O port and an

alternate functional interface for Timer 2 I/O, new External Interrupts, and new

Serial Port 1. The reset condition of Port 1 is with all bits at a logic 1. In this state,

a weak pullup holds the port high. This condition also serves as an input

mode, since any external circuit that writes to the port will overcome the weak

pullup. When software writes a 0 to any port pin, the DS87C530 will activate

a strong pulldown that remains on until either a 1 is written or a reset occurs.

Writing a 1 after the port has been at 0 will cause a strong transition driver to

turn on, followed by a weaker sustaining pullup. Once the momentary strong

driver turns off, the port again becomes the output high (and input) state. The

alternate modes of Port 1 are outlined as follows.

DS87C530

022197 4/40

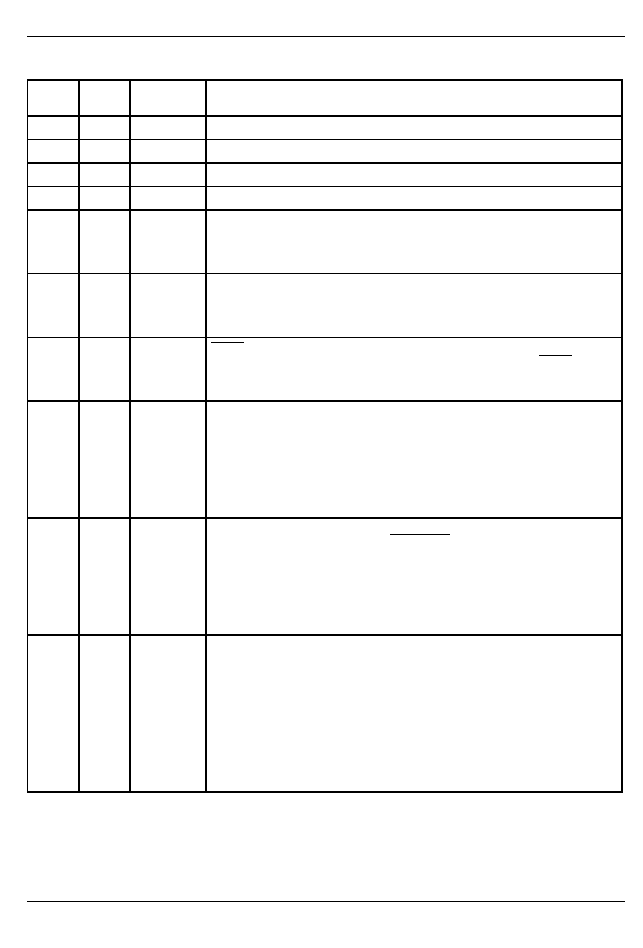

PLCC

DESCRIPTION

SIGNAL

NAME

TQFP

3

4

5

6

7

8

9

10

48

49

50

51

52

1

2

3

Port

Alternate

Function

P1.0

T2

External I/O for Timer/Counter 2

P1.1

T2EX

Timer/Counter 2 Capture/Reload Trigger

P1.2

RXD1

Serial Port 1 Input

P1.3

TXD1

Serial Port 1 Output

P1.4

INT2

External Interrupt 2 (Positive Edge Detect)

P1.5

INT3

External Interrupt 3 (Negative Edge Detect)

P1.6

INT4

External Interrupt 4 (Postive Edge Detect)

P1.7

INT5

External Interrupt 5 (Negative Edge Detect)

30

31

32

33

34

35

36

37

23

24

25

26

27

28

29

30

P2.0 (AD8)

P2.1 (AD9)

P2.2

(AD10)

P2.3

(AD11)

P2.4

(AD12)

P2.5

(AD13)

P2.6

(AD14)

P2.7

(AD15)

Port 2 (A815) I/O. Port 2 is a bidirectional I/O port. The reset condition

of Port 2 is logic high. In this state, a weak pullup holds the port high. This

condition also serves as an input mode, since any external circuit that writes

to the port will overcome the weak pullup. When software writes a 0 to any port

pin, the DS87C530 will activate a strong pulldown that remains on until either

a 1 is written or a reset occurs. Writing a 1 after the port has been at 0 will cause

a strong transition driver to turn on, followed by a weaker sustaining pullup.

Once the momentary strong driver turns off, the port again becomes both the

output high and input state. As an alternate function Port 2 can function as MSB

of the external address bus. This bus can be used to read external ROM and

read/write external RAM memory or peripherals.

1522

815

P3.0 P3.7

Port 3 I/O. Port 3 functions as both an 8bit bidirectional I/O port and an

alternate functional interface for External Interrupts, Serial Port 0, Timer 0 and

1 Inputs, and RD and WR strobes. The reset condition of Port 3 is with all bits

at a logic 1. In this state, a weak pullup holds the port high. This condition also

serves as an input mode, since any external circuit that writes to the port will

overcome the weak pullup. When software writes a 0 to any port pin, the

DS87C530 will activate a strong pulldown that remains on until either a 1 is

written or a reset occurs. Writing a 1 after the port has been at 0 will cause a

strong transition driver to turn on, followed by a weaker sustaining pullup.

Once the momentary strong driver turns off, the port again becomes both the

output high and input state. The alternate modes of Port 3 are outlined below.

15

16

17

18

19

20

21

22

8

9

10

11

12

13

14

15

Port

Alternate Mode

P3.0

RXD0

Serial Port 0 Input

P3.1

TXD0

Serial Port 0 Output

P3.2

INT0

External Interrupt 0

P3.3

INT1

External Interrupt 1

P3.4

T0

Timer 0 External Input

P3.5

T1

Timer 1 External Input

P3.6

WR

External Data Memory Write Strobe

P3.7

RD

External Data Memory Read Strobe

42

35

EA

EA Input. Connect to ground to force the DS87C530 to use an external ROM.

The internal RAM is still accessible as determined by register settings. Connect

EA to V

CC

to use internal ROM.

51

44

V

BAT

V

BAT

Input. Connect to the power source that maintains SRAM and RTC

when V

CC

< V

BAT

. May be connected to a 3V lithium battery or a supercap.

See the electrical specifications for details.

DS87C530

022197 5/40

PLCC

DESCRIPTION

SIGNAL

NAME

TQFP

27, 28

20, 21

RTCX2,

RTCX1

RTCX2, RTCX1 Timekeeping crystal. Connect a 32.768 KHz crystal

between RTCX2 and RTCX1 to supply the timebase for the real time clock.

The DS87C530 supports both 6 pF and 12.5 pF load capacitance crystals as

selected by an SFR bit described below. To prevent noise from affecting the

RTC, the RTCX2 and RTCX1 pin should be guardringed with GND2.

2, 11,

13, 14,

40, 41

4, 6, 7,

33, 34,

47

NC

NC Reserved. These pins should not be connected. They are reserved for

use with future devices in the family.

COMPATIBILITY

The DS87C530 is a fully static CMOS 8051 compatible

microcontroller designed for high performance. While

remaining familiar to 8051 users, it has many new fea-

tures. In general, software written for existing 8051

based systems works without modification on the

DS87C530. The exception is critical timing since the

High Speed Micro performs its instructions much faster

than the original for any given crystal selection. The

DS87C530 runs the standard 8051 instruction set. It is

not pin compatible with other 8051s due to the time-

keeping crystal.

The DS87C530 provides three 16bit timer/counters,

fullduplex serial port (2), 256 bytes of direct RAM plus

1KB of extra MOVX RAM. I/O ports have the same

operation as a standard 8051 product. Timers will

default to a 12 clock per cycle operation to keep their

timing compatible with original 8051 systems. However,

timers are individually programmable to run at the new 4

clocks per cycle if desired. The PCA is not supported.

The DS87C530 provides several new hardware fea-

tures implemented by new Special Function Registers.

A summary of these SFRs is provided below.

PERFORMANCE OVERVIEW

The DS87C530 features a high speed 8051 compatible

core. Higher speed comes not just from increasing the

clock frequency, but from a newer, more efficient

design.

This updated core does not have the dummy memory

cycles that are present in a standard 8051. A conven-

tional 8051 generates machine cycles using the clock

frequency divided by 12. In the DS87C530, the same

machine cycle takes four clocks. Thus the fastest

instruction, 1 machine cycle, executes three times

faster for the same crystal frequency. Note that these

are identical instructions. The majority of instructions on

the DS87C530 will see the full 3 to 1 speed improve-

ment. Some instructions will get between 1.5 and 2.4 to

1 improvement. All instructions are faster than the origi-

nal 8051.

The numerical average of all opcodes gives approxi-

mately a 2.5 to 1 speed improvement. Improvement of

individual programs will depend on the actual instruc-

tions used. Speed sensitive applications would make

the most use of instructions that are three times faster.

However, the sheer number of 3 to 1 improved opcodes

makes dramatic speed improvements likely for any

code. These architecture improvements and 0.8

µ

m

CMOS produce a peak instruction cycle in 121 ns (8.25

MIPs). The Dual Data Pointer feature also allows the

user to eliminate wasted instructions when moving

blocks of memory.

INSTRUCTION SET SUMMARY

All instructions in the DS87C530 perform the same

functions as their 8051 counterparts. Their effect on

bits, flags, and other status functions is identical. How-

ever, the timing of each instruction is different. This

applies both in absolute and relative number of clocks.

For absolute timing of realtime events, the timing of

software loops can be calculated using a table in the

HighSpeed Microcontroller User's Guide. However,

counter/timers default to run at the older 12 clocks per

increment. In this way, timerbased events occur at the

standard intervals with software executing at higher

speed. Timers optionally can run at 4 clocks per incre-

ment to take advantage of faster processor operation.

The relative time of two instructions might be different in

the new architecture than it was previously. For exam-

ple, in the original architecture, the "MOVX A, @DPTR"

instruction and the "MOV direct, direct" instruction used