32K x 8 Static RAM

CY7C199C

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose

,

CA 95134

·

408-943-2600

Document #: 38-05408 Rev. *A

Revised September 11, 2003

Features

· Fast access time: 12 ns, 15 ns, 20 ns, and 25 ns

· Wide voltage range: 5.0V ± 10% (4.5V to 5.5V)

· CMOS for optimum speed/power

· TTLcompatible Inputs and Outputs

· Available in 28 DIP, 28 SOJ, and 28 TSOP I.

· 2.0V Data Retention

· Low CMOS standby power

· Automated Powerdown when deselected

General Description

1

The CY7C199C is a highperformance CMOS Asynchronous

SRAM organized as 32K by 8 bits that supports an

asynchronous memory interface. The device features an

automatic powerdown feature that significantly reduces

power consumption when deselected.

See the Truth Table in this datasheet for a complete

description of read and write modes.

The CY7C199C is available in 28 DIP, 28 SOJ, and 28 TSOP

I package(s).

Product Portfolio

Notes:

1. For bestpractices recommendations, please refer to the Cypress application note System Design Guidelines on www.cypress.com.

12 ns

15 ns

20 ns

25 ns

Unit

Maximum Access Time

12

15

20

25

ns

Maximum Operating Current

85

80

75

75

mA

Maximum CMOS Standby Current

(low power)

500

500

500

500

uA

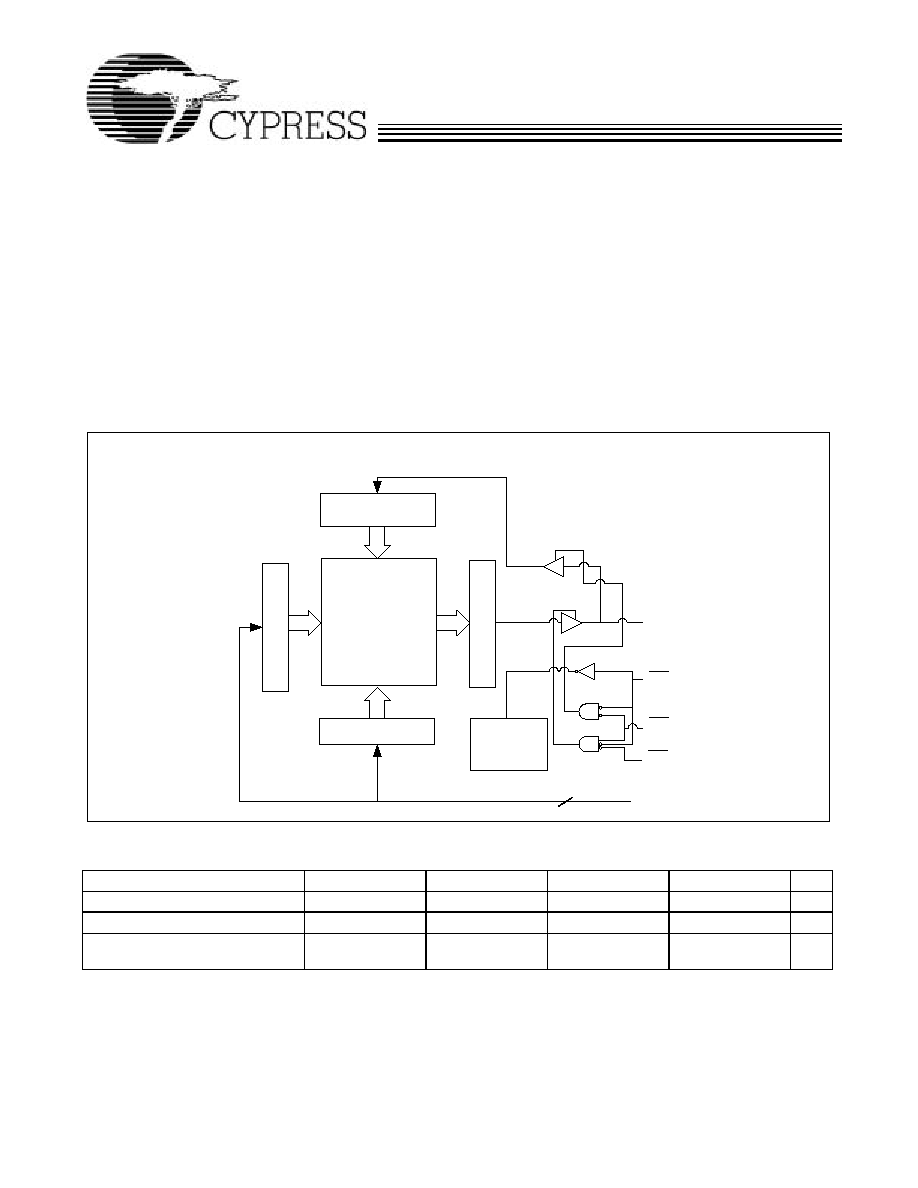

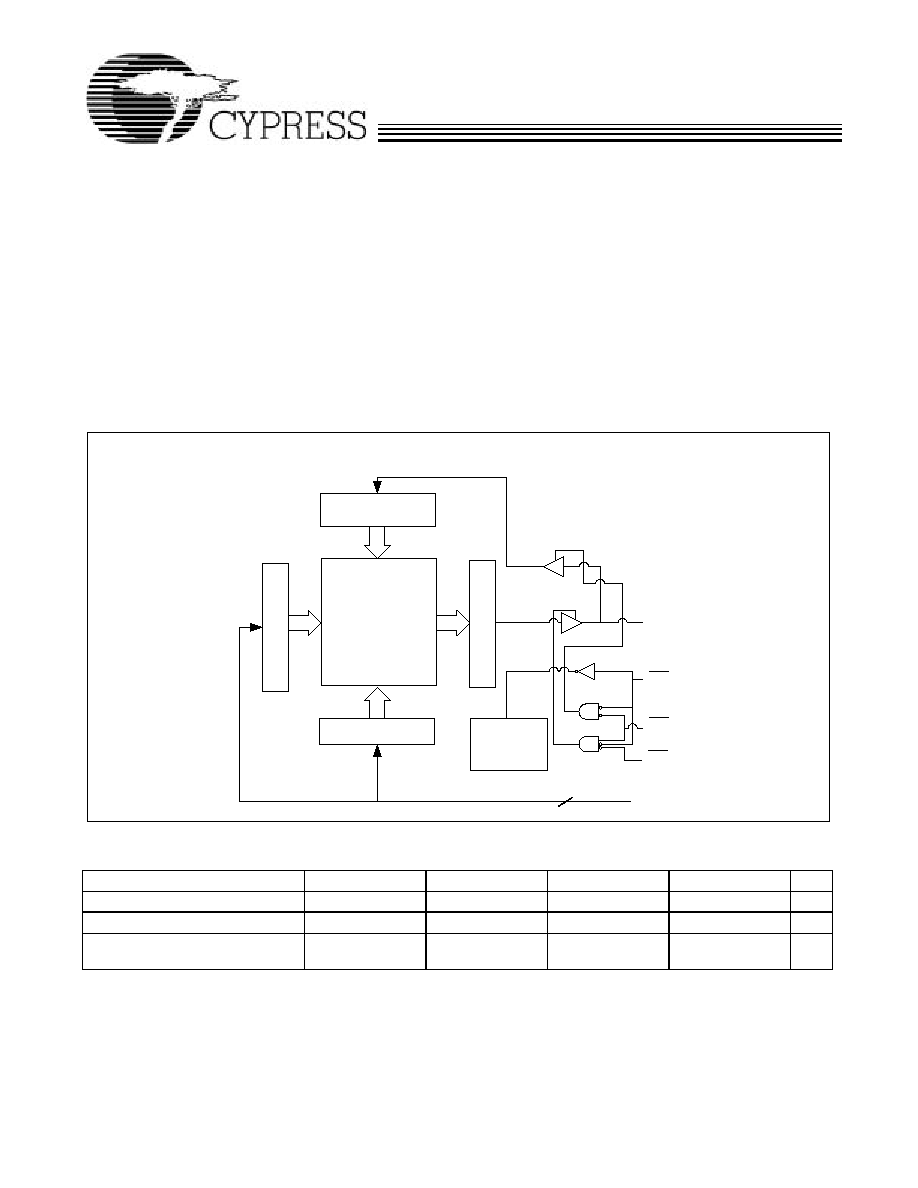

Row D

e

code

r

RAM Array

Column Decoder

Input Buffer

S

ense

A

m

ps

A

X

Power

Down

Circuit

I/Ox

OE

WE

CE

X

Logic Block Diagram

CY7C199C

Document #: 38-05408 Rev. *A

Page 2 of 12

Pin Layout and Specifications

A

5

A

6

A

7

A

8

A

9

A

10

A

11

A

12

A

13

A

14

I/O

0

I/O

1

I/O

2

V

SS

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

CE

A

0

OE

A

1

A

2

A

3

A

4

WE

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

28 DIP (6.9 x 35.6 x 3.5 mm) P21

OE

A

1

A

2

A

3

A

4

WE

V

CC

A

5

A

6

A

7

A

8

A

9

A

10

A

11

A

12

A

13

A

14

I/O

0

I/O

1

I/O

2

V

SS

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

CE

A

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

28 TSOP I (8 x 13.4 x 1.2 mm) Z28

CY7C199C

Document #: 38-05408 Rev. *A

Page 3 of 12

Pin Layout and Specifications

(continued)

Truth Table

Pin Description

Pin

Type

Description

DIP

SOJ

TSOP I

A

X

Input

Address Inputs.

1, 2, 3, 4, 5, 6, 7,

8, 9, 10, 21, 23,

24, 25, 26

1, 2, 3, 4, 5, 6, 7,

8, 9, 10, 21, 23,

24, 25, 26

2, 3, 4, 5, 8, 9,

10, 11, 12, 13,

14, 15, 16, 17,

28

CE

Control

Chip Enable.

20

20

27

I/O

X

Input or

Output

Data Input/Outputs.

11, 12, 13, 15,

16, 17, 18, 19

11, 12, 13, 15,

16, 17, 18, 19

18, 19, 20, 22,

23, 24, 25, 26

OE

Control

Output Enable.

22

22

1

V

CC

Supply

Power (5.0V).

28

28

7

V

SS

Supply

Ground.

14

14

21

WE

Control

Write Enable.

27

27

6

A

5

A

6

A

7

A

8

A

9

A

10

A

11

A

12

A

13

A

14

I/O

0

I/O

1

I/O

2

V

SS

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

CE

A

0

OE

A

1

A

2

A

3

A

4

WE

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

28 SOJ (8 x 18 x 3.5 mm) V21

CE

OE

WE

I/Ox

Mode

Power

H

X

X

High Z

Deselect / Power-Down

Standby (I

SB

)

L

L

H

Data Out

Read

Active (I

CC

)

L

X

L

Data In

Write

Active (I

CC

)

L

H

H

High Z

Selected, outputs disabled

Active (I

CC

)

CY7C199C

Document #: 38-05408 Rev. *A

Page 4 of 12

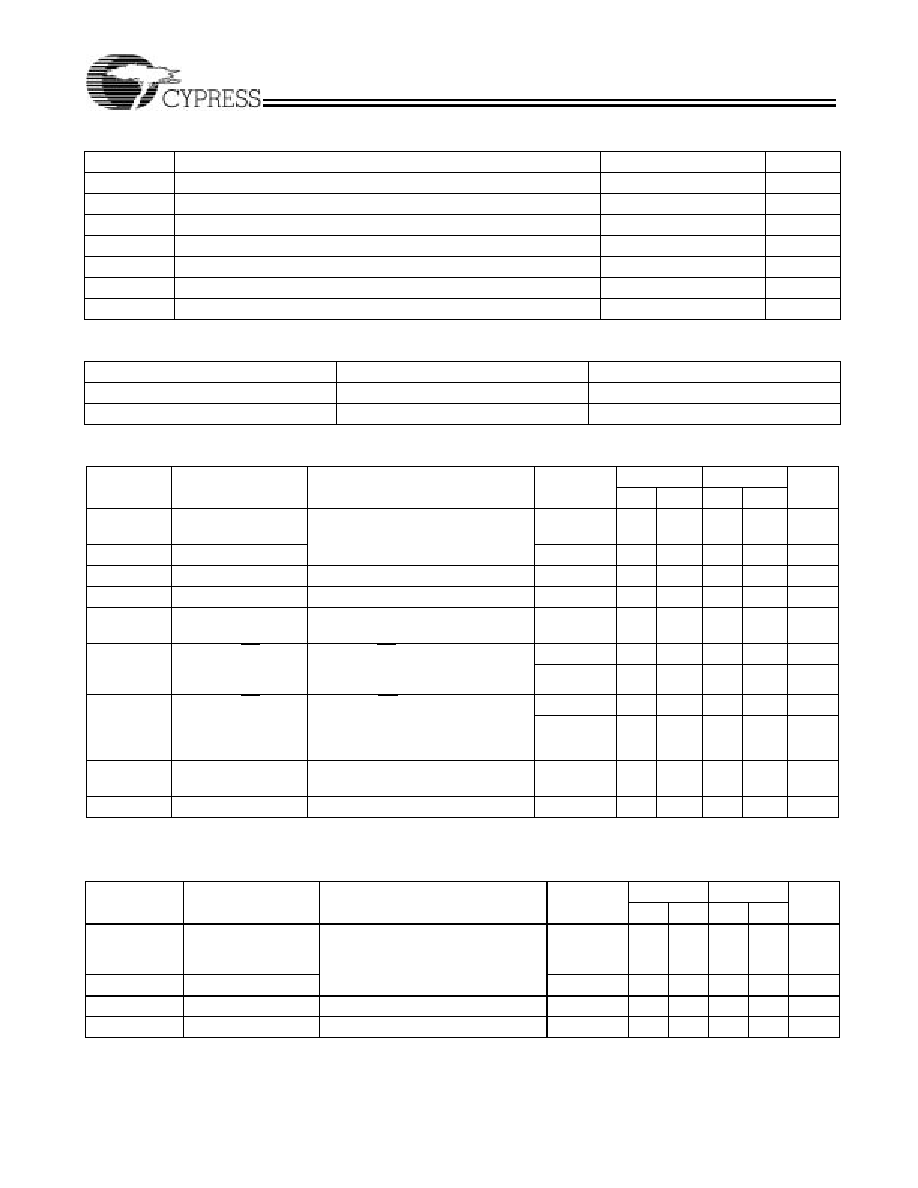

Maximum Ratings

(Above which the useful life may be impaired. For user guidelines, not tested.)

Operating Range

DC Electrical Characteristics

Over the Operating Range (12, 15)

2

DC Electrical Characteristics

Over the Operating Range (20, 25)

3

Parameter

Description

Value

Unit

T

STG

Storage Temperature

65 to +150

°C

T

AMB

Ambient Temperature with Power Applied (i.e. case temperature)

55 to +125

°C

V

CC

Core Supply Voltage Relative to V

SS

0.5 to +7.0

V

V

IN

, V

OUT

DC Voltage Applied to any Pin Relative to V

SS

0.5 to V

CC

+ 0.5

V

I

OUT

Output ShortCircuit Current

20

mA

V

ESD

Static Discharge Voltage (per MILSTD883, Method 3015)

> 2001

V

I

LU

Latchup Current

> 200

mA

Range

Ambient Temperature (T

A

)

Voltage Range (V

CC

)

Commercial

0°C to 70°C

5.0V ± 10%

Industrial

40°C to 85°C

5.0V ± 10%

Parameter

Description

Condition

Power

12 ns

15 ns

Unit

Min.

Max.

Min.

Max.

V

IH

Input HIGH Voltage

2.2

V

CC

+ 0.3

2.2

V

CC

+ 0.3

V

V

IL

Input LOW Voltage

0.5

0.8

0.5

0.8

V

V

OH

Output HIGH Voltage V

CC

= Min., I

OH

= 4.0 mA

2.4

2.4

V

V

OL

Output LOW Voltage V

CC

= Min., I

OL

= 8.0 mA

0.4

0.4

V

I

CC

V

CC

Operating

Supply Current

V

CC

= Max., I

OUT

= 0 mA, f = F

MAX

=

1/t

RC

85

80

mA

I

SB1

Automatic CE

Powerdown

Current TTL Inputs

Max. V

CC

, CE

V

IH

, V

IN

V

IH

or V

IN

V

IL

, f = F

MAX

30

30

mA

L

10

10

mA

I

SB2

Automatic CE

Powerdown

Current CMOS

Inputs

Max. V

CC

, CE

V

CC

0.3V, V

IN

V

CC

0.3V, or V

IN

0.3V, f = 0

10

10

mA

L

500

500

uA

I

OZ

Output Leakage

Current

GND

Vi

V

CC

, Output Disabled

5

+5

5

+5

uA

I

IX

Input Load Current

GND

Vi

V

CC

5

+5

5

+5

uA

Notes:

2. V

IL

(min) = 2.0V for pulse durations of less than 20 ns.

Parameter

Description

Condition

Power

20 ns

25 ns

Unit

Min

Max

Min

Max

V

IH

Input HIGH Voltage

2.2

V

CC

+

0.3

2.2

V

CC

+

0.3

V

V

IL

Input LOW Voltage

0.5

0.8

0.5

0.8

V

V

OH

Output HIGH Voltage V

CC

= Min., I

OH

= 4.0 mA

2.4

2.4

V

V

OL

Output LOW Voltage V

CC

= Min., I

OL

= 8.0 mA

0.4

0.4

V

3.V

IL

(min) = 2.0V for pulse durations of less than 20 ns.

CY7C199C

Document #: 38-05408 Rev. *A

Page 5 of 12

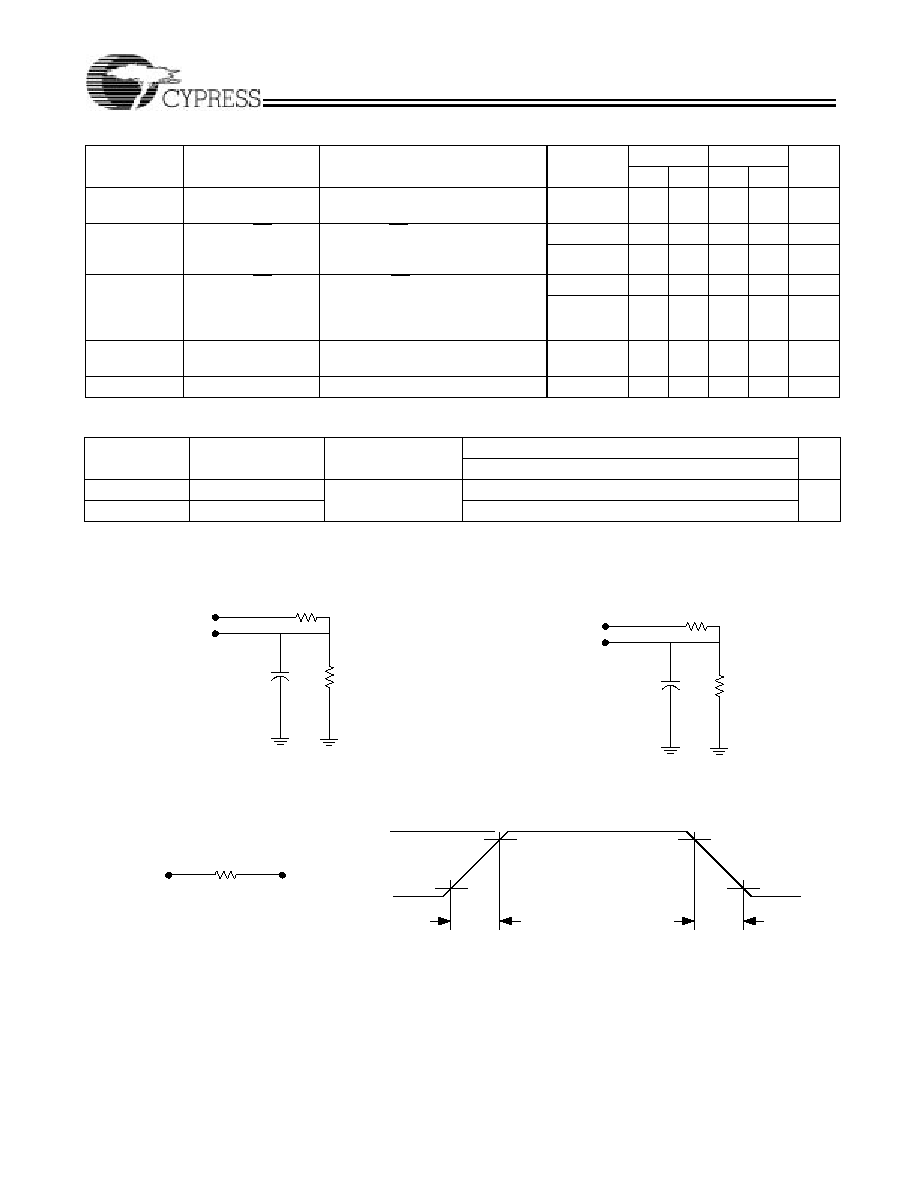

Capacitance

4

AC Test Loads

I

CC

V

CC

Operating

Supply Current

V

CC

= Max., I

OUT

= 0 mA, f = F

MAX

=

1/t

RC

75

75

mA

I

SB1

Automatic CE

Powerdown

Current TTL Inputs

Max. V

CC

, CE

V

IH

, V

IN

V

IH

or V

IN

V

IL

, f = F

MAX

30

30

mA

L

10

10

mA

I

SB2

Automatic CE

Powerdown

Current CMOS

Inputs

Max. V

CC

, CE

V

CC

0.3V, V

IN

V

CC

0.3V, or V

IN

0.3V, f = 0

10

10

mA

L

500

500

uA

I

OZ

Output Leakage

Current

GND

Vi

V

CC

, Output Disabled

5

+5

5

+5

uA

I

IX

Input Load Current

GND

Vi

V

CC

5

+5

5

+5

uA

Parameter

Description

Conditions

Max

Unit

ALL PACKAGES

C

IN

Input Capacitance

T

A

= 25C, f = 1 MHz,

V

CC

= 5.0V

8

pF

C

OUT

Output Capacitance

8

Notes:

4. Tested initially and after any design or process change that may affect these parameters.

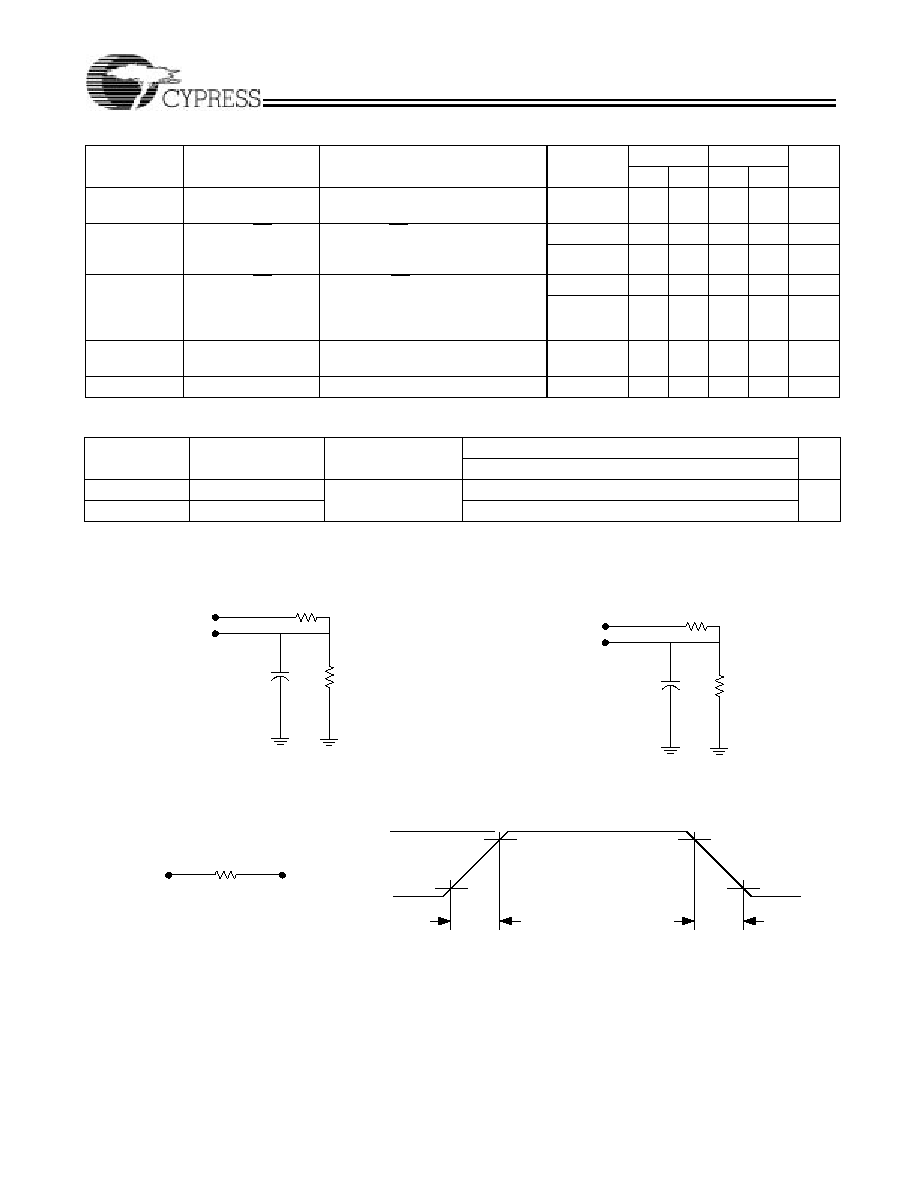

Parameter

Description

Condition

Power

20 ns

25 ns

Unit

Min

Max

Min

Max

V

CC

V

SS

Rise Time

1 V/ns

Fall Time

1 V/ns

All Input Pulses

90%

10%

90%

10%

V

Output

R1

R2

C1

CC

V

Output

R3

C2

CC

R4

Output Loads

Output Loads

for t

HZOE

, t

HZCE

& t

HZWE

* including scope and jig capacitance

(B)*

(A)*

R

th

T

V

Thevenin Equivalent