PRELIMINARY

2M x 36/4M x 18 Pipelined DCD SRAM

CY7C1484V33

CY7C1485V33

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose

,

CA 95134

·

408-943-2600

Document #: 38-05285 Rev. *A

Revised January 18, 2003

Features

· Fast clock speed: 250, 200, and 167 MHz

· Provide high-performance 3-1-1-1 access rate

· Fast access time: 2.6, 3.0, and 3.4 ns

· Optimal for depth expansion

· Single 3.3V 5% and +5% power supply V

DD

· Separate V

DDQ

for 3.3V or 2.5V

· Common data inputs and data outputs

· Byte Write Enable and Global Write control

· Chip enable for address pipeline

· Address, data, and control registers

· Internally self-timed Write Cycle

· Burst control pins (interleaved or linear burst

sequence)

· Automatic power-down for portable applications

· High-density, high-speed packages

· JTAG boundary scan for BGA packaging version

· Available in 119-ball bump BGA and 100-pin TQFP

packages (CY7C1484V33 and CY7C1485V33).

· 165-ball FBGA will be offered on an opportunity basis.

(Please contact Cypress sales or marketing)

Functional Description

The Cypress Synchronous Burst SRAM family employs

high-speed, low-power CMOS designs using advanced

single-layer polysilicon, triple-layer metal technology. Each

memory cell consists of six transistors.

The CY7C1484V33 and CY7C1485V33 SRAMs integrate

2,097,152 × 36/4,194,304 × 18 SRAM cells with advanced

synchronous peripheral circuitry and a two-bit counter for

internal burst operation. All synchronous inputs are gated by

registers controlled by a positive-edge-triggered Clock Input

(CLK). The synchronous inputs include all addresses, all data

inputs, address-pipelining Chip Enable (CE), burst control

inputs (ADSC, ADSP, and ADV), write enables (BW

a

, BW

b

,

BW

c

, BW

d

, and BWE), and Global Write (GW).

Asynchronous inputs include the Output Enable (OE) and

burst mode control (MODE). The data (DQx) and the data

parity (DPx) outputs, enabled by OE, are also asynchronous.

DQa,b,c,d and DPa,b,c,d apply to CY7C1484V33 and DQa,b

and DPa,b apply to CY7C1485V33. a, b, c, and d each are

eight bits wide in the case of DQ and one bit wide in the case

of DP.

Addresses and chip enables are registered with either

Address Status Processor (ADSP) or Address Status

Controller (ADSC) input pins. Subsequent burst addresses

can be internally generated as controlled by the Burst Advance

Pin (ADV).

Address, data inputs, and write controls are registered on-chip

to initiate self-timed Write cycle. Write cycles can be one to

four bytes wide as controlled by the write control inputs.

Individual byte write allows individual byte to be written. BW

a

controls DQa and DPa. BW

b

controls DQb and DPb. BW

c

controls DQc and DPd. BW

d

controls DQ and DPd. BW

a

, BW

b

,

BW

c

, BW

d

can be active only with BWE being LOW. GW being

LOW causes all bytes to be written. Write pass-through

capability allows written data available at the output for the

immediately next Read cycle. This device also incorporates

pipelined enable circuit for easy depth expansion without

penalizing system performance.

The CY7C1484V33/CY7C1485V33 are both double-cycle

deselect parts.All inputs and outputs of the CY7C1484V33,

CY7C1485V33 are JEDEC standard JESD8-5-compatible.

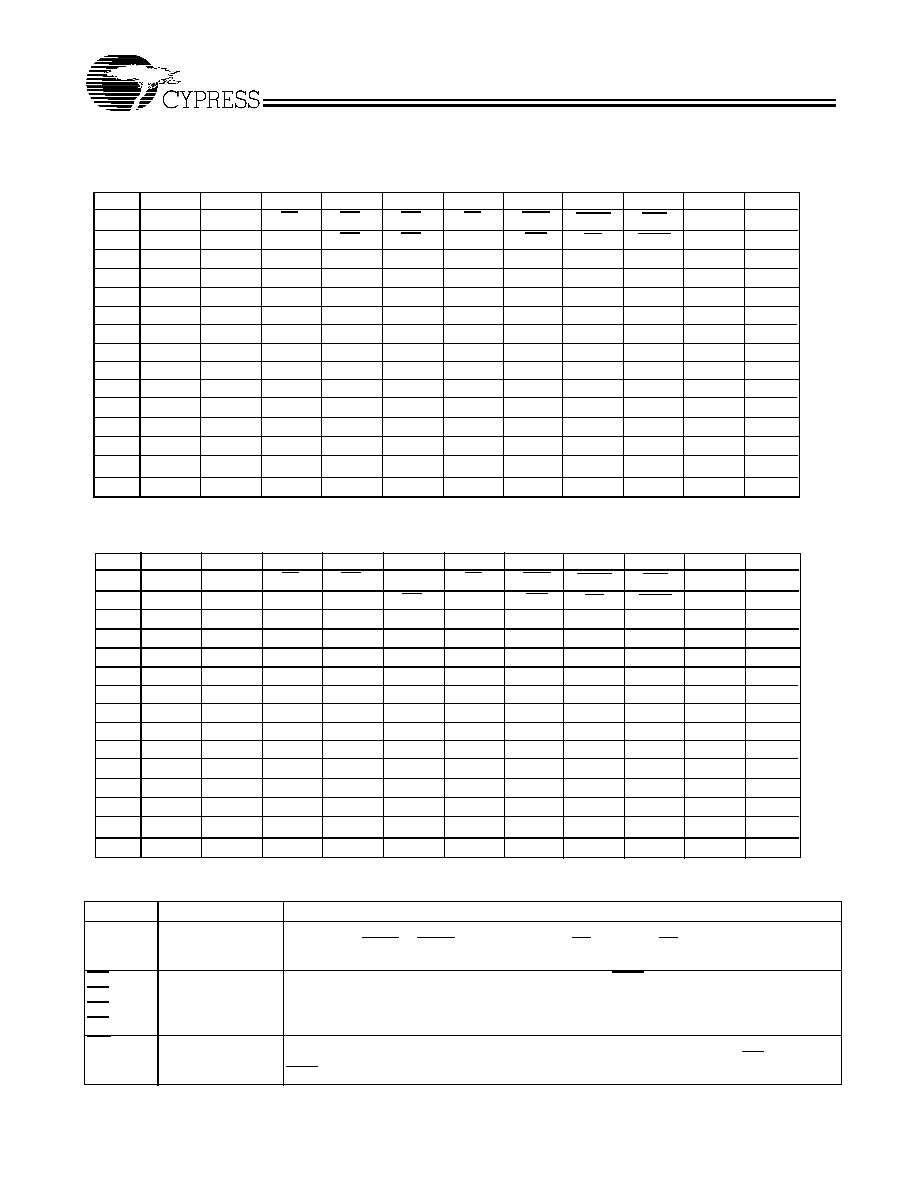

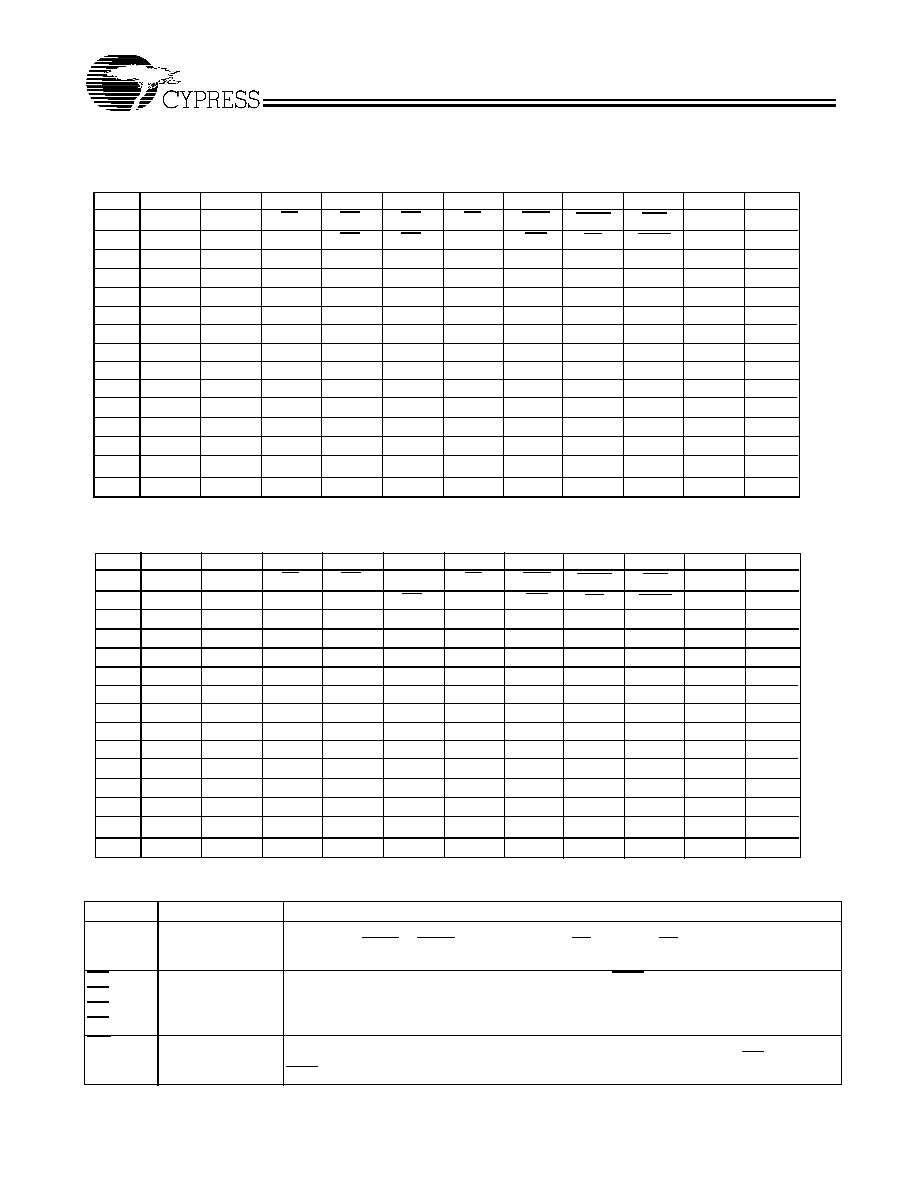

Selection Guide

CY7C1484V33-

250

CY7C1485V33-

250

CY7C1484V33-

200

CY7C1485V33-

200

CY7C1484V33-

167

CY7C1485V33-

167

Unit

Maximum Access Time

2.6

3.0

3.4

ns

Maximum Operating Current

TBD

TBD

TBD

mA

Maximum CMOS Standby Current

TBD

TBD

TBD

mA

Shaded areas contain advance information.

PRELIMINARY

CY7C1484V33

CY7C1485V33

Document #: 38-05285 Rev. *A

Page 5 of 29

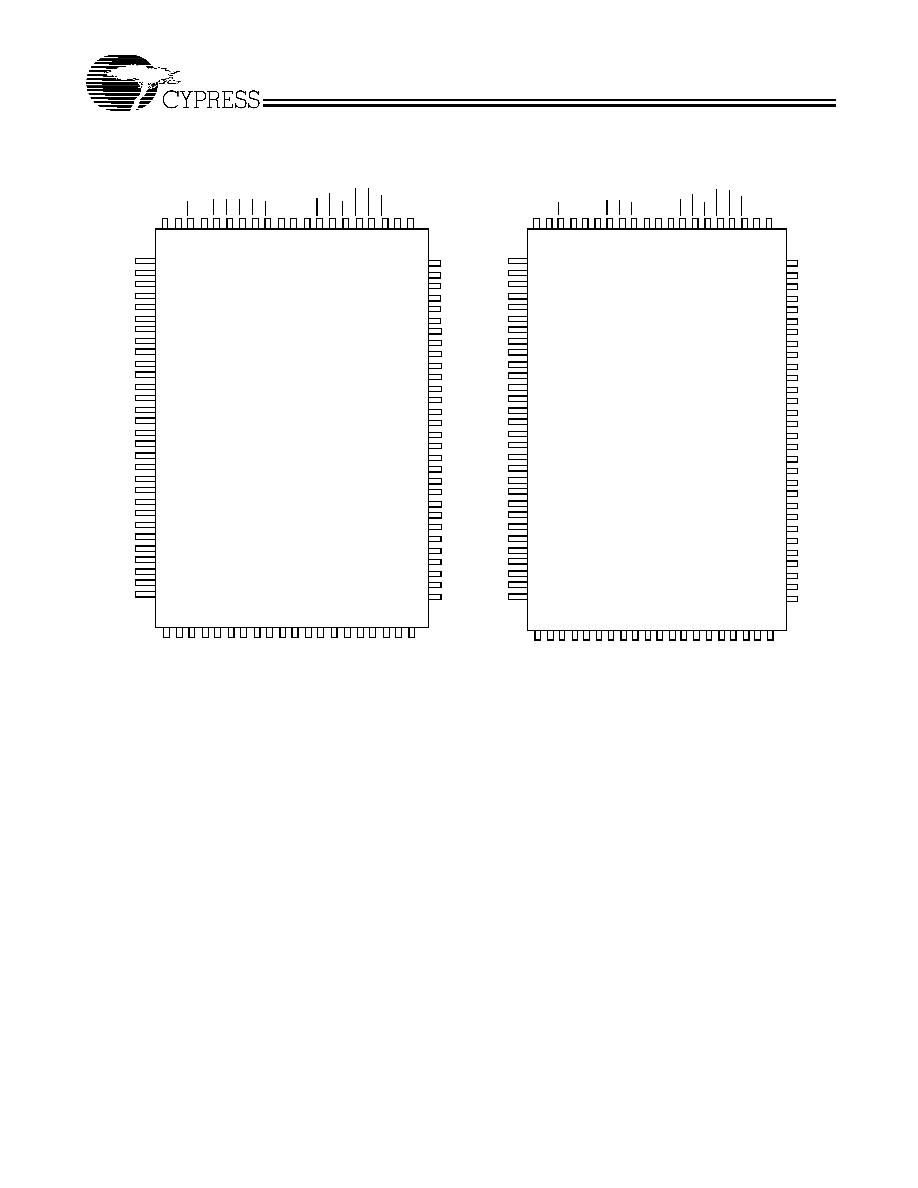

Pin Configurations

(continued)

CY7C1484V33 (2M × 36)11 × 15 FBGA

165-ball Bump FBGA (This package is offered on an opportunity basis)

CY7C1485V33 (4M × 18)11 × 15 FBGA

2

3

4

5

6

7

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

TDO

NC

NC

NC

NC

DPb

NC

DQb

A

CE

1

NC

CE

3

BW

b

BWE

A

CE

2

NC

DQb

DQb

MODE

NC

DQb

DQb

NC

NC

NC

A

A

V

DDQ

NC

BW

a

CLK

GW

V

SS

V

SS

V

SS

V

SS

V

DDQ

V

SS

V

DD

V

SS

V

SS

V

SS

A

V

SS

V

SS

V

SS

V

SS

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

A

A

V

DD

V

SS

V

DD

V

SS

V

SS

V

DDQ

V

DD

V

SS

V

DD

V

SS

V

DD

V

SS

V

SS

V

SS

V

DD

V

DD

V

SS

V

DD

V

SS

V

SS

NC

TCK

A0

V

SS

A

TDI

A

TMS

DQb

V

SS

NC

V

SS

DQb

NC

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

A1

DQb

NC

NC

NC

V

DDQ

V

SS

8

9

10

11

A

ADV

A

ADSC

A

OE

ADSP

A

144M

V

SS

V

DDQ

NC

DPa

V

DDQ

V

DD

NC

DQa

DQa

NC

NC

NC

DQa

NC

V

DD

V

DDQ

V

DD

V

DDQ

DQa

V

DD

NC

V

DD

NC

V

DD

V

DDQ

DQa

V

DDQ

V

DD

V

DD

V

DDQ

V

DD

V

DDQ

NC

V

DDQ

A

A

V

SS

A

A

A

A

DQa

NC

NC

ZZ

DQa

NC

NC

DQa

A

V

DDQ

2

3

4

5

6

7

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

TDO

NC

NC

DPc

DQc

DPd

NC

DQd

A

CE

1

BW

b

CE

3

BW

c

BWE

A

CE

2

DQc

DQd

DQd

MODE

NC

DQc

DQc

DQd

DQd

DQd

A

A

V

DDQ

BW

d

BW

a

CLK

GW

V

SS

V

SS

V

SS

V

SS

V

DDQ

V

SS

V

DD

V

SS

V

SS

V

SS

A

V

SS

V

SS

V

SS

V

SS

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

A

A

V

DD

V

SS

V

DD

V

SS

V

SS

V

DDQ

V

DD

V

SS

V

DD

V

SS

V

DD

V

SS

V

SS

V

SS

V

DD

V

DD

V

SS

V

DD

V

SS

V

SS

NC

TCK

A0

V

SS

A

TDI

A

TMS

DQc

V

SS

DQc

V

SS

DQc

DQc

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

A1

DQd

DQd

NC

NC

V

DDQ

V

SS

8

9

10

11

A

ADV

A

ADSC

NC

OE

ADSP

A

144M

V

SS

V

DDQ

NC

DPb

V

DDQ

V

DD

DQb

DQb

DQb

NC

DQb

NC

DQa

DQa

V

DD

V

DDQ

V

DD

V

DDQ

DQb

V

DD

NC

V

DD

DQa

V

DD

V

DDQ

DQa

V

DDQ

V

DD

V

DD

V

DDQ

V

DD

V

DDQ

DQa

V

DDQ

A

A

V

SS

A

A

A

A

DQb

DQb

DQb

ZZ

DQa

DQa

DPa

DQa

A

V

DDQ

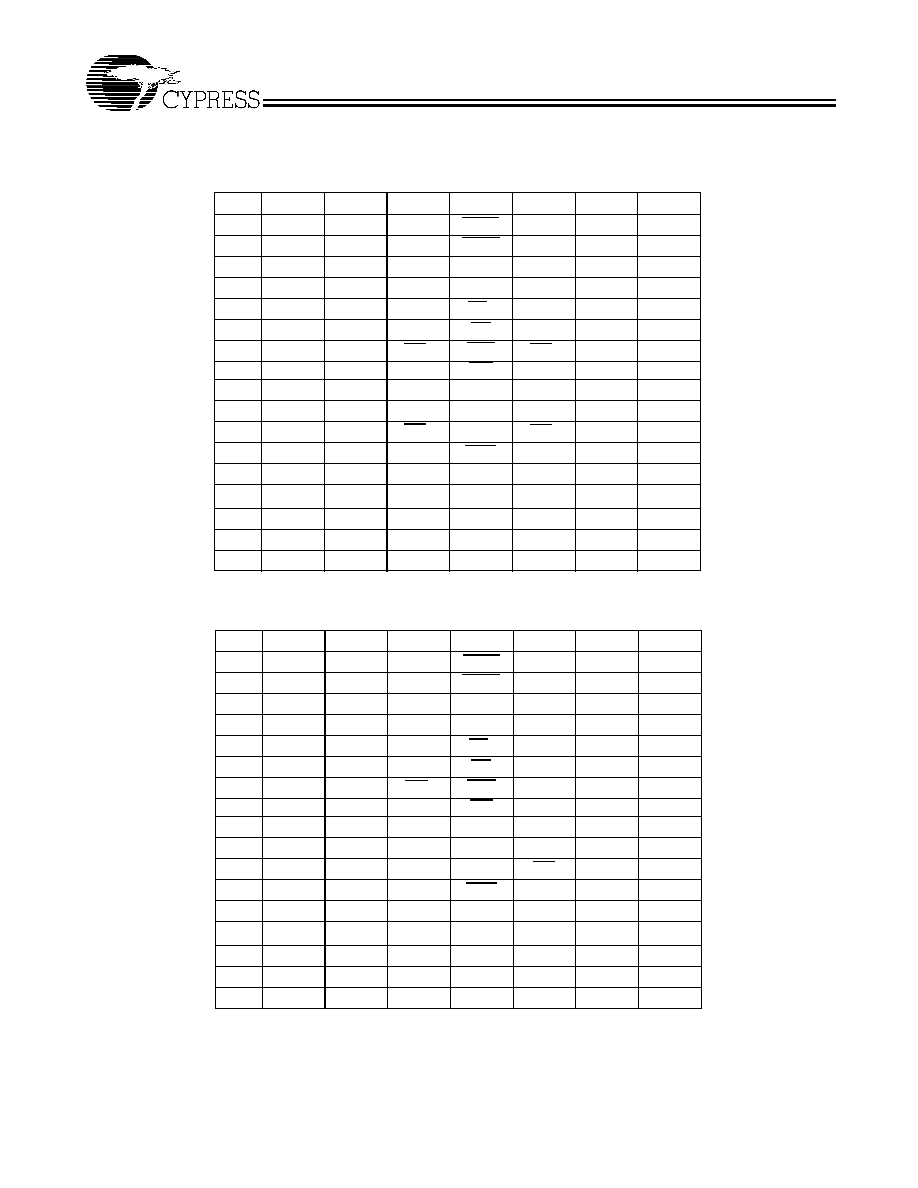

Pin Definitions

Pin Name

I/O

Pin Description

A0

A1

A

Input-

Synchronous

Address Inputs used to select one of the address locations. Sampled at the rising edge

of the CLK if ADSP or ADSC is active LOW, and CE

1,

CE

2

, and

CE

3

are sampled active. A

[1:0]

feed the two-bit counter.

BW

a

BW

b

BW

c

BW

d

Input-

Synchronous

Byte Write Select Inputs, active LOW. Qualified with BWE to conduct byte writes to the

SRAM. Sampled on the rising edge of CLK.

GW

Input-

Synchronous

Global Write Enable Input, active LOW. When asserted LOW on the rising edge of CLK, a

global write is conducted (ALL bytes are written, regardless of the values on BW

a,b,c,d

and

BWE).