/home/web/doc/html/cypress/169527

PRELIMINARY

18-Mb DDR-II SIO SRAM Two-word

Burst Architecture

CY7C1392V18

CY7C1393V18

CY7C1394V18

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose

·

CA 95134

·

408-943-2600

Document #: 38-05179 Rev. *A

Revised July 31, 2002

Features

· 18-Mb density (2M x 8, 1M x 18, 512K x 36)

-- Supports concurrent transactions

· 250-MHz clock for high bandwidth

· Two-word burst for reducing address bus frequency

· Double Data Rate (DDR) interfaces (data transferred at

500 MHz) @ 250 MHz

· Two input clocks (K and K) for precise DDR timing

-- SRAM uses rising edges only

· Two output clocks (C and C) accounts for clock skew

and flight time mismatches

· Echo clocks (CQ and CQ) simplify data capture in high

speed systems

· Separate Port Selects for depth expansion

· Synchronous internally self-timed writes

· 1.8V core power supply with HSTL inputs and outputs

· Variable drive HSTL output buffers

· Expanded HSTL output voltage (1.4V1.9V)

· 13x15 mm 1.0-mm pitch fBGA package, 165 ball (11 x 15

matrix)

· JTAG Interface

· On-chip Delay Lock Loop (DLL)

Configuration

CY7C1392V182M x 8

CY7C1393V181M x18

CY7C1394V18512K x 36

Functional Description

The CY7C1392V18/CY7C1393V18/CY7C1394V18 are 1.8V

Synchronous Pipelined SRAMs equipped with DDR-II SIO

(Double Data Rate Separate I/O) architecture. The DDR-II SIO

consists of two separate DDR ports, Read and Write port, to

access the memory array. The Read port has dedicated

outputs and the Write port has dedicated inputs to support

read and write operations concurrently. Access to each port is

accomplished using a common address bus. Addresses for

Read and Write are latched on alternate rising edges of the

input (K) clock. Write data is registered on the rising edges of

both K and K. Read data is driven on the rising edges of C and

C if provided, or on the rising edge of K and K if C/C are not

provided. Each address location is associated with two 8-bit

words in the case of CY7C1392V18, two 18-bit words in the

case of CY7C1393V18, and two 36-bit words in the case of

CY7C1394V18, that burst sequentially into or out of the

device.

Asynchronous inputs include impedance match (ZQ).

Synchronous data outputs are tightly matched to the two

output echo clocks CQ/CQ, eliminating the need for separately

capturing data from each individual DDR-II SIO SRAM in the

system design. Output data clocks (C/C) enable maximum

system clocking and data synchronization flexibility.

All synchronous inputs pass through input registers controlled

by the K/K input clocks. All data outputs pass through output

registers controlled by the C/C input clocks (or K/K in single

clock mode). Writes are conducted with on-chip synchronous

self-timed write circuitry.

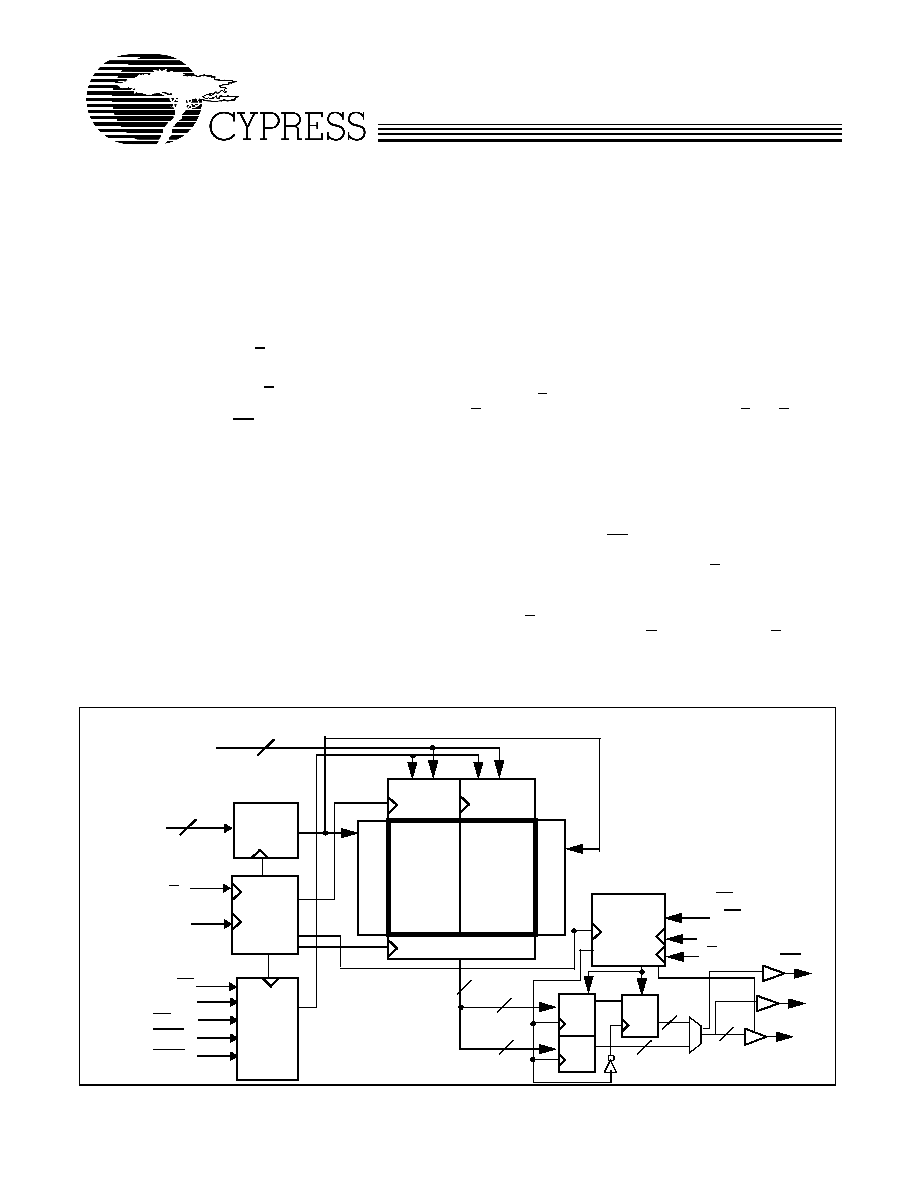

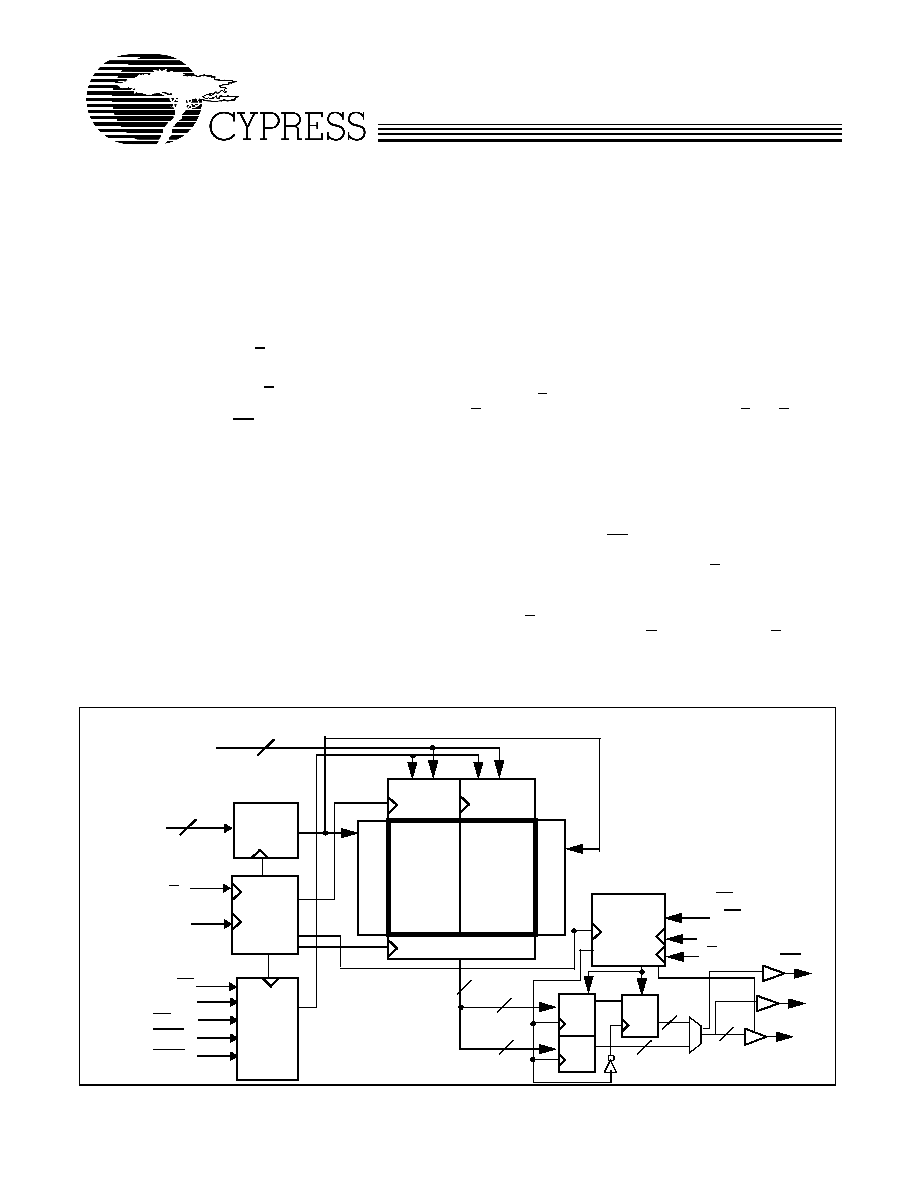

Logic Block Diagram (CY7C1392V18)

1M x 8

CLK

A

(19:0)

Gen.

K

K

Control

Logic

Address

Register

D

[7:0]

Read A

dd.

Decod

e

Read Data Reg.

LD

Q

[7:0]

Control

Logic

Reg.

Reg.

Reg.

8

8

16

Write

8

BWS

0

V

REF

W

r

it

e Add.

Decode

Data Reg

Write

Data Reg

Memory

Array

1M x 8

Memory

Array

8

8

20

8

C

C

BWS

1

R/W

LD

R/W

CQ

CQ

PRELIMINARY

CY7C1392V18

CY7C1393V18

CY7C1394V18

Document #: 38-05179 Rev. *A

Page 2 of 24

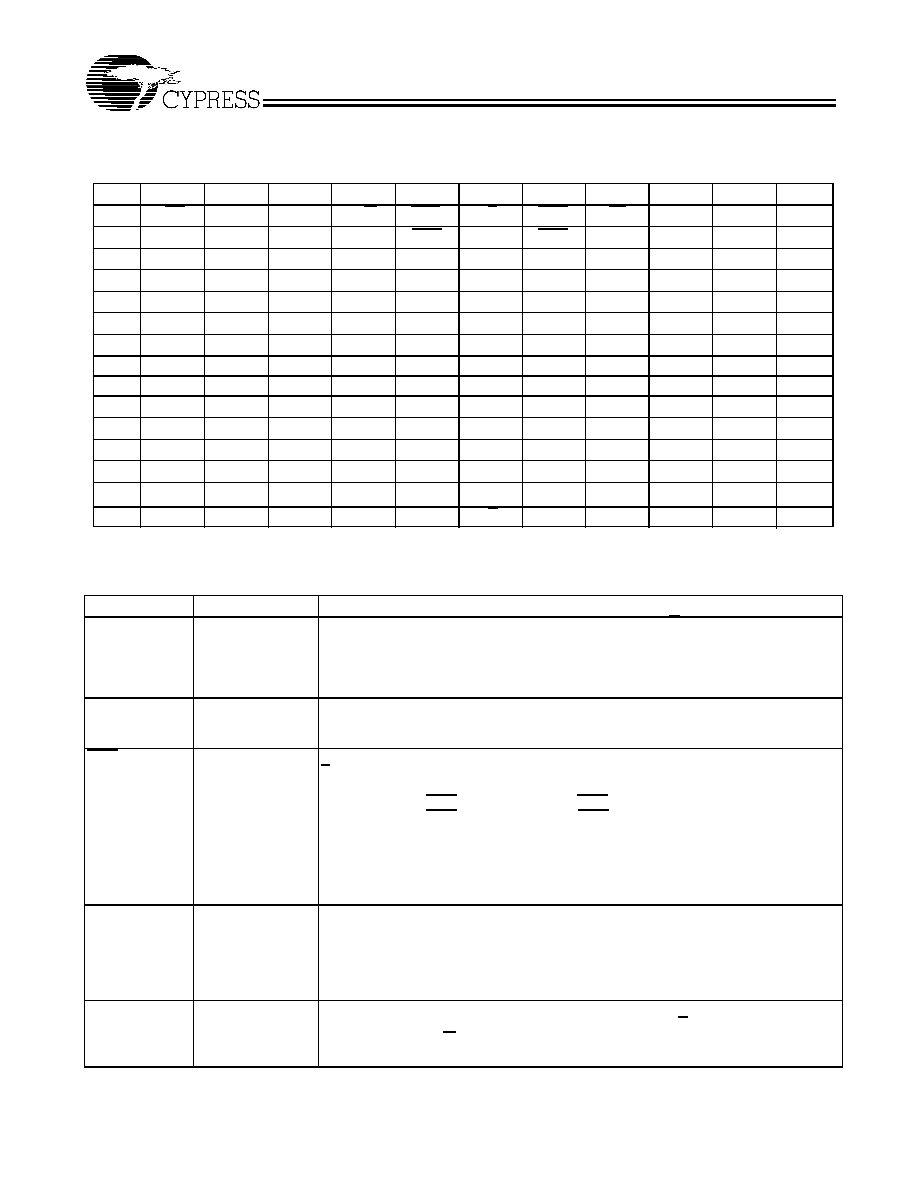

Selection Guide

300 MHz

[1]

250 MHz

200 MHz

167 MHz

Unit

Maximum Operating Frequency

300

250

200

167

MHz

Maximum Operating Current

TBD

TBD

TBD

TBD

mA

Note:

1.

Shaded cells indicate advanced information.

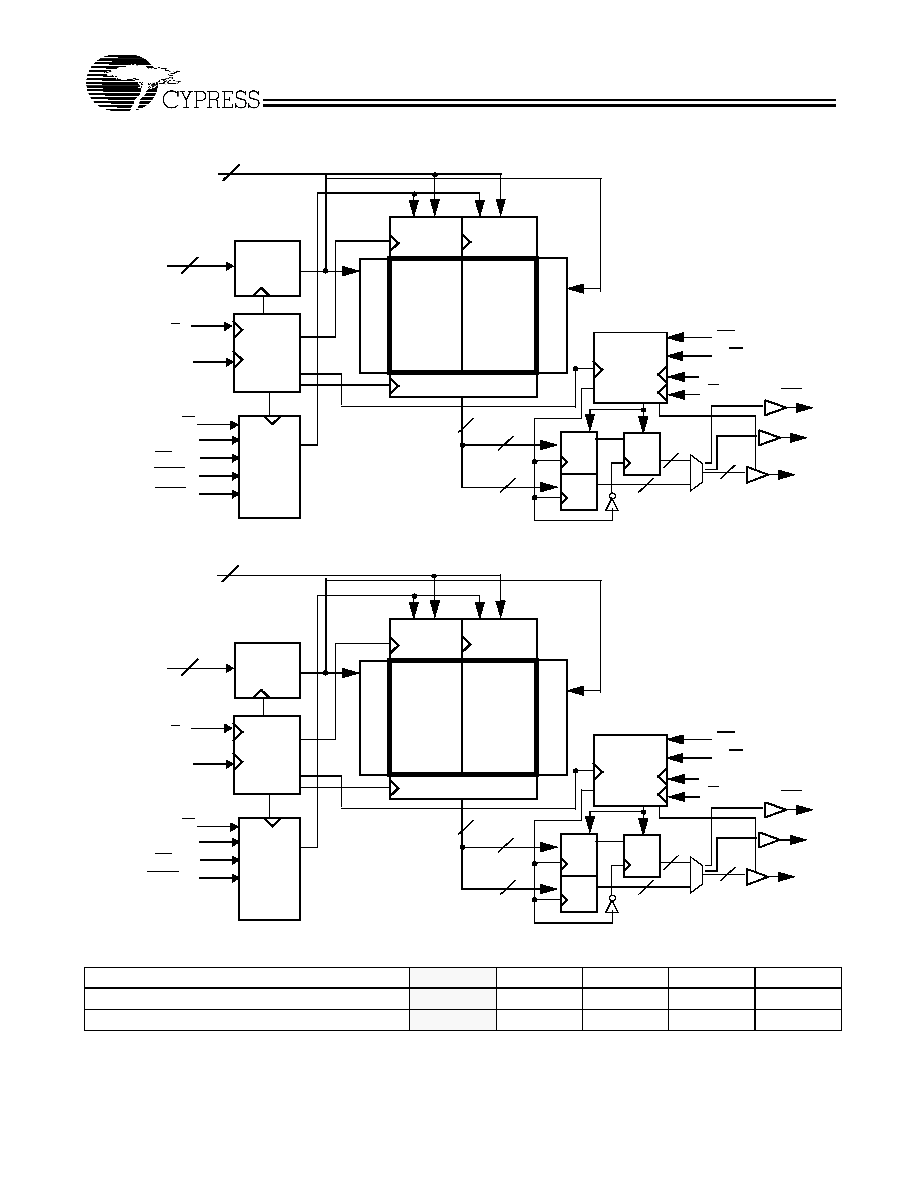

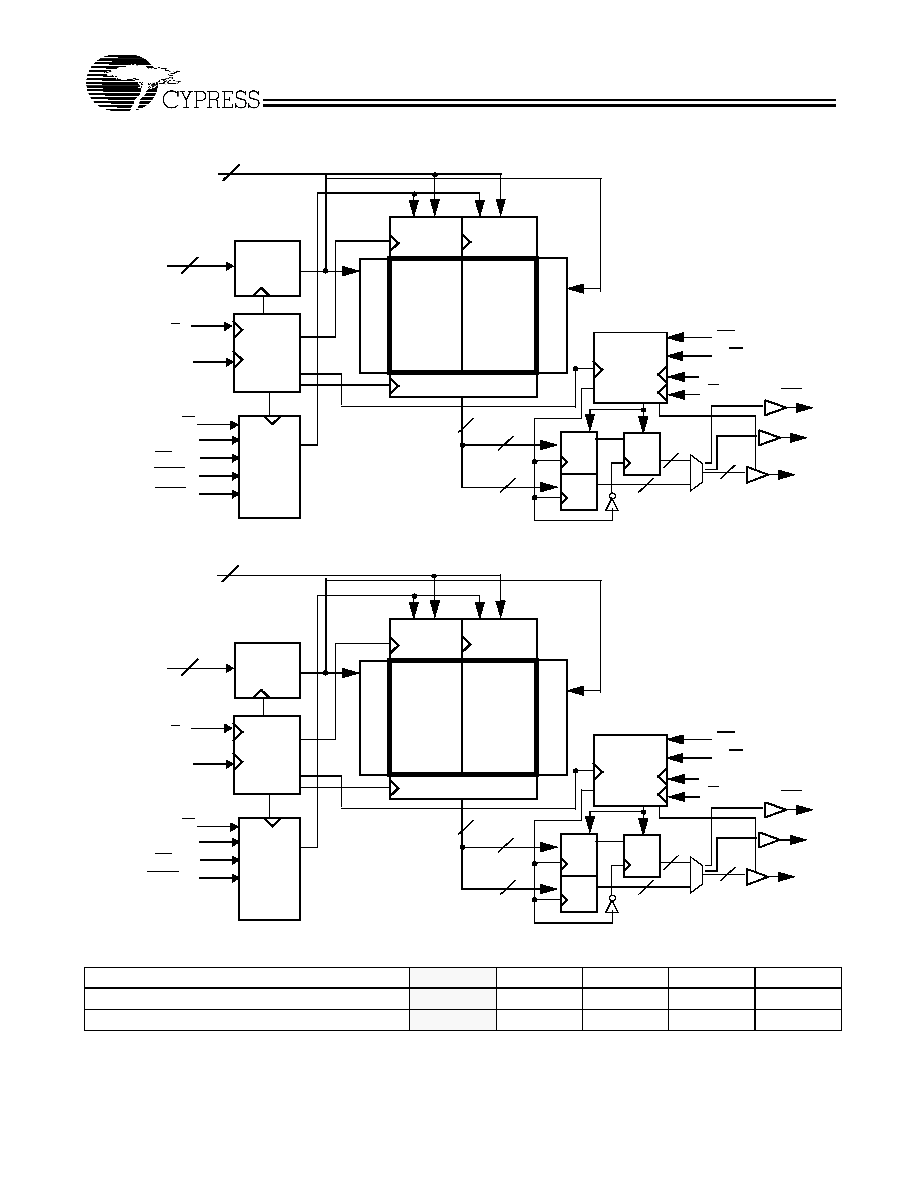

Logic Block Diagram (CY7C1393V18)

512K x 18

CLK

A

(18:0)

Gen.

K

K

Control

Logic

Address

Register

D

[17:0]

Read Add.

Dec

ode

Read Data Reg.

LD

Q

[17:0]

Control

Logic

Reg.

Reg.

Reg.

18

18

36

Write

18

BWS

0

V

REF

W

r

it

e A

dd.

Decode

Data Reg

Write

Data Reg

Memory

Array

512K x 18

Memory

Array

18

18

19

18

C

C

BWS

1

R/W

LD

R/W

CQ

CQ

Logic Block Diagram (CY7C1394V18)

256K x 36

CLK

A

(17:0)

Gen.

K

K

Control

Logic

Address

Register

D

[35:0]

Read Add

.

Decode

Read Data Reg.

LD

Q

[35:0]

Control

Logic

Reg.

Reg.

Reg.

36

36

72

Write

36

BWS

[3:0]

V

REF

W

r

i

t

e Add.

Dec

ode

Data Reg

Write

Data Reg

Memory

Array

256K x 36

Memory

Array

36

36

18

36

C

C

R/W

LD

R/W

CQ

CQ

PRELIMINARY

CY7C1392V18

CY7C1393V18

CY7C1394V18

Document #: 38-05179 Rev. *A

Page 3 of 24

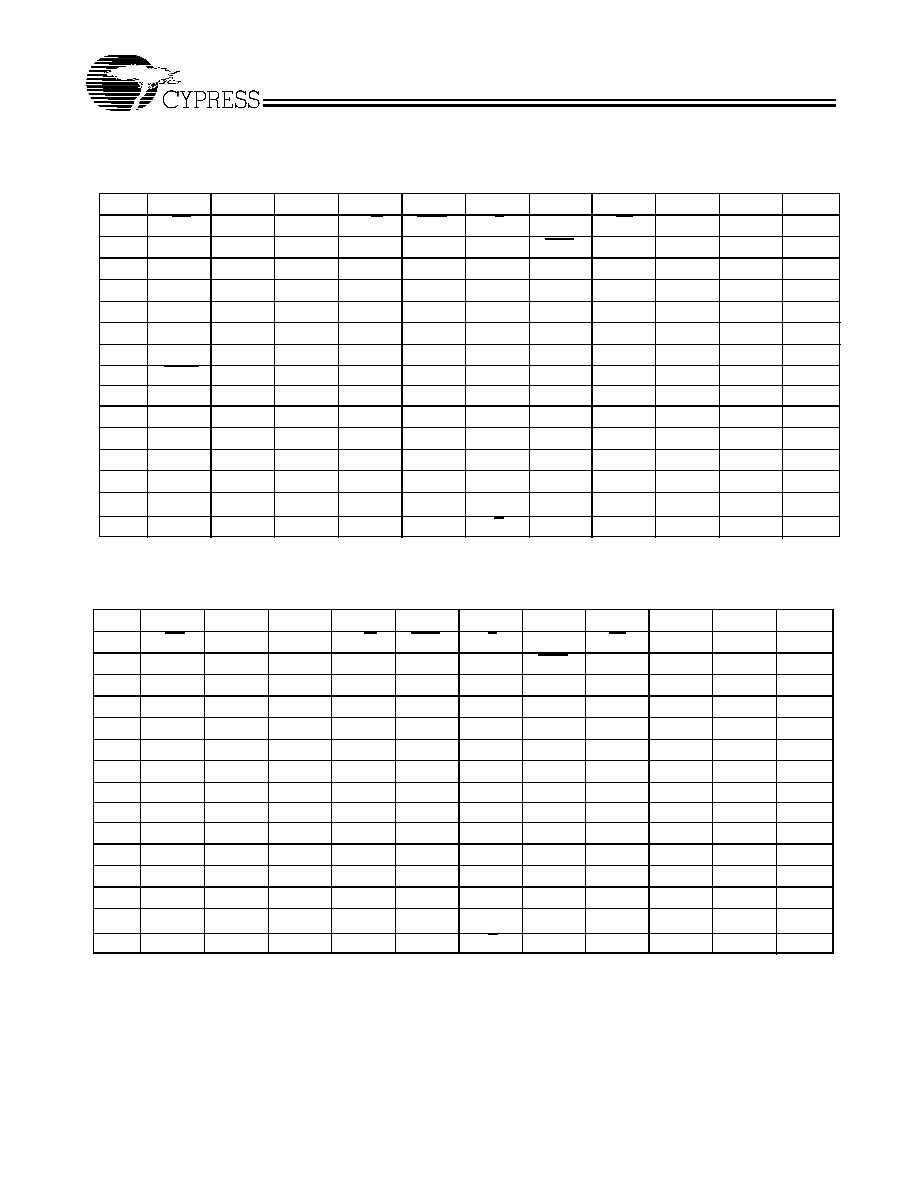

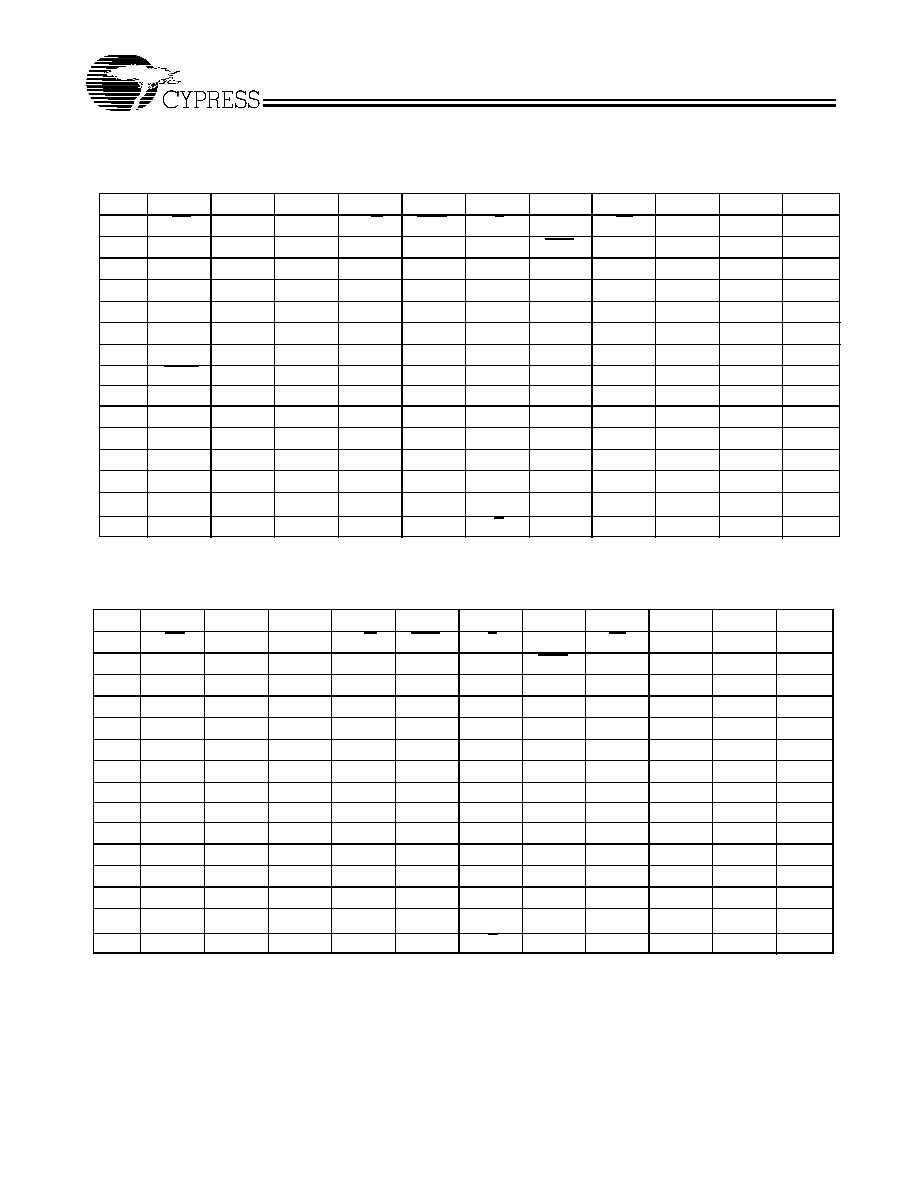

Pin Configurations

CY7C1392V18 (2M x 8) - 11 x 15 FBGA

2

3

4

5

6

7

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

A

CQ

NC

NC

NC

NC

DOFF

NC

V

SS

/72M

A

BWS

1

K

R/W

NC

NC

NC

NC

NC

NC

TDO

NC

NC

D5

NC

NC

NC

TCK

NC

NC

A NC

K

BWS

0

V

SS

A

A

A

NC

V

SS

V

SS

V

SS

V

SS

V

DD

A

V

SS

V

SS

V

SS

V

DD

Q4

NC

V

DDQ

NC

NC

NC

NC

Q7

A

V

DDQ

V

SS

V

DDQ

V

DD

V

DD

Q5

V

DDQ

V

DD

V

DDQ

V

DD

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

SS

V

SS

V

SS

V

SS

A

A

C

V

SS

A

A

A

D4

V

SS

NC

V

SS

NC

NC

V

REF

V

SS

V

DD

V

SS

V

SS

A

V

SS

C

NC

Q6

NC

D7

D6

V

DD

A

8

9

10

11

NC

A

V

DD

/36M

LD

CQ

A NC

NC

Q3

V

SS

NC

NC

D3

NC

V

SS

NC

Q2

NC

NC

NC

V

REF

NC

NC

V

DDQ

NC

V

DDQ

NC

NC

V

DDQ

V

DDQ

V

DDQ

D1

V

DDQ

NC

Q1

NC

V

DDQ

V

DDQ

NC

V

SS

NC

D0

NC

TDI

TMS

V

SS

A

NC

A

NC

D2

NC

ZQ

NC

Q0

NC

NC

NC

NC

A

CY7C1393V18 (1M x 18) - 11 x 15 FBGA

2

3

4

5

6

7

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

A

CQ

NC

NC

NC

NC

DOFF

NC

V

SS

/144M NC/36M

BWS

1

K

R/W

NC

Q9

D9

NC

NC

NC

TDO

NC

NC

D13

NC

NC

NC

TCK

NC

D10

A NC

K

BWS

0

V

SS

A

A

A

Q10

V

SS

V

SS

V

SS

V

SS

V

DD

A

V

SS

V

SS

V

SS

V

DD

Q11

D12

V

DDQ

D14

Q14

D16

Q16

Q17

A

V

DDQ

V

SS

V

DDQ

V

DD

V

DD

Q13

V

DDQ

V

DD

V

DDQ

V

DD

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

SS

V

SS

V

SS

V

SS

A

A

C

V

SS

A

A

A

D11

V

SS

NC

V

SS

Q12

NC

V

REF

V

SS

V

DD

V

SS

V

SS

A

V

SS

C

NC

Q15

NC

D17

D15

V

DD

A

8

9

10

11

Q0

A

GND/72M

LD

CQ

A NC

NC

Q8

V

SS

NC

Q7

D8

NC

V

SS

NC

Q6

D5

NC

NC

V

REF

NC

Q3

V

DDQ

NC

V

DDQ

NC

Q5

V

DDQ

V

DDQ

V

DDQ

D4

V

DDQ

NC

Q4

NC

V

DDQ

V

DDQ

NC

V

SS

NC

D2

NC

TDI

TMS

V

SS

A

NC

A

D7

D6

NC

ZQ

D3

Q2

D1

Q1

D0

NC

A

PRELIMINARY

CY7C1392V18

CY7C1393V18

CY7C1394V18

Document #: 38-05179 Rev. *A

Page 4 of 24

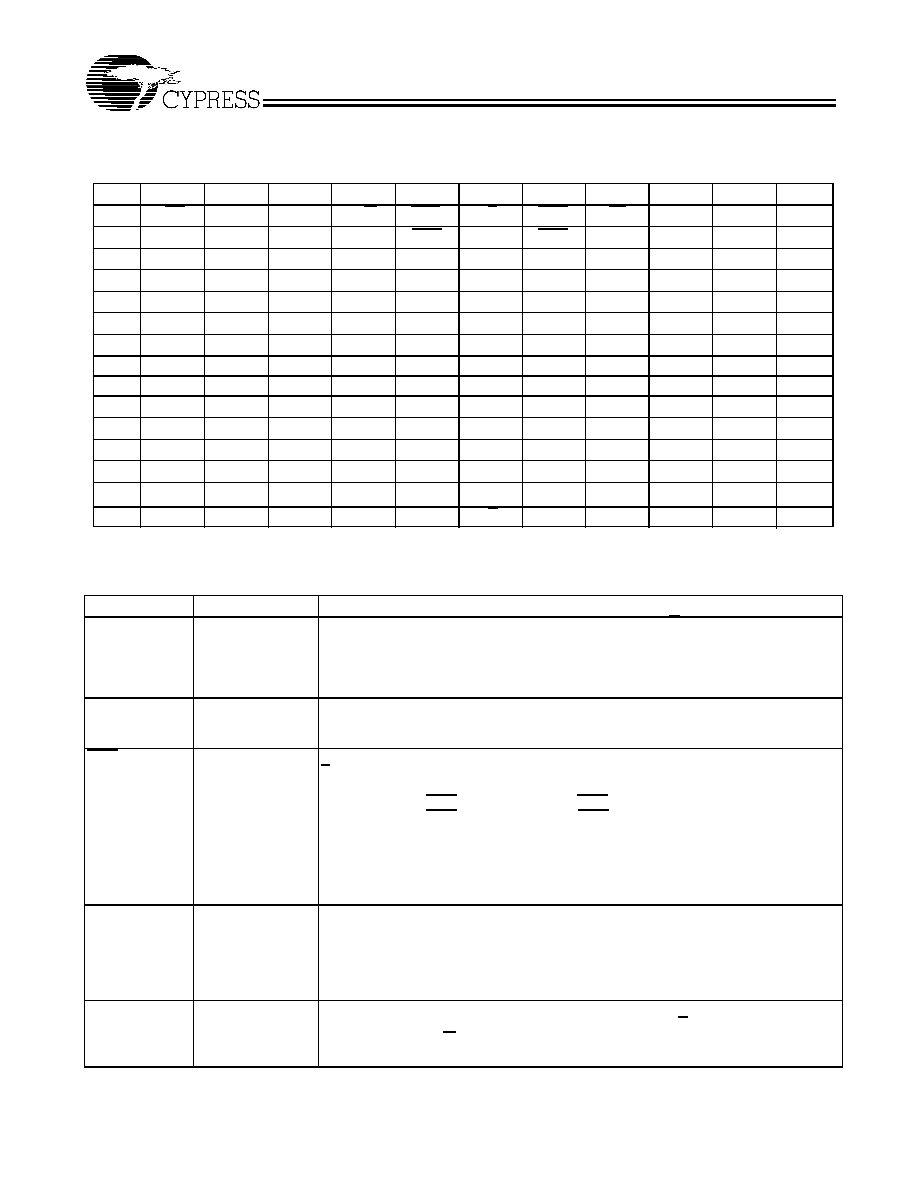

Pin Configurations

(continued)

CY7C1394V18 (512K x 36) - 11 x 15 FBGA

2

3

4

5

6

7

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

A

CQ

Q27

D27

D28

D34

DOFF

Q33

V

SS

/288M NC/72M

BWS

2

K

R/W

BWS

1

Q18

D18

Q30

D31

D33

TDO

Q28

D29

D22

D32

Q34

Q31

TCK

D35

D19

A BWS

3

K

BWS

0

V

SS

A

A

A

Q19

V

SS

V

SS

V

SS

V

SS

V

DD

A

V

SS

V

SS

V

SS

V

DD

Q20

D21

V

DDQ

D23

Q23

D25

Q25

Q26

A

V

DDQ

V

SS

V

DDQ

V

DD

V

DD

Q22

V

DDQ

V

DD

V

DDQ

V

DD

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

SS

V

SS

V

SS

V

SS

A

A

C

V

SS

A

A

A

D20

V

SS

Q29

V

SS

Q21

D30

V

REF

V

SS

V

DD

V

SS

V

SS

A

V

SS

C

Q32

Q24

Q35

D26

D24

V

DD

A

8

9

10

11

Q0

NC/36M V

SS

/144M

LD

CQ

A D17

Q17

Q8

V

SS

D16

Q7

D8

Q16

V

SS

D15

Q6

D5

D9

Q14

V

REF

Q11

Q3

V

DDQ

Q15

V

DDQ

D14

Q5

V

DDQ

V

DDQ

V

DDQ

D4

V

DDQ

D12

Q4

Q12

V

DDQ

V

DDQ

D11

V

SS

D10

D2

Q10

TDI

TMS

V

SS

A

Q9

A

D7

D6

D13

ZQ

D3

Q2

D1

Q1

D0

Q13

A

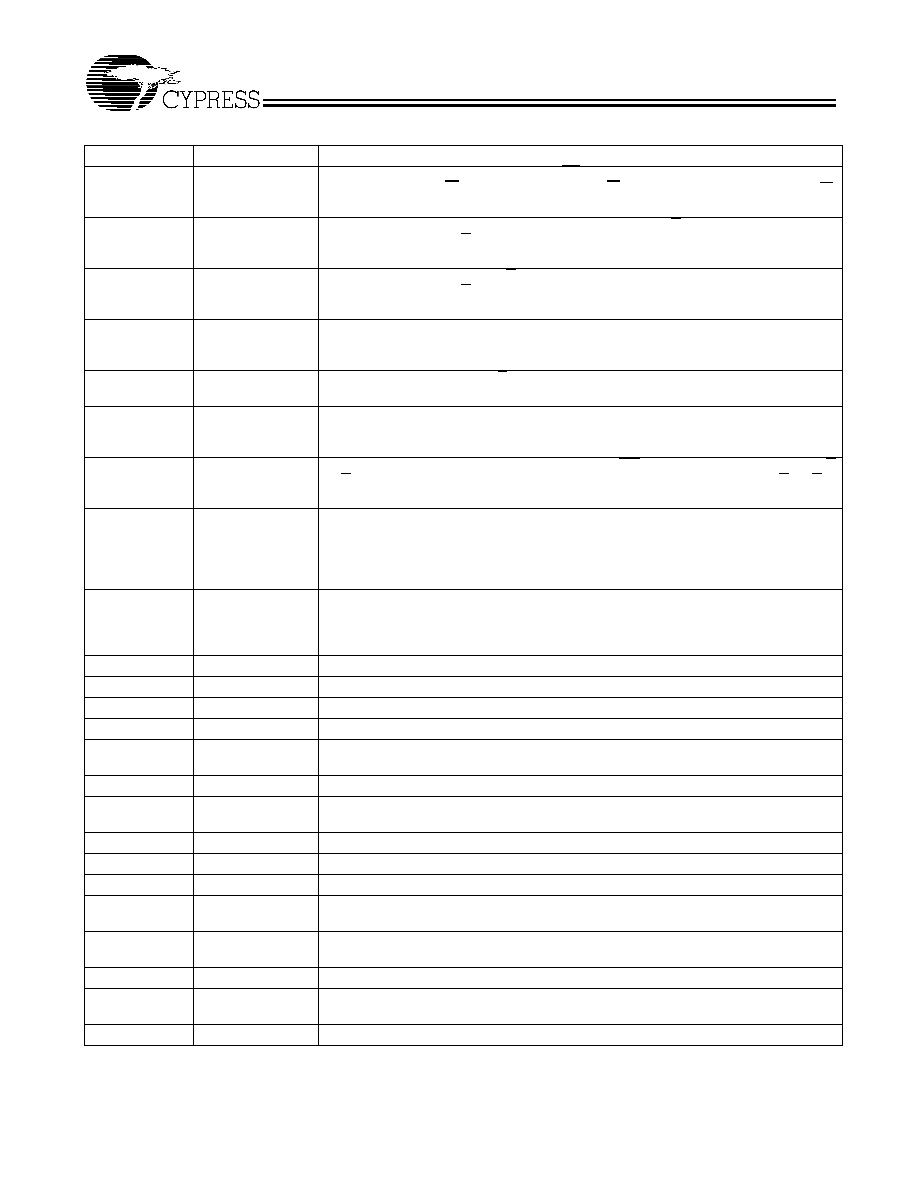

Pin Definitions

Pin Name

I/O

Pin Description

D

[x:0]

Input-

Synchronous

Data input signals, sampled on the rising edge of K and K clocks during valid write

operations.

CY7C1392V18

-

DQ

[7:0]

CY7C1393V18

-

DQ

[17:0]

CY7C1394V18

-

DQ

[35:0]

LD

Input-

Synchronous

Synchronous Load: This input is brought LOW when a bus cycle sequence is to be

defined. This definition includes address and read/write direction. All transactions

operate on a burst of 2 data (one period of bus activity).

BWS

[3:0]

Input-

Synchronous

Byte Write Select 0, 1, 2, and 3

-

active LOW. Sampled on the rising edge of the K and

K clocks during write operations. Used to select which byte is written into the device

during the current portion of the write operations. Bytes not written remain unaltered.

CY7C1392V18

-

BWS

0

controls D

[3:0]

and BWS

1

controls D

[7:4]

.

CY7C1393V18

-

BWS

0

controls D

[8:0]

and BWS

1

controls D

[17:9].

CY7C1394V18

-

BWS

0

controls D

[8:0]

, BWS

1

controls D

[17:9]

, BWS

2

controls D

[26:18]

and

BWS

3

controls D

[35:27]

All the byte writes are sampled on the same edge as the data. Deselecting a Byte Write

Select will cause the corresponding byte of data to be ignored and not written into the

device.

A

Input-

Synchronous

Address Inputs. Sampled on the rising edge of the K clock during active read and write

operations. These address inputs are multiplexed for both Read and Write operations.

Internally, the device is organized as 2M x 8 (2 arrays each of 1M x 8) for CY7C1392V18,

1M x 18 (2 arrays each of 512K x 18) for CY7C1393V18 and 512K x 36 (2 arrays each

of 256K x 36) for CY7C1394V18.

All the address inputs are ignored when the appropriate port is deselected.

Q

[x:0]

Outputs-

Synchronous

Data Output signals. These pins drive out the requested data during a Read operation.

Valid data is driven out on the rising edge of both the C and C clocks during Read

operations or K and K when in single clock mode. When the Read port is deselected,

Q

[x:0]

are automatically three-stated.

PRELIMINARY

CY7C1392V18

CY7C1393V18

CY7C1394V18

Document #: 38-05179 Rev. *A

Page 5 of 24

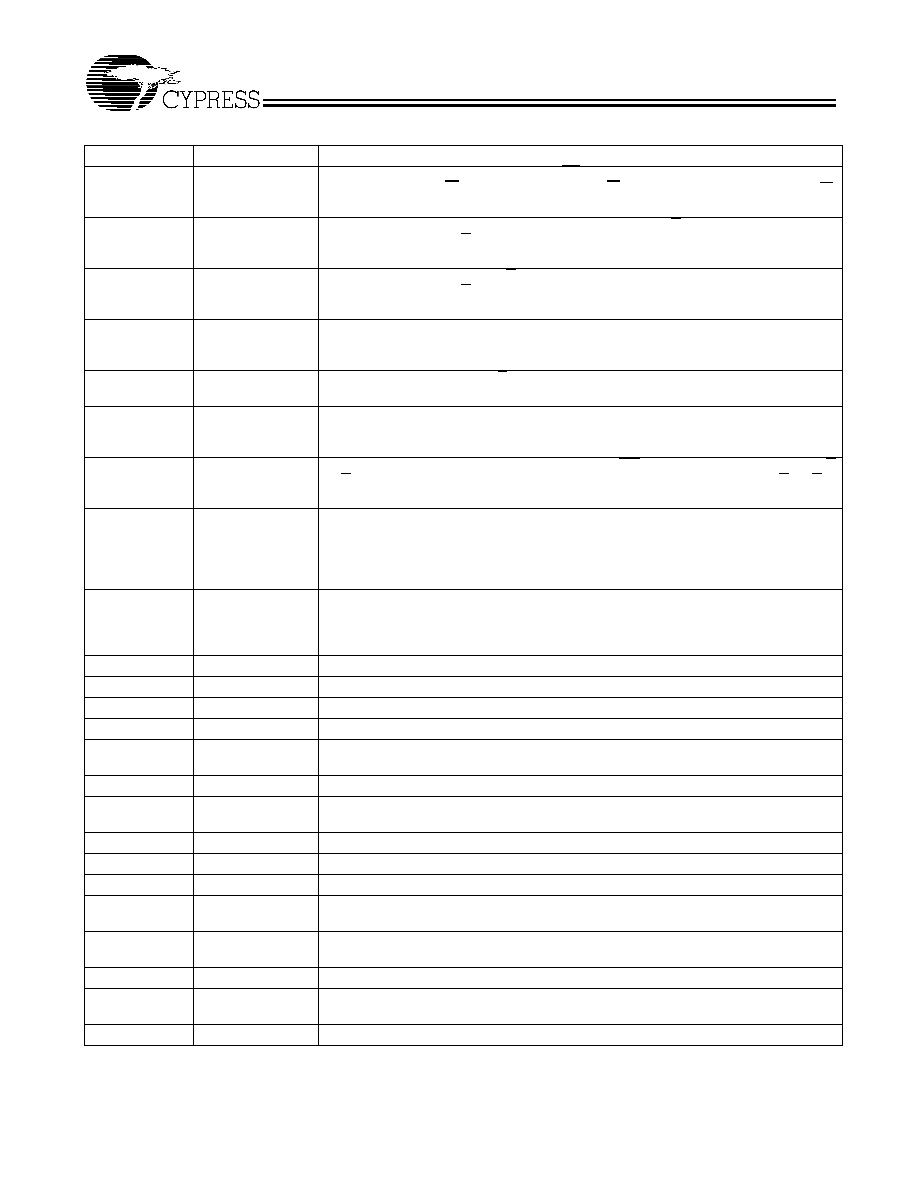

R/W

Input-

Synchronous

Synchronous Read/Write Input: When LD is LOW, this input designates the access

type (Read when R/W is HIGH, Write when R/W is LOW) for loaded address. R/W

must meet the set-up and hold times around edge of K.

C

Input-

Clock

Positive Output Clock Input. C is used in conjunction with C to clock out the Read data

from the device. C and C can be used together to deskew the flight times of various

devices on the board back to the controller. See application example for further details.

C

Input-

Clock

Negative Output Clock Input. C is used in conjunction with C to clock out the Read data

from the device. C and C can be used together to deskew the flight times of various

devices on the board back to the controller. See application example for further details.

K

Input-

Clock

Positive Input Clock Input. The rising edge of K is used to capture synchronous inputs

to the device and to drive out data through Q

[x:0]

when in single clock mode. All accesses

are initiated on the rising edge of K.

K

Input-

Clock

Negative Input Clock Input. K is used to capture synchronous inputs being presented

to the device and to drive out data through Q

[x:0]

when in single clock mode.

CQ

Input-

Clock

Positive Output Echo Clock. The rising edge of CQ is synchronous with respect to C

(or K in single clock mode) and is used for data valid indication coming off of C (or K)

clock. This is a free-running clock.

CQ

Input-Clock

Negative Output Echo Clock. The rising edge of CQ is synchronous with respect to C

(or K in single clock mode) and is used for data valid indication coming off of C (or K)

clock. This is a free-running clock.

ZQ

Input

Output Impedance Matching Input. This input is used to tune the device outputs to the

system data bus impedance. Q

[x:0]

output impedance are set to 0.2 x RQ, where RQ is

a resistor connected between ZQ and ground. Alternately, this pin can be connected

directly to V

DD

, which enables the minimum impedance mode. This pin cannot be

connected directly to GND or left unconnected.

DOFF

Input

DLL Turn Off. Connecting this pin to ground will turn off the DLL inside the device. The

timings in the DLL turned off operation will be different from those listed in this data sheet.

More details on this operation can be found in the application note, "DLL Operation in

the QDR

TM

-II."

TDO

Output

TDO for JTAG.

TCK

Input

TCK pin for JTAG.

TDI

Input

TDI pin for JTAG.

TMS

Input

TMS pin for JTAG.

NC/36M

Input

Address expansion for 36M. This is a No connect on the 18M and could be tied to any

level on the 18M devices

GND/36M

Input

Address expansion for 36M. This should be tied LOW on the 18M devices.

NC/72M

Input

Address expansion for 72M. This is a No connect on the 18M and could be tied to any

level on the 18M devices

V

SS

/72M

Input

Address expansion for 72M. This must be tied LOW on the 18M SRAM.

V

SS

/144M

Input

Address expansion for 144M. This must be tied LOW on the 18M SRAM.

V

SS

/288M

Input

Address expansion for 288M. This must be tied LOW on the 18M SRAM.

V

REF

Input-

Reference

Reference Voltage Input. Static input used to set the reference level for HSTL inputs

and Outputs as well as A/C measurement points.

V

DD

Power Supply

Power supply inputs to the core of the device. Should be connected to 1.8V power

supply.

V

SS

Ground

Ground for the device. Should be connected to ground of the system.

V

DDQ

Power Supply

Power supply inputs for the outputs of the device. Should be connected to 1.5V

power supply.

NC

NC

No connect.

Pin Definitions

(continued)

Pin Name

I/O

Pin Description