PRELIMINARY

9-Mbit (256K x 36/512K x 18) Flow-Through SRAM

CY7C1361C

CY7C1363C

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose

,

CA 95134

·

408-943-2600

Document #: 38-05541 Rev. *A

Revised October 5, 2004

Features

· Supports 133-MHz bus operations

· 256K × 36/512K × 18 common I/O

· 3.3V 5% and +10% core power supply (V

DD

)

· 2.5V or 3.3V I/O supply (V

DDQ

)

· Fast clock-to-output times

-- 6.5 ns (133-MHz version)

-- 7.5 ns (117-MHz version)

-- 8.5 ns (100-MHz version)

· Provide high-performance 2-1-1-1 access rate

· User-selectable burst counter supporting Intel

Pentium

interleaved or linear burst sequences

· Separate processor and controller address strobes

· Synchronous self-timed write

· Asynchronous output enable

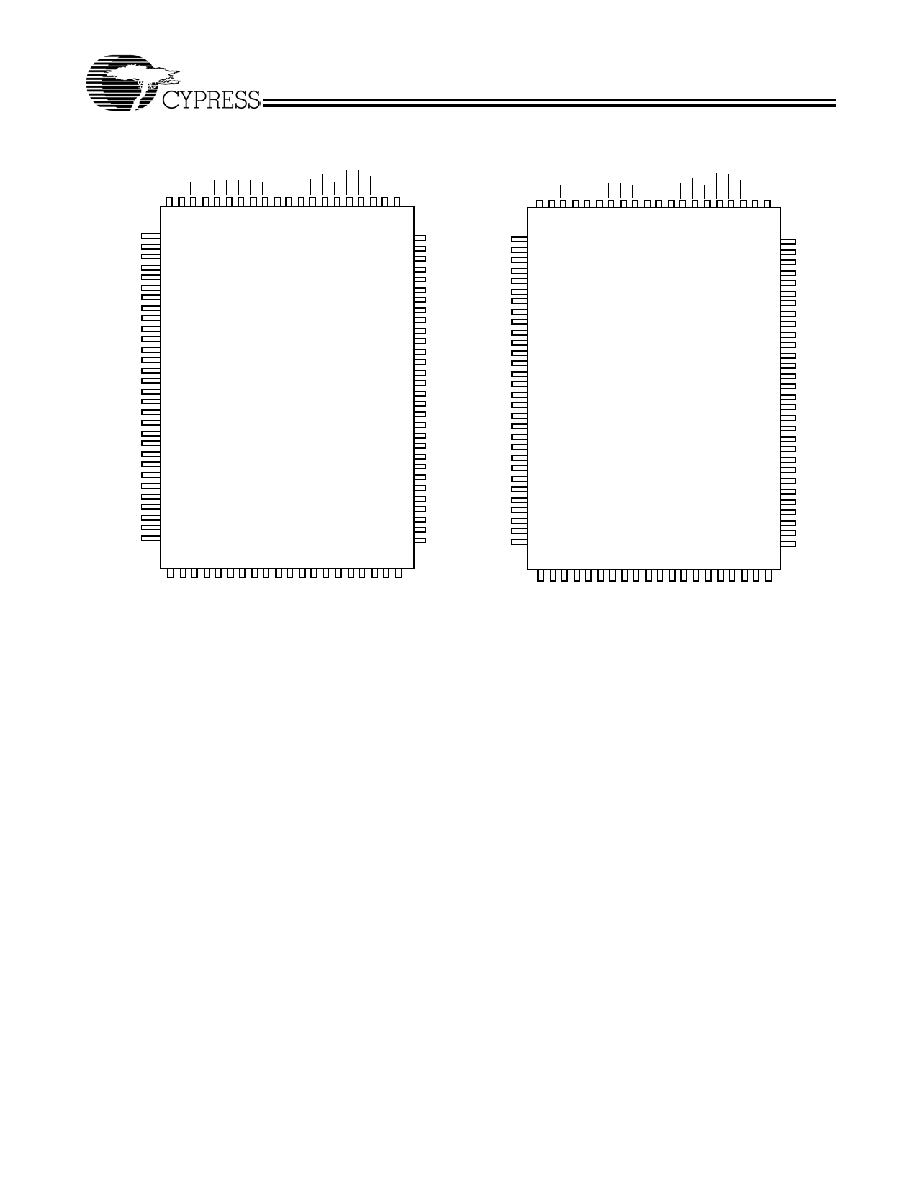

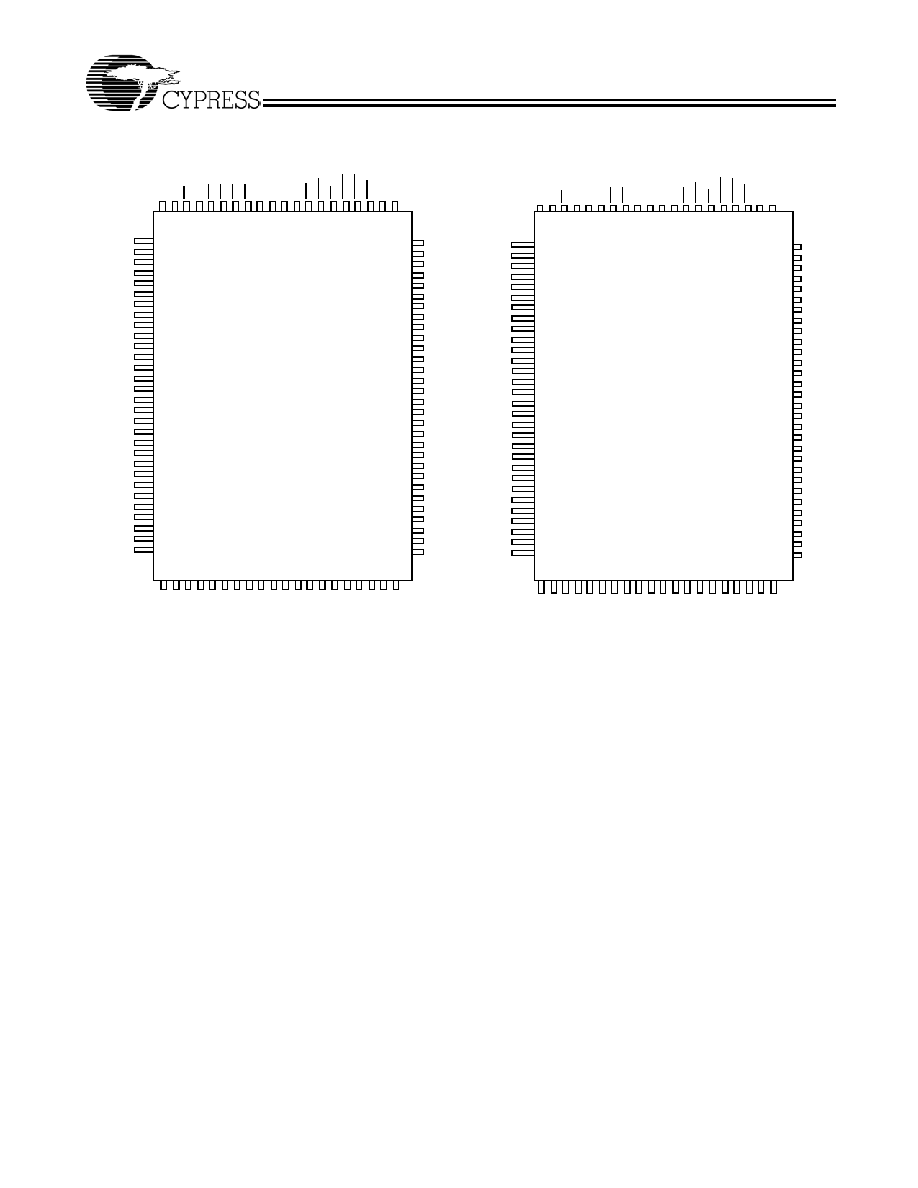

· Available in Lead-Free 100 TQFP,119 BGA and 165 fBGA

packages Both 2 and 3 Chip Enable Options for TQFP

· IEEE 1149.1 compatible JTAG Boundary Scan for BGA

and fBGA packages

·"ZZ" Sleep Mode option

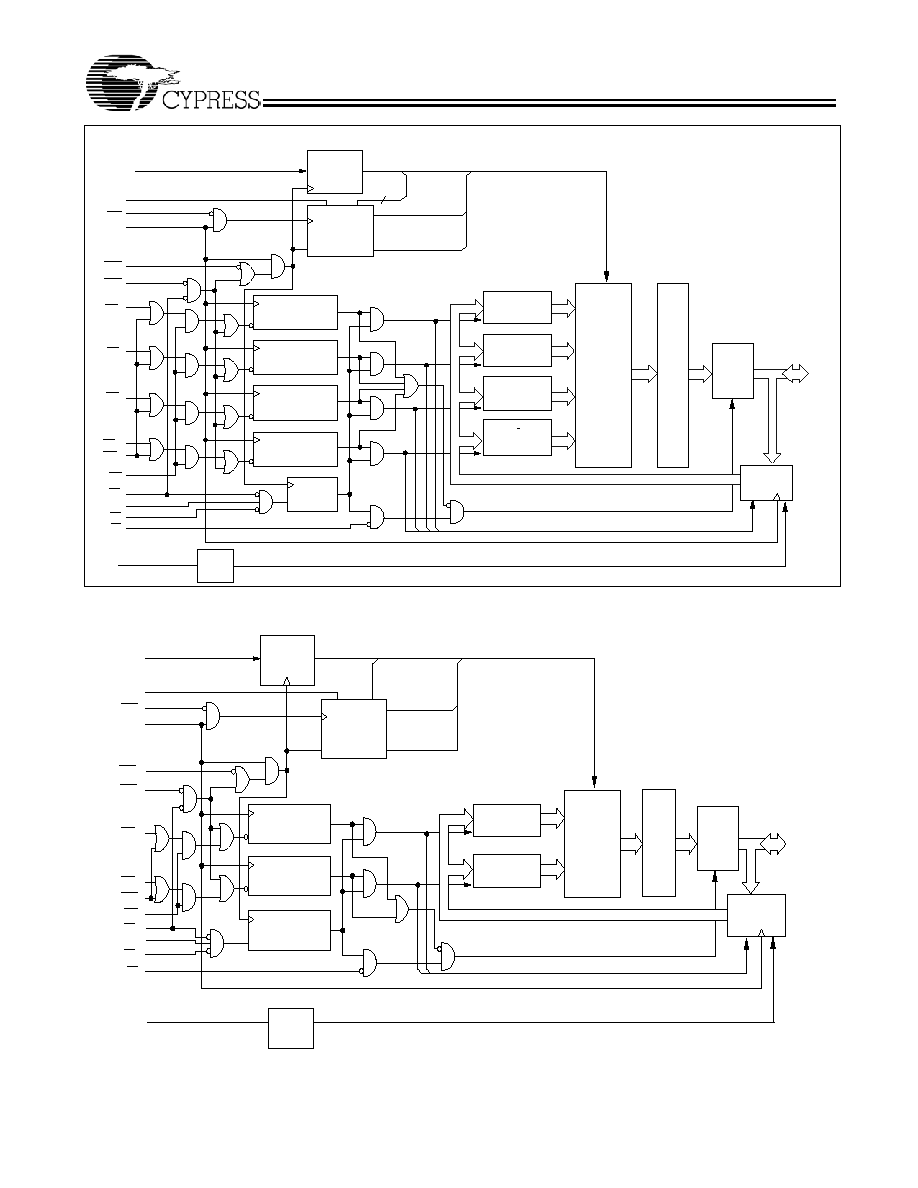

Functional Description

[1]

The CY7C1361C/CY7C1363C is a 3.3V, 256K x 36 and 512K x

18 Synchronous Flowthrough SRAMs, respectively designed

to interface with high-speed microprocessors with minimum

glue logic. Maximum access delay from clock rise is 6.5 ns

(133-MHz version). A 2-bit on-chip counter captures the first

address in a burst and increments the address automatically

for the rest of the burst access. All synchronous inputs are

gated by registers controlled by a positive-edge-triggered

Clock Input (CLK). The synchronous inputs include all

addresses, all data inputs, address-pipelining Chip Enable

(CE

1

), depth-expansion Chip Enables (CE

2

and

CE

3

[2]

), Burst

Control inputs (ADSC, ADSP, and ADV), Write Enables (BW

x

,

and BWE), and Global Write (GW). Asynchronous inputs

include the Output Enable (OE) and the ZZ pin.

The CY7C1361C/CY7C1363C allows either interleaved or

linear burst sequences, selected by the MODE input pin. A

HIGH selects an interleaved burst sequence, while a LOW

selects a linear burst sequence. Burst accesses can be

initiated with the Processor Address Strobe (ADSP) or the

cache Controller Address Strobe (ADSC) inputs. Address

advancement is controlled by the Address Advancement

(ADV) input.

Addresses and chip enables are registered at rising edge of

clock when either Address Strobe Processor (ADSP) or

Address Strobe Controller (ADSC) are active. Subsequent

burst addresses can be internally generated as controlled by

the Advance pin (ADV).

The CY7C1361C/CY7C1363C operates from a +3.3V core

power supply while all outputs may operate with either a +2.5

or +3.3V supply. All inputs and outputs are JEDEC-standard

JESD8-5-compatible.

Selection Guide

133 MHz

117 MHz

100 MHz

Unit

Maximum Access Time

6.5

7.5

8.5

ns

Maximum Operating Current

250

220

180

mA

Maximum CMOS Standby Current

30

30

30

mA

Notes:

1. For bestpractices recommendations, please refer to the Cypress application note System Design Guidelines on www.cypress.com.

2. CE

3

is for A version of TQFP ( 3 Chip Enable Option) and 165 fBGA package only. 119 BGA is offered only in 2 Chip Enable.