1

Features

À

Data Rate up to 50 MHz (2 Outputs at 25 MHz Each)

À

Pixel Size: 10 Ám x 10 Ám (10 Ám Pitch)

À

300 to 1100 nm Spectral Range

À

High Sensitivity and Lag Free Photodiodes

À

Very Low Noise (30 pJ/cm

2

Noise Equivalent Illumination)

À

Antiblooming

À

Exposure Control

À

20-lead 0.4" DIL Package

Description

TH7815 linear arrays are based on Atmel's most recent technology in terms of design

and performance. The flexibility and performance of these devices provide the oppor-

tunity to use them in most vision systems for industrial applications (web inspection,

process control, sorting and inspection of various parts), document scanning up to

200 dpi and metrology.

Pin Identification

All pins must be connected.

Pin Number

Symbol

Function

4, 17

VDD1,2

Output Amplifiers Drain Supply

3, 18

VOS1,2

Video Outputs

5

VS

Output Amplifiers Substate Bias

20

VDR

Reset Drain Supply

2

VGS

Output Gate Bias

14

L1

Readout Register Clocks

13

L2

15

R

Reset Clock

10

A

Antiblooming Gate Bias/Clock

7

VA

Antiblooming Drain Bias

8

VST

Storage Gate Bias

11

P

Transfer Gate Clock

1, 6, 9, 12, 16, 19

VSS

Ground, Optical Grounding (Internally Connected)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VSS

VGS

VOS1

VDD1

VS

VSS

VA

VST

VSS

A

VDR

VSS

VOS2

VDDR

VSS

R

L1

L2

VSSP

TH7815ACC

50 MHz 4096

Linear CCDs

TH7815ACC

Rev. 1995A¡IMAGE¡04/02

2

TH7815ACC

1995A¡IMAGE¡04/02

Operating

Precautions

Shorting the video outputs to any other pin, even temporarily, can permanently damage

the on-chip output amplifier.

Absolute Maximum Ratings*

Storage Temperature Range ......................... -55░C to +150░C

Note:

Stresses above those listed under absolute maximum

ratings may cause permanent device failure. Func-

tionally at or above these limits is not implied.

Exposure to absolute maximum ratings for extended

periods may affect device reliability.

¡

Operating range defines the limits within

which the functionality is guaranteed.

¡

Electrical limits of applied signals are given

in operating conditions section.

Operating Temperature Range........................ -40░C to +85░C

Thermal Cycling........................................................ 15░C/min

Maximum Applied Voltages:

À Pins 2, 8, 10, 11, 13, 14, 15 ................................. -0.3 to 15V

À Pins 4, 5, 7, 17, 20 .............................................. -0.3 to 16V

À Pins 1, 6, 9, 12, 16, 19 ........................................0V (ground)

3

TH7815ACC

1995A¡IMAGE¡04/02

Operating Conditions

Table 1. DC Characteristics

Parameter

Symbol

Value

Unit

Min.

Typ.

Max.

Output Amplifier Drain Supply

VDD1, VDD2

14.5

15

15.5

V

Storage Gate Bias

VST

2.2

2.4

2.6

V

Antiblooming Gate (See Pixel

Saturation Adjustment)

A

2

4

7

V

Reset Bias

VDR

13.5

14

14.5

V

Antiblooming Diode Bias

VA

14.5

15

15.5

V

Register Output Gate Bias

VGS

2.2

2.4

2.6

V

Output Amplifier Source Supply

VS

0

V

Ground

VSS

0

V

Table 2. Drive Clocks Characteristics

Parameter

Symbol

Value

Unit

Remarks

Min.

Typ.

Max.

Reset Gate

High Level

Low Level

R

8.5

-0.1

9

0

9.5

0.4

V

V

Clock Capacitance < 50 pF

Transfer Gate

High Level

Low Level

P

8.5

-0.1

9

0

9.5

0.4

V

V

Clock Capacitance < 200 pF

Readout Register Clocks

High Level

Low Level

L1, 2

8.5

-0.1

9

0

9.5

0.4

V

V

Maximum Readout Register

Frequency

F

H

10

25

MHz

200 pF

500 pF

460 pF

L1

L2

4

TH7815ACC

1995A¡IMAGE¡04/02

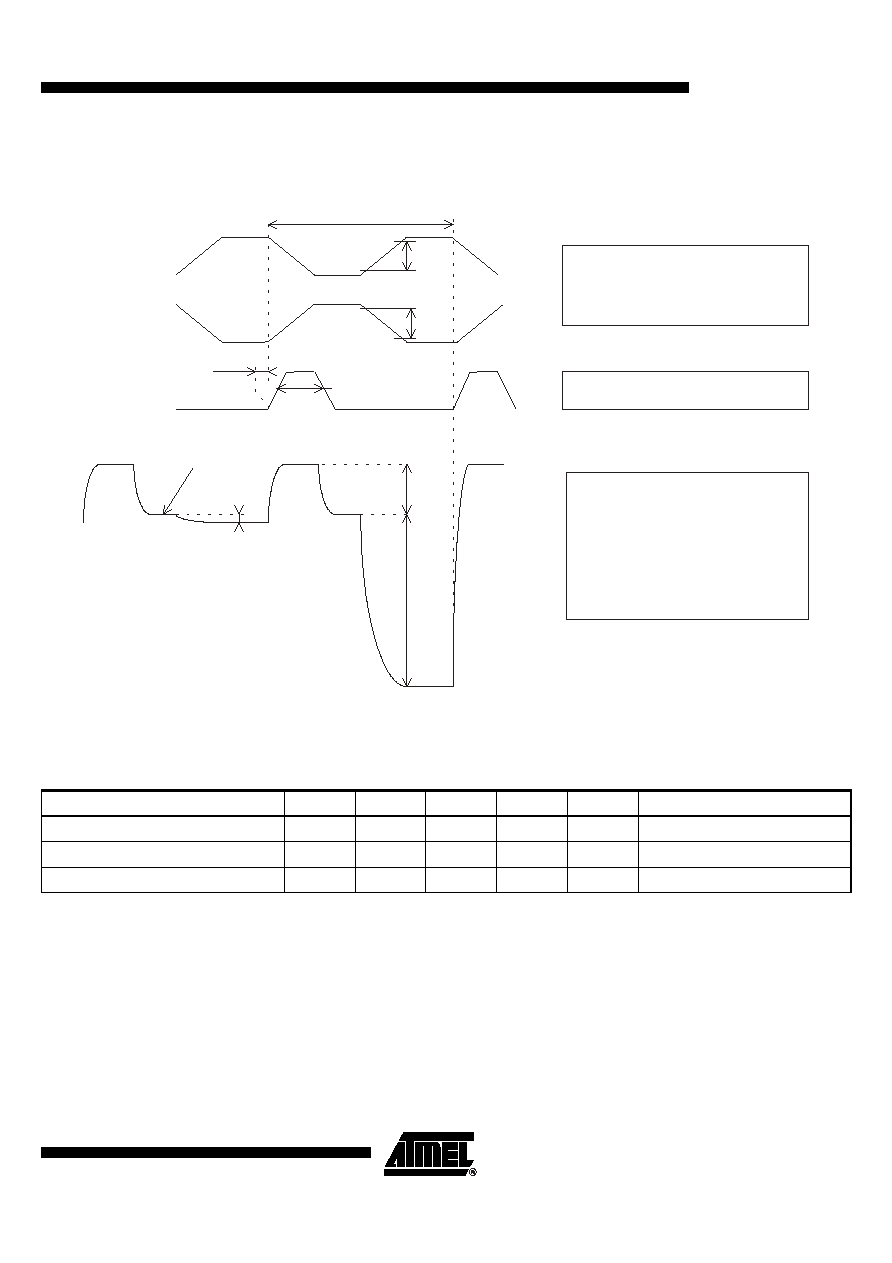

Timing Diagrams

The following diagram shows the general clocking scheme for TH7815ACC.

The line is composed as follows:

Postscan elements may be added in order to either increase the exposure time, or to

provide a voltage reference level.

Figure 1. Line Timing Diagram

The following diagram shows the timing for the transfer period:

Figure 2. Line Transfer Period

R clock may also be held in high state during line transfer period.

Synopsis

Number of Prescan

Pixels Per Output

Number of Useful

Pixels Per Output

Total Number of Pixels

Per Output

TH7815ACC

4

2048

2052

A

P

L1

L2

R

Line Period

Transfer Period

A

P

L1

L2

R

> 300 ns

> 10 ns

> 10 ns

first prescan pixel

(700 ns typ.)

5

TH7815ACC

1995A¡IMAGE¡04/02

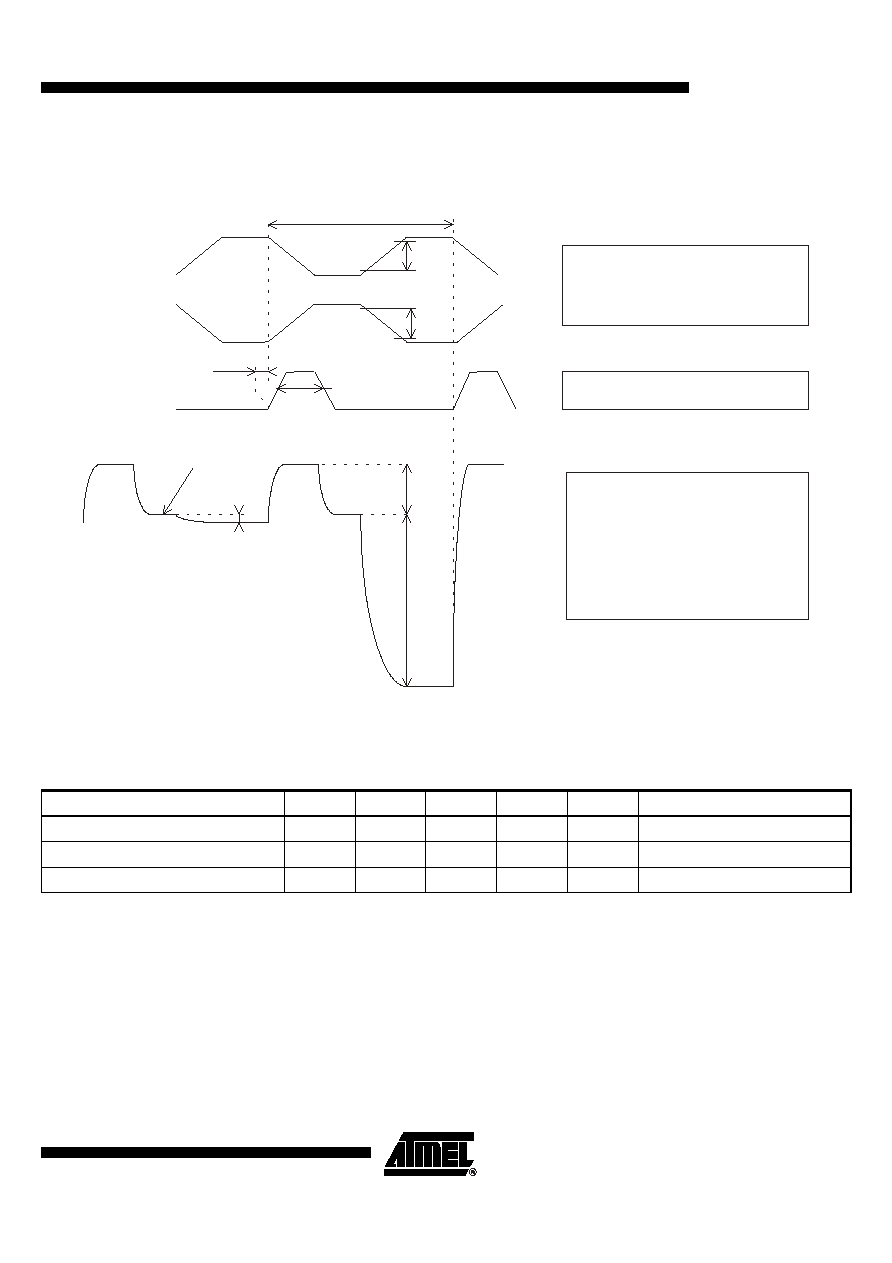

The following diagram shows the detailed timing for the pixel readout:

Figure 3. Pixel Readout Timing Diagram

Exposure Time

Reduction

The TH7815ACC antiblooming structure provides an electronic shutter capability by

clocking phase

A during the line period. The timing diagram is described below:

L1

L2

R

10%

90%

90%

10%

tr

tf

Tpixel

0 ns

10 ns

50%

Video signal

Reset Feedthrough

Offset in darkness

VIDEO OUTPUTS

▒

floating diode level

Duty cycle: 50%

▒

10%

Crossover at 50%

▒

10%

Rise and fall time

10 ns

Rise and fall time

8 ns

Video outputs are synchronous

Video signal occurs on

L2 falling edge

First useful pixel occurs on 5th

falling edge of

L2 after

P

Antiblooming Gate

A

Min.

Typ.

Max.

Unit

Clock Capacitance < 200 pF

High Level

8.5

9

9.5

V

Low Level Sets Saturation Level

Low Level

2

4

7

V

See Pixel Saturation Adjustment

Pulse Min.

200 ns