1

High-

performance

EE PLD

ATF1508ASV

ATF1508ASVL

Features

∑

High-density, High-performance, Electrically-erasable

Complex Programmable Logic Device

≠ 3.0V to 3.6V Operating Range

≠ 128 Macrocells

≠ 5 Product Terms per Macrocell, Expandable up to 40 per Macrocell

≠ 84, 100, 160 Pins

≠ 15 ns Maximum Pin-to-pin Delay

≠ Registered Operation up to 77 MHz

≠ Enhanced Routing Resources

∑

Flexible Logic Macrocell

≠ D/T/Latch Configurable Flip-flops

≠ Global and Individual Register Control Signals

≠ Global and Individual Output Enable

≠ Programmable Output Slew Rate

≠ Programmable Output Open Collector Option

≠ Maximum Logic Utilization by Burying a Register within a COM Output

∑

Advanced Power Management Features

≠ Automatic 5 µA Standby for "L" Version

≠ Pin-controlled 100 µA Standby Mode

≠ Programmable Pin-keeper Inputs and I/Os

≠ Reduced-power Feature per Macrocell

∑

Available in Commercial and Industrial Temperature Ranges

∑

Available in 84-lead PLCC and 100-lead PQFP and TQFP and

160-lead PQFP Packages

∑

Advanced EE Technology

≠ 100% Tested

≠ Completely Reprogrammable

≠ 10,000 Program/Erase Cycles

≠ 20 Year Data Retention

≠ 2000V ESD Protection

≠ 200 mA Latch-up Immunity

∑

JTAG Boundary-scan Testing to IEEE Std. 1149.1-1990 and 1149.1a-1993 Supported

∑

Fast In-System Programmability (ISP) via JTAG

∑

PCI-compliant

∑

Security Fuse Feature

Enhanced Features

∑

Improved Connectivity (Additional Feedback Routing, Alternate Input Routing)

∑

Output Enable Product Terms

∑

Transparent-latch Mode

∑

Combinatorial Output with Registered Feedback within Any Macrocell

∑

Three Global Clock Pins

∑

ITD (Input Transition Detection) Circuits on Global Clocks, Inputs and I/O

∑

Fast Registered Input from Product Term

∑

Programmable "Pin-keeper" Option

∑

V

CC

Power-up Reset Option

∑

Pull-up Option on JTAG Pins TMS and TDI

∑

Advanced Power Management Features

≠ Edge-controlled Power-down "L"

≠ Individual Macrocell Power Option

≠ Disable ITD on Global Clocks, Inputs and I/O for "Z" Parts

Rev. 1408E≠09/00

ATF1508ASV(L)

4

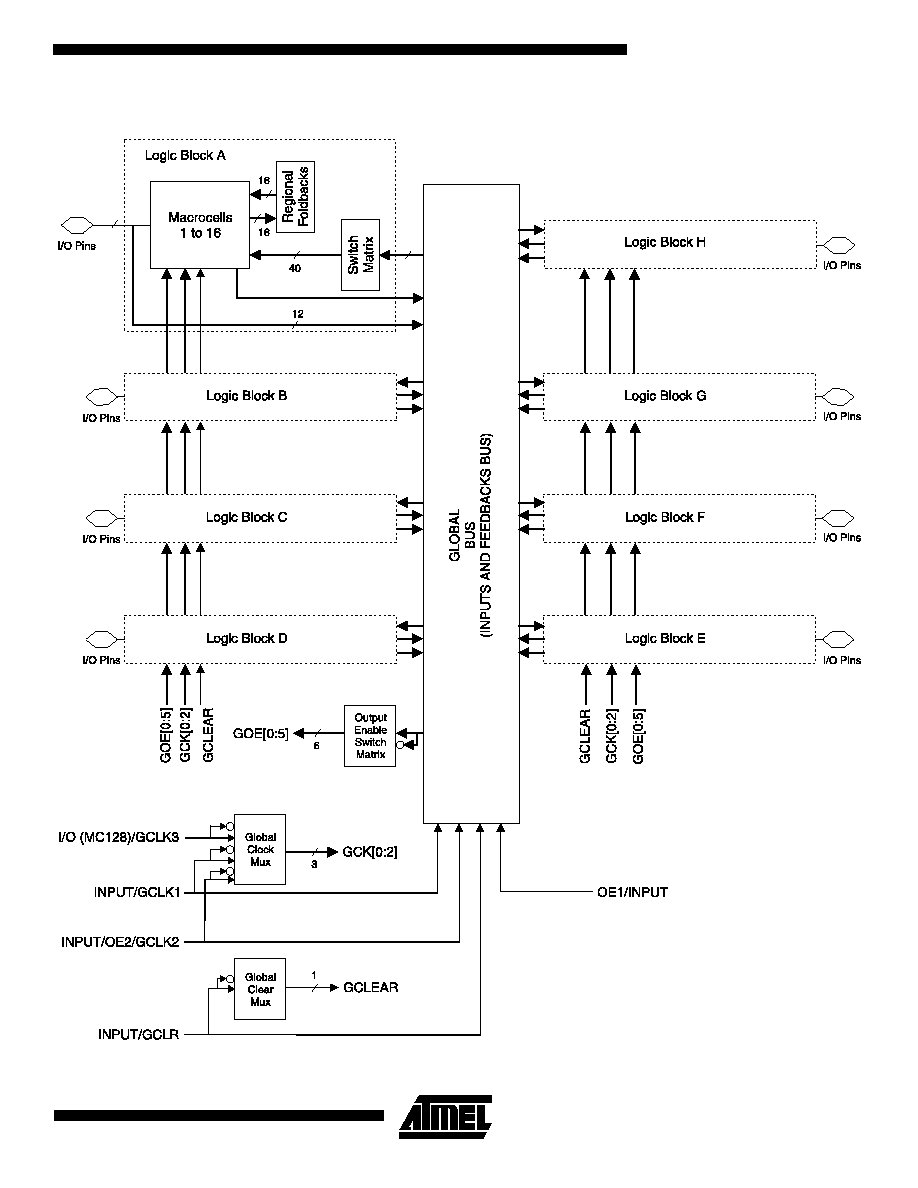

Description

The ATF1508ASV(L) is a high-performance, high-density

complex programmable logic device (CPLD) that utilizes

Atmel's proven electrically-erasable technology. With 128

logic macrocells and up to 100 inputs, it easily integrates

logic from several TTL, SSI, MSI, LSI and classic PLDs.

The ATF1508ASV(L)'s enhanced routing switch matrices

increase usable gate count and increase odds of success-

ful pin-locked design modifications.

The ATF1508ASV(L) has up to 96 bi-directional I/O pins

and four dedicated input pins, depending on the type of

device package selected. Each dedicated pin can also

serve as a global control signal, register clock, register

reset or output enable. Each of these control signals can be

selected for use individually within each macrocell.

Each of the 128 macrocells generates a buried feedback

that goes to the global bus. Each input and I/O pin also

feeds into the global bus. The switch matrix in each logic

block then selects 40 individual signals from the global bus.

Each macrocell also generates a foldback logic term that

goes to a regional bus. Cascade logic between macrocells

in the ATF1508ASV(L) allows fast, efficient generation of

complex logic functions. The ATF1508ASV(L) contains

eight such logic chains, each capable of creating sum term

logic with a fan-in of up to 40 product terms.

The ATF1508ASV(L) macrocell, shown in Figure 1, is flexi-

ble enough to support highly-complex logic functions oper-

ating at high-speed. The macrocell consists of five

sections: product terms and product term select multi-

plexer, OR/XOR/CASCADE logic, a flip-flop, output select

and enable, and logic array inputs.

Unused macrocells are automatically disabled by the com-

piler to decrease power consumption. A security fuse,

w h e n p r o g r a m m e d , p r o t e c t s t h e c o n t e n t s o f t h e

ATF1508ASV(L). Two bytes (16 bits) of User Signature are

accessible to the user for purposes such as storing project

name, part number, revision or date. The User Signature is

accessible regardless of the state of the security fuse.

The ATF1508ASV(L) device is an in-system programmable

(ISP) device. It uses the industry-standard 4-pin JTAG

interface (IEEE Std. 1149.1), and is fully-compliant with

JTAG's Boundary-scan Description Language (BSDL). ISP

allows the device to be programmed without removing it

from the printed circuit board. In addition to simplifying the

manufacturing flow, ISP also allows design modifications to

be made in the field via software.

Product Terms and Select Mux

Each ATF1508ASV(L) macrocell has five product terms.

Each product term receives as its inputs all signals from

both the global bus and regional bus.

The product term select multiplexer (PTMUX) allocates the

five product terms as needed to the macrocell logic gates

and control signals. The PTMUX programming is deter-

mined by the design compiler, which selects the optimum

macrocell configuration.

OR/XOR/CASCADE Logic

The ATF1508ASV(L)'s logic structure is designed to effi-

ciently support all types of logic. Within a single macrocell,

all the product terms can be routed to the OR gate, creating

a 5-input AND/OR sum term. With the addition of the

CASIN from neighboring macrocells, this can be expanded

to as many as 40 product terms with little additional delay.

The macrocell's XOR gate allows efficient implementation

of compare and arithmetic functions. One input to the XOR

comes from the OR sum term. The other XOR input can be

a product term or a fixed high- or low-level. For combinato-

rial outputs, the fixed level input allows polarity selection.

For registered functions, the fixed levels allow DeMorgan

minimization of product terms. The XOR gate is also used

to emulate T- and JK-type flip-flops.

Flip-flop

The ATF1508ASV(L)'s flip-flop has very flexible data and

control functions. The data input can come from either the

XOR gate, from a separate product term or directly from

the I/O pin. Selecting the separate product term allows cre-

ation of a buried registered feedback within a combinatorial

output macrocell. (This feature is automatically imple-

mented by the fitter software). In addition to D, T, JK and

SR operation, the flip-flop can also be configured as a flow-

through latch. In this mode, data passes through when the

clock is high and is latched when the clock is low.

The clock itself can either be the Global CLK Signal (GCK)

or an individual product term. The flip-flop changes state on

the clock's rising edge. When the GCK signal is used as

the clock, one of the macrocell product terms can be

selected as a clock enable. When the clock enable function

is active and the enable signal (product term) is low, all

clock edges are ignored. The flip-flop's asynchronous reset

signal (AR) can be either the Global Clear (GCLEAR), a

product term, or always off. AR can also be a logic OR of

GCLEAR with a product term. The asynchronous preset

(AP) can be a product term or always off.

ATF1508ASV(L)

5

Figure 1. ATF1508ASV(L) Macrocell

Output Select and Enable

The ATF1508ASV(L) macrocell output can be selected as

registered or combinatorial. The buried feedback signal can

be either combinatorial or registered signal regardless of

whether the output is combinatorial or registered.

The output enable multiplexer (MOE) controls the output

enable signals. Any buffer can be permanently enabled for

simple output operation. Buffers can also be permanently

disabled to allow use of the pin as an input. In this configu-

ration. all the macrocell resources are still available,

including the buried feedback, expander and CASCADE

logic. The output enable for each macrocell can be

selected as one of the global OUTPUT enable signals. The

device has six global OE signals.

Global Bus/Switch Matrix

The global bus contains all input and I/O pin signals as well

as the buried feedback signal from all 128 macrocells.

The switch matrix in each logic block receives as its inputs

all signals from the global bus. Under software control, up

to 40 of these signals can be selected as inputs to the logic

block.

Foldback Bus

Each macrocell also generates a foldback product term.

This signal goes to the regional bus and is available to 16

macrocells. The foldback is an inverse polarity of one of the

macrocell's product terms. The 16 foldback terms in each

region allow generation of high fan-in sum terms (up to 21

product terms) with little additional delay.

Open-collector Output Option

This option enables the device output to provide control

signals such as an interrupt that can be asserted by any of

the several devices.