AMCC

200 Brickstone Square, Andover, MA 01810 Ph: (978)-623-0009 Fax:(978)-623-0024

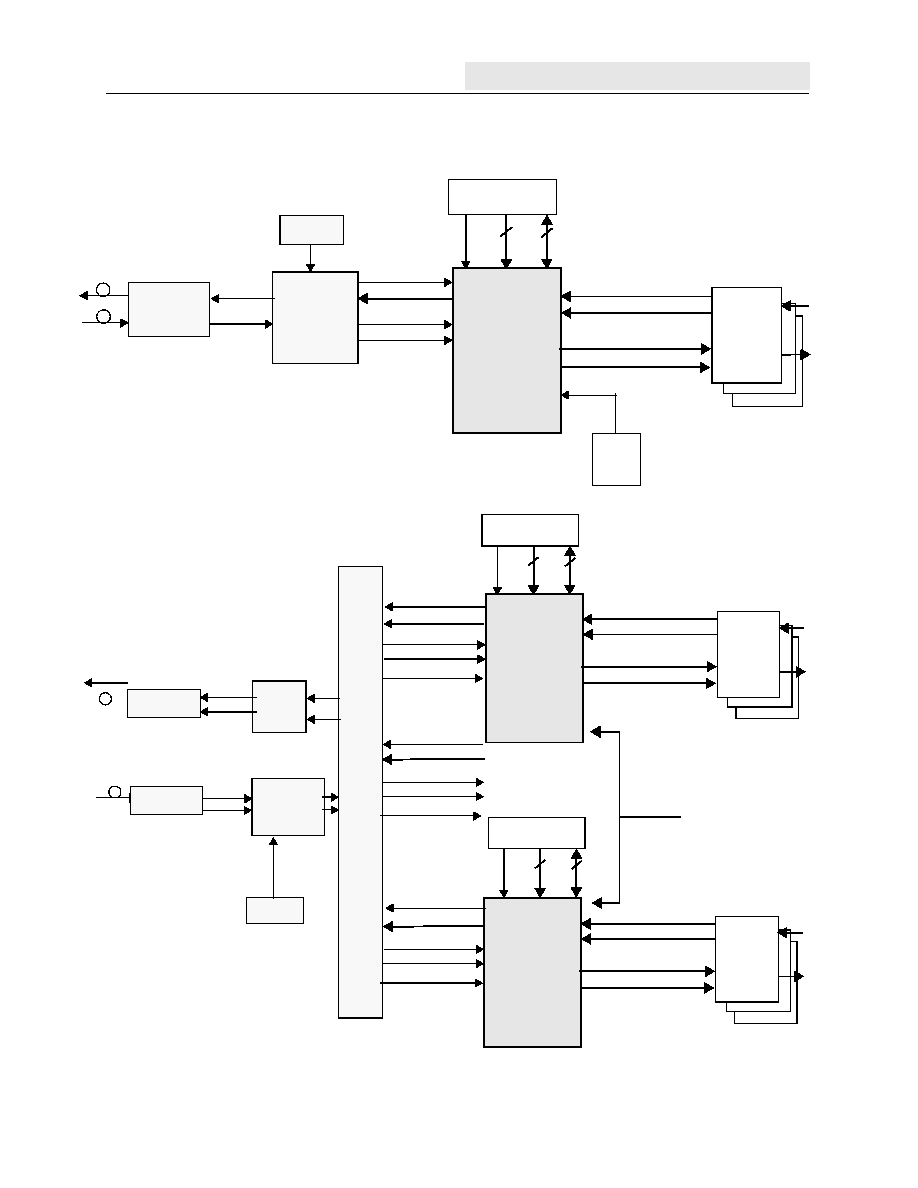

S1204CBI Block Diagram

General Description

STS-12/STM-4 DS3/E3/STS-1E SONET/SDH MAPPER

Part Number - S1204CBI

Product Specification Revision 1.2

Summary Datasheet Version 1.2 - December 2000

Prelimary Information - The information contained in this docu-

ment is about a product in its sample release stage and is subject

to change. All features described herein are design goals. Contact

AMCC for updates to this document and the latest product status.

Orinoco

PRELIMINARY SUMMARY DATASHEET

Features

· Processes any valid combination of SONET/SDH STS-1/

AU-3 or TUG-3/AU-4 tributaries in STS-12/STM-4 or

STS-3/STM-1.

· Terminates/generates SONET/SDH section, line, and

path OH

· Provides on the SONET/SDH side a serial 622 MHz or a

77.76 MHz 8-bit interface for STS-12/STM-4

applications; or a serial 155.52 MHz interface for STS-3/

STM-1 applications.

· Supports flexible assignment of STS-1E and DS3 or

STS-1E and E3 mappings on a per tributary basis.

· Provides STS-1E mapping/demapping for up to 12 STS-

1s.

· Provides DS3 or E3 mapping/demapping for up to 12

tributaries, through SONET STS1, SDH AU-3, and/or

TUG-3/AU-4 containers.

· Supports mixed M23 and C-bit parity DS3 frame formats

on a per-tributary basis.

· Supports mixed G.751 and G.832 E3 frame formats on a

per-tributary basis.

· Supports full-featured DS3/E3/STS-1E performance

monitoring in both transmit and receive directions.

· 12 serial clock/data ports are provided on the system

side for DS3/E3/STS-1E interfaces.

· Integrates DS3/E3 desynchronizer circuitry necessary to

provide DS3/E3 clear channel outputs that meet Bellcore,

ANSI and ITU jitter requirements.

· 622/155 MHz APS interface for redundancy applications.

· Loopback capability for SONET/SDH and DS3/E3/STS-

1Es data streams.

The ORINOCO is a highly integrated chip that

implements SONET/SDH processing and DS3/E3/STS-

1E mapping functions for an STS-12/STM-4 or STS-3/

STM-1 data stream. The ORINOCO is compliant with

the following standards: Bellcore GR-253, GR-499 and

GR-820; ANSI T1.105 and T1.107; and ITU G.751-2;

G.775, G.783, G.804, G.823-5, and G.832.

The ORINOCO supports full-duplex processing of

SONET/SDH data streams with section, line, & path

overhead processing. The device supports framing,

scrambling/descrambling, alarm signal insertion/

detection, and bit interleaved parity (B1/B2/B3)

processing. Serial interfaces for E1, E2, F1 and Line and

Section DCC are also provided.

A general purpose microprocessor interface is provided

for device initialization, control, and monitoring. This

interface can operate either as an 8-bit asynchronous

interface, or a 16-bit synchronous interface. The

interface supports both Intel and Motorola type

microprocessors, and is capable of operating in either an

interrupt driven or polled-mode configuration.

PTR

POH

MONITOR

TOH DROP

TOH

MON

RX

FRAMER

LI

NE SI

DE I

N

T

E

R

F

ACE

TX

FRAMER

TOH INSERT

SPE/VC

GENERATE

T

X

_T

OH

_D

A

T

A_

I

N

T

X

_T

OH

_C

LK_

O

U

T

T

X

_

T

O

H

_F

R

M

_O

U

T

R

X

_T

OH

_D

A

T

A_

OU

T

R

X

_

T

O

H

_C

LK

_

O

U

T

RX

_

T

O

H

_

F

RM

_

O

UT

D

[

15:

0

]

AD

D

R

[

1

3

:

0]

CS

N

RD

B

_

D

S

B

WR

B

_

RW

B

RDY

B

_

DT

A

C

K

B

BU

SM

OD

E

IN

T

B

MICROPROCESSOR I/F

GPIO REG

GPPI

O[

23:

0

]

TX_PDATA_OUT_[7:0]

TX_PCLK_OUT

RX_PDATA_IN_[7:0]

RX_PCLK_IN

SYS_

R

E

F

C

LK_

O

U

T

RX_LOSEXT

R

X

_

A

LM

_O

U

T

RS

T

B

APS

_

I

N

T

B

1

12

1

12

1

12

DS3/E3

FR

RX_LS_[1:4]_[1:3]_DATA

T

X

_

ASYN

C

_

F

R

M

_

O

U

T

RX_PFRM_IN

RX_LS_[1:4]_[1:3]_CLK

Intrfc

Intrfc

RX_LS_[1:4]_[1:3]_FRM_OUT

PR

OT

_

D

A

T

A_OU

T

PR

OT

_D

A

T

A

_

I

N

PM

PR

OT

_C

L

K

_OU

T

PR

OT

_C

L

K

_I

N

TX_SDATA_OUT

TX_SCLK_OUT

RX_SDATA_IN

RX_SCLK_IN

T

X

_

A

S

Y

NC_

FR

M_

IN

RX_LINE_PRTY

TX_LINE_PRTY

FR/TOH

MON

SEL

INTPRT

STS-1

FR

GEN

DeSynchronization

RX

1

12

R

X

_ST

S

_C

LK_

I

N

SEL

TX_LS_[1:4_][1:3]_DATA

TX_LS_[1:4]_[1:3]_CLK

TX_LS_[1:4]_[1:3]_FRM_IN

FIFO

STS-1

PTR

PROC

STS-1

Dmap

DS3

1

12

DS3/E3

Frame Generator

1

12

DS3

MAP

E3

TX

1

12

DS3/E3

FR

PM

1

12

DS3/E3

DMAP

1

1

Block

AMCC

200 Brickstone Square, Andover, MA 01810 Ph: (978)-623-0009 Fax:(978)-623-0024

STS-12 DS3/E3/STS-1E SONET Mapper

ORINOCO: S1204CBI

Product Specification Revision 1.2

Summary Datasheet Version 1.2 - December 2000

PRELIMINARY SUMMARY DATASHEET

Overview

SONET/SDH Processing

The ORINOCO implements SONET/SDH processing for

STS-12/STM-4 or STS-3/STM-1 data streams. It can

support STS-1 signals within an STS-12 or STS-3, or any

combination of TUG-3/AU-4 or AU-3 signals within an

STM-1 or STM-4. The ORINOCO supports the mapping

of DS3, E3 or STS-1 tributaries into SONET or SDH. For

DS3/E3/STS-1E tributaries, the ORINOCO provides full

framing and performance monitoring.

In the SONET/SDH receive direction, the ORINOCO per-

forms framing, descrambling, and TOH monitoring,

including B1/B2 performance monitoring, serial channel

access to the DCC, User Channel and Orderwire bytes,

and monitoring of the J0, K1K2 (APS, AIS-L and RDI-L

detection), S1 and M1 bytes. While processing the

received pointers, the ORINOCO locates the start of the

embedded SPEs and provides monitoring capabilities for

the POH and pointer bytes.

In the SONET/SDH transmit direction, the ORINOCO

generates the appropriate SPE/VCs containing the input

DS3/E3/STS-1E signals, including generation of path

overhead (with generation of AIS-P and RDI-P). A

SONET/SDH STS-12/STM-4 or STS-3/STM-1 frame is

then created, with its corresponding TOH. The user has

the ability to control the contents of all defined TOH

bytes, including register map control of the K1K2, J0, M1

and S1 bytes, as well as serial channel access to the

DCC, User Channel and Orderwire bytes. The B1 and B2

bytes are automatically generated, as well as AIS-L and

RDI-L indications.

The ORINOCO is SONET and SDH standards compliant

with Bellcore GR-253 and GR-499 and ITU G.707 and

G.783.

DS3/E3 Processing

The ORINOCO provides DS3/E3 mapper and de-mapper

functions. The DS3/E3 mapper accepts data from an

external DS3/E3 input, looped-back DS3/E3 tributaries,

or internal DS3/E3 frame generators. The ORINOCO

provides full DS3/E3 framing and performance monitor-

ing in both transmit and receive directions.

The ORINOCO supports both M23 and C-bit parity DS3

frame formats. It provides the following DS3 mapping

options: DS3/STS-1, DS3/AU-3 and DS3/TUG-3/AU-4.

The ORINOCO supports both the G.751 and G.832 E3

frame formats. It provides the following E3 mapping

options: E3/AU-3 and E3/TUG-3/AU-4.

DS3 monitoring functionality includes support for AIS,

idle, RAI, AIC, FEAC, path parity, FEBE detection/inser-

tion, detection of DS3 frame errors (OOF and SEF), and

DS3 performance monitoring per ANSI T1.231.

E3 monitoring functionality includes detection of REI,

RDI, LOF, AIS, and BIP-4/BIP-8 parity errors, as well as

errored block and errored second indications.

STS-1 Processing

The ORINOCO provides STS-1 mapper and de-mapper

functions. The STS-1 mapper accepts data from external

STS-1E inputs and/or from looped-back STS-1 tributar-

ies. The ORINOCO provides full STS-1 framing,

descrambling, performance monitoring and pointer pro-

cessing in the transmit direction. In the receive direction,

the ORINOCO provides full STS-1 frame generation and

scrambling.

Line Interface

On the line side, the ORINOCO supports an 8-bit parallel

interface which operates at 77.76 MHz for STS-12/STM-

4 applications. In this mode, the device is connected to

the S3037 parallel-to-serial converter (see application

figure below). Optionally, the ORINOCO supports a serial

line interface which operates at 622.08 MHz for STS-12/

STM-4 applications, or at 155.52 MHz or STS-3/STM-1.

In these applications, the device is connected to the

S3024 clock recovery device.

APS Interface

The ORINOCO provides APS input and output interfaces

to convey signals between two S1204 devices configured

for APS operation. This configuration supports both 1+1

and 1:1 configurations. The APS interface consists of

serial clock and data, operating a 622 MHz for STS-12/

STM-4 operation, or 155 MHz for STS-3/STM-1 opera-

tion.

System Interface

The ORINOCO supports up to 12 DS3/E3/STS1 tributar-

ies. In the SONET/SDH Receive direction, the

ORINOCO generates a serial (NRZ) data signal, accom-

panied by a smoothed DS3/E3 clock and a start of frame

indication for each DS3/E3 tributary. For STS-1E tributar-

ies, the ORINOCO provides RX serial (NRZ) data and

clock and frame start signals at 51.84 MHz.

In the SONET/SDH Transmit direction, the ORINOCO

provides two modes of operation. In clear-channel mode,

the ORINOCO accepts a full DS3/E3 signal, payload and

overhead bits, and performs framing on the incoming sig-

nal. The frame start inputs are ignored in this mode of

operation. In DS3 payload only mode, the ORINOCO

accepts the DS3 payload only on the data inputs. The

frame start signal indicates the start of the payload (the

first data bit following the X1 overhead bit). The

ORINOCO maps the DS3 payload data into a full DS3

frame, prior to mapping into a SONET/SDH SPE.

DS3/E3 Desynchronizer

The ORINOCO provides for dense DS3/E3 integration by

performing all functions related to DS3/E3 desynchroni-

zation. The clock smoother consists of a single, off-chip

clock reference together with 12 independent on-chip

digitally controlled modulators, digital filters and fre-

quency detectors. This desynchronizer circuitry provides

jitter and wander compliance to the ANSI T1-105.03-

1994 and ANSI T1-105.03b-1997 specifications.

AMCC

200 Brickstone Square, Andover, MA 01810 Ph: (978)-623-0009 Fax:(978)-623-0024

STS-12 DS3/E3/STS-1E SONET Mapper

ORINOCO: S1204CBI

Product Specification Revision 1.2

Summary Datasheet Version 1.2 - December 2000

PRELIMINARY SUMMARY DATASHEET

Packaging and Power

The ORINOCO is packaged in a ceramic ball grid array

totaling 474 pins (CBGA474). Two power sources, +3.3V

and +2.5V, supplies the I/O and core voltages respec-

tively.

Applications

·

Edge and MultiService Switches

·

Optical Transport Systems

·

WAN Aggregation Terminals

·

SONET/SDH Multiplexers and Digital

Cross Connects

Control

S1204CBI

ORINOCO

Addr

Data

16

12

DS3/E3/STS-1

TX_LS_[1:4][1:3]_DATA

TX_LS_[1:4][1:3]_CLK

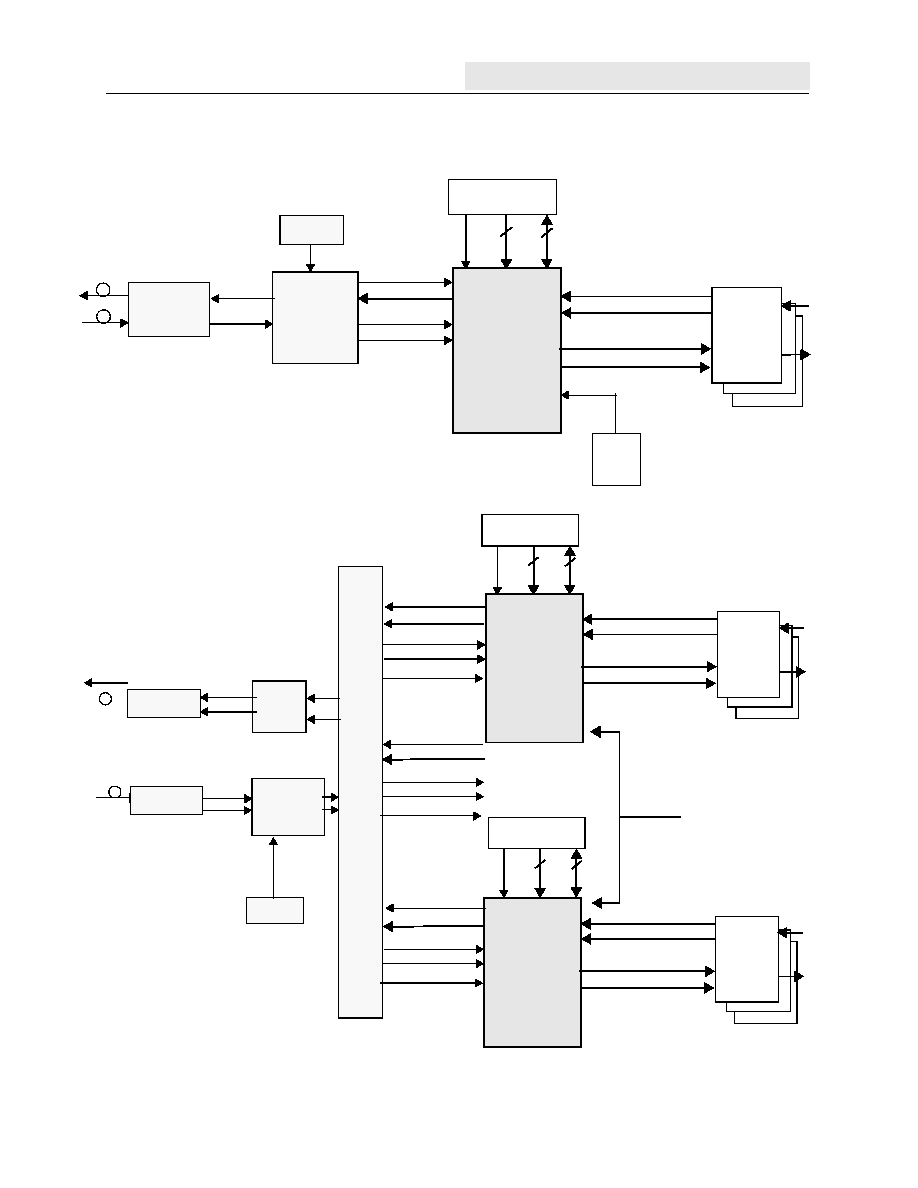

APPLICATION: - Universal DS3 Line Card

DS3/E3/STS-1

LIU

RX_LS_[1:4][1:3]_DATA

RX_LS_[1:4][1:3]_CLK

(up to 12)

Ref Clk

SYS_LS_REFCLK_IN

8-

b

i

t

Microprocessor

Control

Control

S1202CBI

NILE

Addr

Data

8

12

TX_CLK

TX_SYS_DAT[15:0]

RX_CLK

RX_SYS_DAT[15:0]

Utopia Level-2

System Interface

TOH Insertion

and Extraction

ATM Switch

OR

U

T

O

P

I

A

DS3

DS3 Clear Channel for

TX_DS3_[1:12]_DATA

RX_DS3_[1:12]_DATA

RX_DS3_[1:12]_GAP/SM_CLK

RX_DS3_[1:12]_FIFO_[1:0]

TX_DS3_[1:12]_CLK

Packet over SONET Application

Fractional DS3

Channel

HDLC

Processor

IP ROUTER

Switching/

Routing

Logic

Line Interfaces

78

M

h

z

I

n

t

e

rf

ace

Addr

Data

Control

for Multi-Service Applications

TOH Insertion

and Extraction

STS-1

Cross-Connect

- High Density ATM over DS3 Termination

- High Density DS3 Aggregation for Synchronous X-Connects

Transport Line Card

High Density

(OC-12, OC-48, OC-192)

Data Termination

Multi

Support

Interface

622 Mhz

S

3

037

TX_SDATA_OUT±

TX_SCLK_OUT±

RX_SCLK_IN±

RX_SDATA_IN±

622Mhz Clk

SerRxD±

Microprocessor

Control

Control

AMCC S3024

Sumitomo SDM7202

HP HFCT5208

Reference

Clock

Fiber Optic

Transceiver

SONET

Line Side

Interface

RX_LOSEXT

S1204CBI

ORINOCO

Addr

Data

16

12

DS3/E3/STS-1 Line Interfaces

TX_LS_[1:4][1:3]_DATA

TX_LS_[1:4][1:3]_CLK

APPLICATION: OC-12 Aggregation using the

DS3/E3/STS-1

LIU

RX_LS_[1:4][1:3]_DATA

RX_LS_[1:4][1:3]_CLK

(up to 12)

STS-12 Line Interface

Recovery

* Can be replaced by

a backplane driver

Serial 622 Mbit/s Interface

Ref Clk

SYS_REFCLK_IN

AMCC

200 Brickstone Square, Andover, MA 01810 Ph: (978)-623-0009 Fax:(978)-623-0024

STS-12 DS3/E3/STS-1E SONET Mapper

ORINOCO: S1204CBI

Product Specification Revision 1.2

Summary Datasheet Version 1.2 - December 2000

PRELIMINARY SUMMARY DATASHEET

TX_PDATA_OUT[7:0]

TX_PCLK_OUT

RX_PCLK_IN

RX_PDATA_IN[7:0]

SerRxD±

SerTxD±

Microprocessor

Control

Control

AMCC S3045

Reference

Clock

RX_LOSEXT

S1204CBI

ORINOCO

Addr

Data

16

12

DS3/E3/STS-1 Line Interfaces

TX_LS_[1:4][1:3]_DATA

TX_LS_[1:4][1:3]_CLK

APPLICATION: OC-48 Aggregation

DS3/E3/STS-1

LIU

RX_LS_[1:4][1:3]_DATA

RX_LS_[1:4][1:3]_CLK

(up to 12)

OC

-

4

8 Opt

i

cal

I

n

t

e

r

f

a

c

e

TX_PDATA_OUT[7:0]

RX_PCLK_IN

RX_PDATA_IN[7:0]

RX_LOSEXT

S1204CBI

ORINOCO

DS3/E3/STS-1 Line Interfaces

TX_LS_[1:4][1:3]_DATA

TX_LS_[1:4][1:3]_CLK

DS3/E3/STS-1

LIU

RX_LS_[1:4][1:3]_DATA

RX_LS_[1:4][1:3]_CLK

(up to 12)

AMCC S3041

AMCC S3042

Fiber Optic

Receiver

Sumitomo SDT8908-R

Fiber Optic

Receiver

Sumitomo SDT8908-R

Fiber Optic

Fiber Optic

Transmitter

Sumitomo SDT8008-T

TxClk±

RxClk±

S/P

SONET RX

with

Clk Recovery

TX

P/S

SONET

TX_PCLK_OUT

Four(4) Parallel ORINOCOs

TX_PDATA_OUT[7:0]

TX_PCLK_OUT

RX_PCLK_IN

RX_PDATA_IN[7:0]

RX_LOSEXT

Microprocessor

Control

Control

Addr

Data

16

12

STS-4

8

<-

> STS-

12 De/

M

ux

TX_PDATA_OUT[7:0]

TX_PCLK_IN

RX_PCLK_IN

RX_PDATA_IN[7:0]

P/S & S/P

SONET XCVR

with

Clk Recovery

SerRxD±

SerTxD±

Microprocessor

Control

Control

AMCC S3037

Sumitomo SDM7202

HP HFCT5208

Reference

Clock

Fiber Optic

Transceiver

SONET

Line Side

Interface

RX_LOSEXT

S1204CBI

ORINOCO

Addr

Data

16

12

DS3/E3/STS-1 Line Interfaces

TX_LS_[1:4][1:3]_DATA

TX_LS_[1:4][1:3]_CLK

APPLICATION: OC-12 Aggregation using the

DS3/E3/STS-1

LIU

RX_LS_[1:4][1:3]_DATA

RX_LS_[1:4][1:3]_CLK

(up to 12)

STS-12 Line Interface

Ref Clk

SYS_LS_REFCLK_IN

8-bit, 78Mhz Interface