FUNCTIONAL BLOCK DIAGRAM

V

DIGITAL

=

+3V OR +5V

V

ANALOG+

=

+0V TO +5V

OUTPUT

IN+

INş

NOTE: (V

ANALOG+

) ş (V

ANALOGş

)

3V

V

ANALOGş

=

+0V TO ş5V

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

23 ns and 65 ns

Low Voltage Comparators

CMP401/CMP402

ę Analog Devices, Inc., 1995

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

FEATURES

23 ns or 65 ns Propagation Delay

Single-Supply Operation

Compatible with +3 V and +5 V Logic

Separate Input and Output Sections

Low Power

Wide Input Range: ş5 V to +3.9 V

APPLICATIONS

Battery Operated Instrumentation

Line Receivers

Level Translators

Read Channel Detection

GENERAL DESCRIPTION

The CMP401 and CMP402 are 23 ns and 65 ns quad comp-

arators with separate input and output supplies. Separate supplies

enable the input stage to be operated from +3 volts to as high as

▒

6 volts. The output can be supplied with either +3 volts or

+5 volts as determined by the interface logic or available supplies.

Independent input and output supplies combined with fast prop-

agation make the CMP401 and CMP402 excellent choices for

interfacing to portable instrumentation.

The CMP401 and CMP402 are specified over the extended

industrial (ş40

░

C to +125

░

C) temperature range. Both are

available in 16-pin plastic DIP or narrow SO-16 surface mount

packages. Consult factory for 16-lead TSSOP availability.

10

0%

2v

10nS

50mV

100

90

CMP401: 20 MHz Noninverting Switching. V

IN

=

▒

100 mV

ELECTRICAL SPECIFICATIONS

Parameter

Symbol

Conditions

Min

Typ

Max

Units

INPUT CHARACTERISTICS

Offset Voltage

1

V

OS

T

A

= +25

░

C

3

mV

Offset Voltage

1

V

OS

4

mV

Hysteresis

2

mV

Input Bias Current

I

B

T

A

= +25

░

C

3

Á

A

I

B

4

Á

A

Input Offset Current

I

OS

▒

3

Á

A

Input Common-Mode Voltage Range

V

CM

0

+4.0

V

Common-Mode Rejection

CMRR

0.1 V

V

CM

3.9 V

60

dB

Large Signal Voltage Gain

A

VO

R

L

= 10 k

10

V/mV

Offset Voltage Drift

V

OS

/

T

1

Á

V/

░

C

OUTPUT CHARACTERISTICS

Output High Voltage

V

OH

I

OH

= ş3.2 mA

4.6

V

Output Low Voltage

V

OL

I

OL

= 3.2 mA

0.2

V

POWER SUPPLY

Power Supply Rejection Ratio

PSRR

V+

ANA

and V+

DIG

+2.7 V to +6 V

60

dB

Analog Supply Current ş CMP401

I

ANA

T

A

= +25

░

C

6.5

mA

Digital Supply Current ş CMP401

I

DIG

V

O

= 0 V, R

L

=

, T

A

= +25

░

C

2.0

mA

Analog Supply Current ş CMP401

I

ANA

8.0

mA

Digital Supply Current ş CMP401

I

DIG

V

O

= 0 V, R

L

=

2.25

mA

Analog Supply Current ş CMP402

I

ANA

T

A

= +25

░

C

1.4

mA

Digital Supply Current ş CMP402

I

DIG

V

O

= 0 V, R

L

=

, T

A

= +25

░

C

2.0

mA

Analog Supply Current ş CMP402

I

ANA

1.75

mA

Digital Supply Current ş CMP402

I

DIG

V

O

= 0 V, R

L

=

2.25

mA

DYNAMIC PERFORMANCE

Propagation Delay ş CMP401

t

P

100 mV Step with 20 mV OD,

T

A

= +25

░

C

17

23

ns

Propagation Delay ş CMP401

t

P

100 mV Step with 5 mV OD,

T

A

= +25

░

C

33

ns

Propagation Delay ş CMP401

t

P

100 mV Step with 20 mV OD

30

ns

Propagation Delay ş CMP402

t

P

100 mV Step with 20 mV OD,

T

A

= +25

░

C

54

65

ns

Propagation Delay ş CMP402

t

P

100 mV Step with 5 mV OD,

T

A

= +25

░

C

60

ns

Propagation Delay ş CMP402

t

P

100 mV Step with 20 mV OD

75

ns

ELECTRICAL SPECIFICATIONS

Parameter

Symbol

Conditions

Min

Typ

Max

Units

INPUT CHARACTERISTICS

Offset Voltage

1

V

OS

4.5

mV

Input Common-Mode Voltage Range

V

CM

0

+2.0

V

Input Differential Voltage Range

V

DIFF

▒

2.0

V

Common-Mode Rejection

CMRR

0.1 V

V

CM

1.9 V

60

dB

OUTPUT CHARACTERISTICS

Output High Voltage

V

OH

I

OH

= ş3.2 mA

2.6

V

Output Low Voltage

V

OL

I

OL

= 3.2 mA

0.25

V

POWER SUPPLY

Power Supply Rejection Ratio

PSRR

V+

ANA

and V+

DIG

+2.7 V to +6 V

60

dB

Analog Supply Current ş CMP401

I

ANA

6

mA

Digital Supply Current ş CMP401

I

DIG

V

O

= 0 V, R

L

=

1

mA

Analog Supply Current ş CMP402

I

ANA

1.2

mA

Digital Supply Current ş CMP402

I

DIG

V

O

= 0 V, R

L

=

1

mA

DYNAMIC PERFORMANCE

Propagation Delay ş CMP401

t

P

100 mV Step with 20 mV OD

32

ns

Propagation Delay ş CMP402

t

P

100 mV Step with 20 mV OD

70

ns

REV. 0

ş2ş

(@ V+

ANA

= V+

DIG

= +5.0 V, V

CM

= 0.1 V, ş40 C

T

A

+125 C unless otherwise noted)

(@ V

ANA

= V

DIG

= +3.0 V, V

CM

= 0.1 V, T

A

= +25 C unless otherwise noted)

CMP401/CMP402şSPECIFICATIONS

ELECTRICAL SPECIFICATIONS

Parameter

Symbol

Conditions

Min

Typ

Max

Units

INPUT CHARACTERISTICS

Offset Voltage

1

V

OS

V

CM

= 0 V

3

mV

Input Common-Mode Voltage Range

V

CM

ş5.0

+4.0

V

Input Differential Voltage Range

V

DIFF

▒

8.0

V

Common-Mode Rejection

CMRR

ş4.9 V

V

CM

3.9 V

60

dB

Offset Voltage Drift

V

OS

/

T

1

5

Á

V/

░

C

POWER SUPPLY

Power Supply Rejection Ratio

PSRR

V

▒

ANA

▒

3 V to

▒

6 V

60

dB

Analog Supply Current ş CMP401

I

ANA

6.5

mA

Digital Supply Current ş CMP401

I

DIG

V

O

= 0 V, R

L

=

2.0

mA

Analog Supply Current ş CMP402

I

ANA

2.0

mA

Digital Supply Current ş CMP402

I

DIG

V

O

= 0 V, R

L

=

2.0

mA

DYNAMIC PERFORMANCE

Propagation Delay ş CMP401

t

P

100 mV Step with 20 mV OD

23

ns

Propagation Delay ş CMP402

t

P

100 mV Step with 20 mV OD

65

ns

NOTES

1

Offset voltage is defined as (V

OS+

+ V

OSş

)/2.

Specifications subject to change without notice.

REV. 0

ş3ş

(@ V

▒

ANA

=

▒

5 V, V

DIG

= +5.0 V, T

A

= +25 C unless otherwise noted)

CMP401/ CMP402

CMP401/ CMP402

REV. 0

ş4ş

WARNING!

ESD SENSITIVE DEVICE

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the CMP401/CMP402 features proprietary ESD protection circuitry, permanent damage

may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

ABSOLUTE MAXIMUM RATINGS

1

Total Analog Supply Voltage . . . . . . . . . . . . . . . . . . . . . +16 V

Digital Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . +7 V

Analog Positive Supply--Digital Positive Supply . . . . ş200 mV

Input Voltage

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

▒

7 V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . .

▒

9 V

Output Short-Circuit Duration to GND . . . . . . . . . Indefinite

Storage Temperature Range

P, S, RU Package . . . . . . . . . . . . . . . . . . . ş65

░

C to +150

░

C

Operating Temperature Range

CMP401G, CMP402G . . . . . . . . . . . . . . ş40

░

C to +125

░

C

Junction Temperature Range

P, S, RU Package . . . . . . . . . . . . . . . . . . . ş65

░

C to +150

░

C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . +300

░

C

Package Type

JA

3

JC

Units

16-Pin Plastic DIP (P)

90

47

░

C/W

16-Pin SO (S)

113

37

░

C/W

16-Lead TSSOP (RU)

180

37

░

C/W

NOTES

1

Absolute maximum ratings apply to both DICE and packaged parts, unless

otherwise noted.

2

The analog input voltage is equal to

▒

7 volts or the analog supply voltage,

whichever is less.

3

JA

is specified for the worst case conditions, i.e.,

JA

is specified for device in socket

for P-DIP, and

JA

is specified for device soldered in circuit board for SOIC and

TSSOP packages.

ORDERING GUIDE

Temperature

Package

Package

Model

Range

Description

Option

CMP401GP

ş40

░

C to +125

░

C 16-Pin Plastic DIP

N-16

CMP401GS

ş40

░

C to +125

░

C 16-Pin SOIC

R-16A

CMP401GRU

ş40

░

C to +125

░

C 16-Lead TSSOP

RU-16

CMP402GP

ş40

░

C to +125

░

C 16-Pin Plastic DIP

N-16

CMP402GS

ş40

░

C to +125

░

C 16-Pin SOIC

R-16A

CMP402GRU

ş40

░

C to +125

░

C 16-Lead TSSOP

RU-16

DICE CHARACTERISTICS

2

1

16 15

8

9

3

4

5

6

7

14

13

12

11

10

CMP401/CMP402 Die Size 0.065

Î

0.069 inch, 4,485 sq. mils

Substrate (Die Backside) Is Connected to V+

Transistor Count 104.

+IN

şIN

V+ ANA

Vş ANA

V+ DIG

OUT

DIG GND

Figure 1. Simplified Schematic

CMP401/CMP402 PIN CONFIGURATIONS

16-Lead Epoxy DIP

(P Suffix)

16-Lead Narrow-SO

(S Suffix)

16-Lead

TSSOP

(RU Suffix)

OUT B

OUT A

V+ DIG

V+ ANA

şIN A

+IN A

şIN B

+IN B

Vş ANA

DIG GND

OUT D

OUT C

şIN C

+IN D

şIN D

+IN C

1

16

8

9

TOP VIEW

(Not to Scale)

CMP401/

402

14

13

12

11

16

15

10

9

8

1

2

3

4

7

6

5

OUT B

OUT A

V+ DIG

V+ ANA

şIN A

+IN A

şIN B

+IN B

Vş ANA

DIG GND

OUT D

OUT C

şIN C

+IN D

şIN D

+IN C

TOP VIEW

(Not to Scale)

CMP401/

402

14

13

12

11

16

15

10

9

8

1

2

3

4

7

6

5

OUT B

OUT A

V+ DIG

V+ ANA

şIN A

+IN A

şIN B

+IN B

Vş ANA

DIG GND

OUT D

OUT C

şIN C

+IN D

şIN D

+IN C

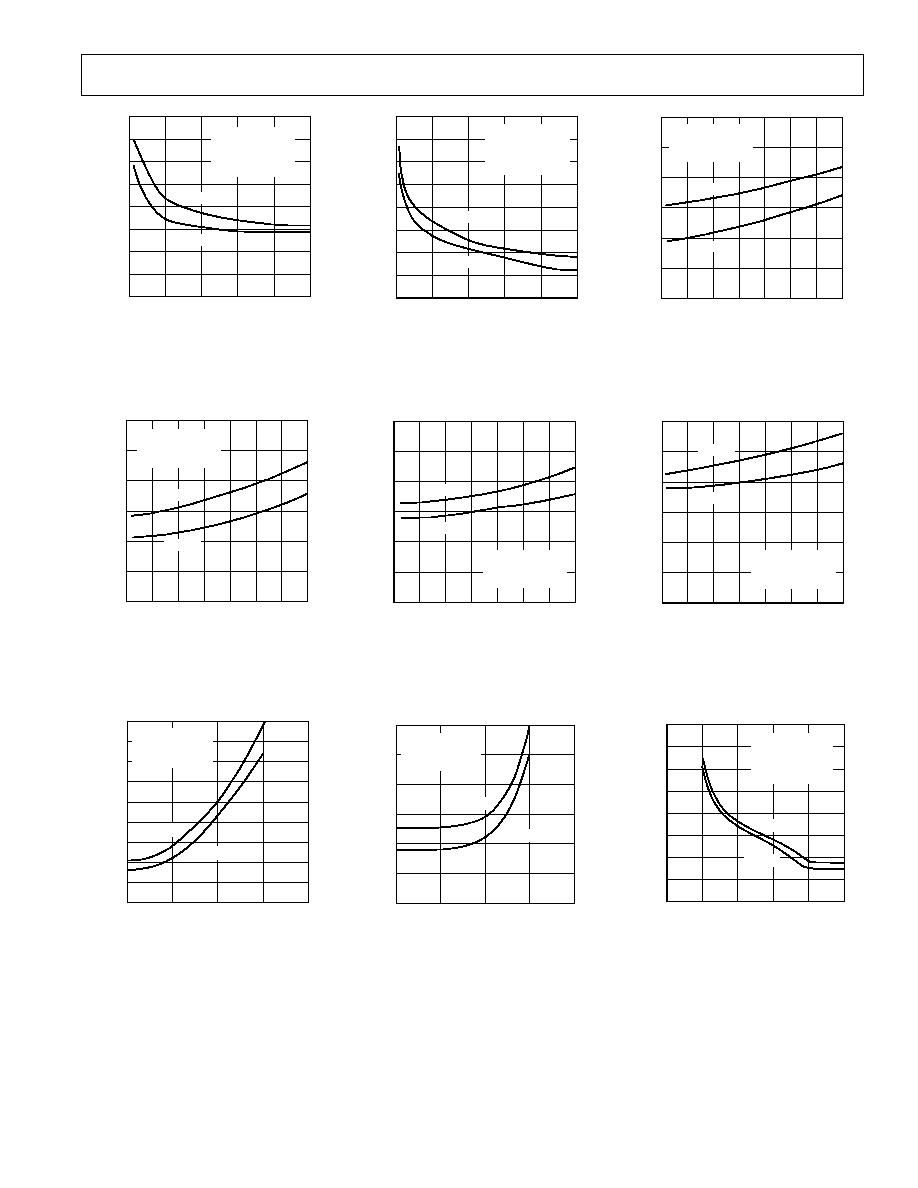

Typical Performance CharacteristicsşCMP401/ CMP402

REV. 0

ş5ş

OVERDRIVE ş mV

PROPAGATION DELAY ş ns

40

35

0

0

10

50

20

30

40

20

15

10

5

30

25

+P

DELAY

şP

DELAY

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

T

A

= +25

░

C

Figure 2. CMP401 Propagation Delay

vs. Overdrive

TEMPERATURE ş

░

C

PROPAGATION DELAY ş ns

90

30

ş50

ş25

125

0

25

50

75

100

80

70

60

50

40

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

+P

DELAY

şP

DELAY

Figure 5. CMP402 Propagation Delay

vs. Temperature ş 5 mV OD

SOURCE RESISTANCE ş

90

80

0

10

100

100k

1k

10k

40

30

20

10

70

60

50

PROPAGATION DELAY ş ns

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

T

A

= +25

░

C

+P

DELAY

şP

DELAY

Figure 8. CMP401 Propagation Delay

vs. Source Resistance ş 20 mV OD

OVERDRIVE ş mV

PROPAGATION DELAY ş ns

110

90

20

0

10

50

20

30

40

60

50

40

30

80

70

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

T

A

= +25

░

C

+P

DELAY

şP

DELAY

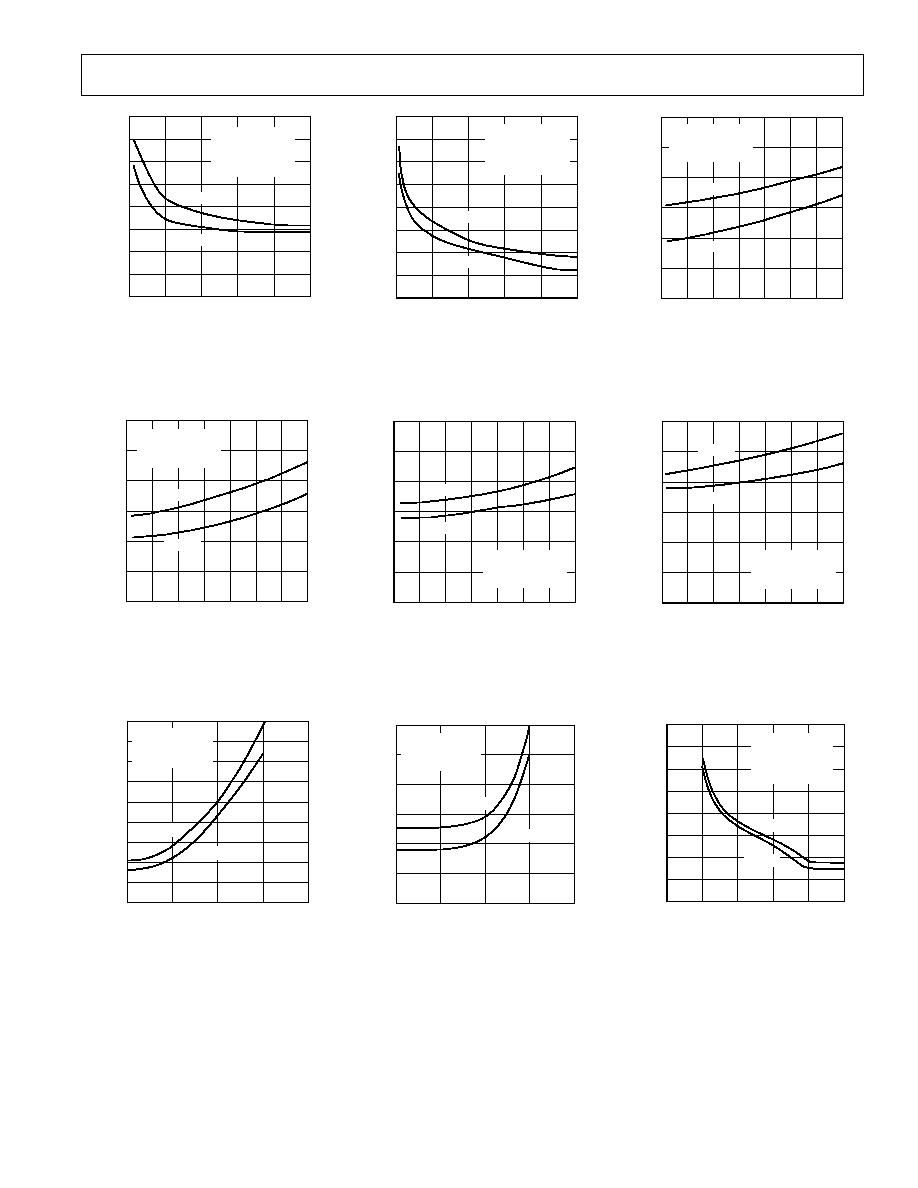

Figure 3. CMP402 Propagation Delay

vs. Overdrive

TEMPERATURE ş

░

C

PROPAGATION DELAY ş ns

30

0

ş50

ş25

125

0

25

50

75

100

25

20

15

10

5

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

+P

DELAY

şP

DELAY

Figure 6. CMP401 Propagation Delay

vs. Temperature ş 20 mV OD

SOURCE RESISTANCE ş

PROPAGATION DELAY ş ns

120

100

0

10

100

100k

1k

10k

80

60

40

20

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

T

A

= +25

░

C

+P

DELAY

şP

DELAY

Figure 9. CMP402 Propagation Delay

vs. Source Resistance ş 20 mV OD

TEMPERATURE ş

░

C

PROPAGATION DELAY ş ns

40

10

ş50

ş25

125

0

25

50

75

100

35

30

25

20

15

+P

DELAY

şP

DELAY

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

Figure 4. CMP401 Propagation Delay

vs. Temperature ş 5 mV OD

TEMPERATURE ş

░

C

PROPAGATION DELAY ş ns

60

0

ş50

ş25

125

0

25

50

75

100

50

40

30

20

10

+V

AN

= +V

DIG

= +5V

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

+P

DELAY

şP

DELAY

Figure 7. CMP402 Propagation Delay

vs. Temperature ş 20 mV OD

POSITIVE SUPPLY VOLTAGE ş Volts

PROPAGATION DELAY ş ns

80

70

0

0

2

6

3

4

5

40

30

20

10

60

50

+V

AN

= +V

DIG

şV

AN

= 0V TO ş5V

R

S

50

, C

L

= 15pF

T

A

= +25

░

C

+P

DELAY

şP

DELAY

Figure 10. CMP401 Propagation Delay

vs. Supply Voltage ş 20 mV OD